лельно включенных МОП-транзисторов дополнительного логического элемента НЕ- ИЛИ, затвор другого параллельно включенного МОП-транзистора этого логического элемента соединен со стоком второго МОПтранзистора логического элемента НЕ- ИЛИ, затвор которого соединен со стоком третьего МОП-транзистора дополнительного логического элемента НЕ-ИЛИ, при этом затвор третьего МОП-транзистора дополнительного логического элемента НЕ- ИЛИ соединен с четвертой входной шииой.

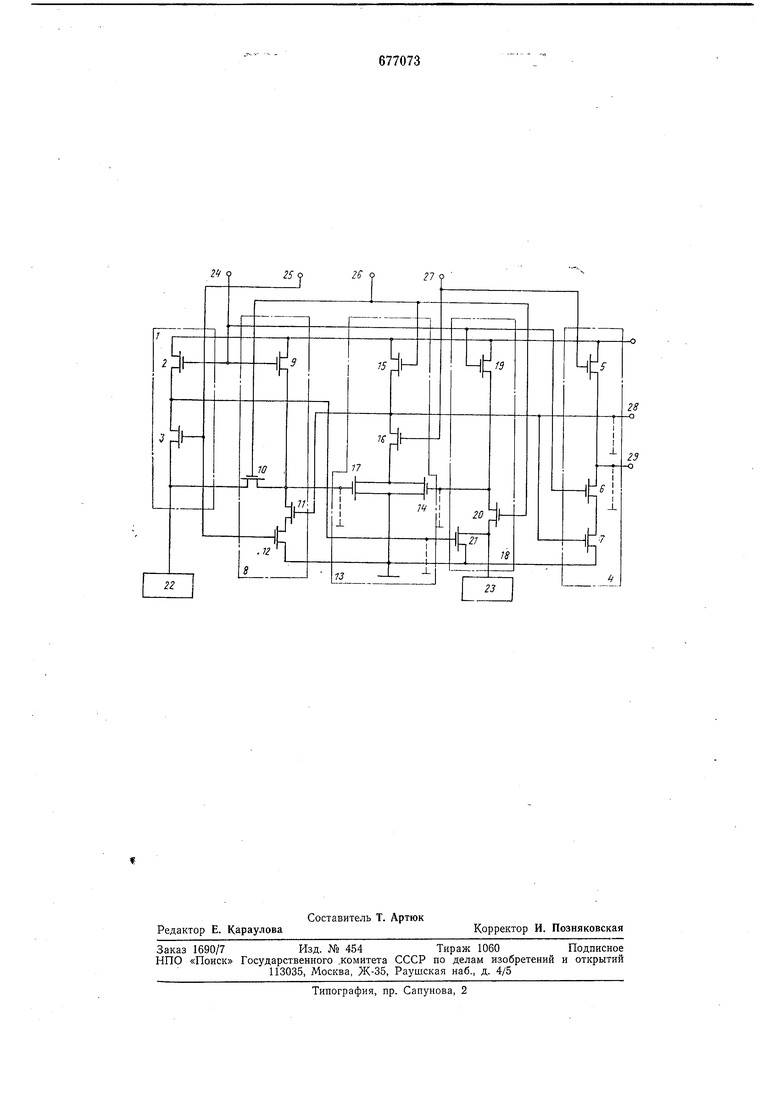

На чертеже приведена принципиальная электрическая схема предлагаемого Д-триггера.

Д-Триггер содержит логический элемент НЕ 1, вьшолненный на МОП-транзисторах 2, 3, второй логический элемент НЕ 4, выполненный на МОП-транзисторах 5-7, логический элемент НЕ-ИЛИ 8, выполненный на МОП-транзисторах 9-12, второй логический элемент НЕ-ИЛИ 13, выполненный на МОП-транзисторах 14-17, логический элемент ЗНЕ-ИЛР1 18, выполненный на МОП-транзисторах 19-21, элементы управления 22, 23.

На входнь;е шины 24-27 поданы соответствующие входные сигналы.

Выходные сигналы снимаются соответственно с выходов 28, 29.

Принцип работы триггера заключается в следующем.

Пусть в исходном состоянии выход 28 имеет потенциал, близкий к потенциалу «Земля, выход 29 имеет потенциал, близкий к потенциалу источника питания, элементы управления 22, 23, работающие в ключевом , разомкнуты, что соответствует логическому «О. Следовательно, истоки МОП-транзисторов 3, 10, 20 не заземлены.

При цоступлении на входную шину 24 сигнала фазы fj МОП-транзисторы 2, 9, 19 открываются. Входные емкости МОП-транзисторов 17, 21, 14 зарядятся приблизительно до потенциала источника питания.

. При поступлении сигнала фазы /2 на входную шину 25 МОП-траизистор 3 будет закрыт, так как не возбужден элемент управления 22, что соответствует логическому «О, и, следовательно, исток МОП-транзистора 3 не замкнут на «Землю.

Таким образом, по окончании импульса f2 входная емкость МОП-транзистора 21 сохраняет потенциал, приблизительно равный потенциалу источника питания.

При поступлении сигнала fa на затвор МОП-транзистора 12 последний не открывается, так как закрыт последовательно соединенный с ним МОП-транзистор 11 (на затворе потенциал, приблизительно равный потенциалу «Земля). Входная емкость МОП-транзистора 17 не изменит своего состояния нотен11,иала, приблизительно равного потенциалу источника питания, после окончания сигнала /2При поступлении фазового импульса /з на входную шину 26 МОП-транзистор 10 не 5 открывается, так как не возбужден элемент управления 22, что соответствует логическому «О, и исток МОП-транзистора 10 не замкнут на «Землю. Следовательно, емкость МОП-транзистора 17 не разрядится. 10 Фазовым имнуль сом fz открывается МОПтраизистор 15 и емкость МОП-транзистора 7 заряжается до потенциала источника питания.

При поступлении сигнала /з на затвор 15 МОП-транзистора 20 последний открывается, так как открыт последовательно соединенный с ним МОП-транзистор 21 (на затворе потенциал источника питания), и емкость МОП-транзистора 14 разряжается до 20 потенциала, приблизительно равного потенциалу «Земля.

На входную шину 27 поступает сигнал фазы /4- При его поступлении на затвор МОП-транзистора 16 последний открывается, так как открыт последовательно соединенный с ним МОП-транзистор 17 (на затворе потенциал, приблизительно равный потенциалу источника питания).

Емкость МОП-транзистора 7 разряжается 0 через МОП-транзисторы 16 и 17 до потенциала, приблизительно равного потенциалу «Земля.

При поступлении сигнала /4 на затвор МОП-транзистора 5 МОП-транзистор от5 крывается, и его выходная емкость заряжается до потенциала, нриблизительио равного потенциалу источника питания.

По сигналу фазы /i, поступающему на входную шину 24 и на затвор транзистора ; 6, МОП-транзистор не открывается, так как закрыт носледовательно соединенный с ним МОП-транзистор 7 (на затворе потенциал, нриблизительно равный потенциалу «Земля). Следовательно, выходная емкость со5 храняет после окончания сигнала fi свое состояние (нотенциал, приблизительно равный потенциалу «Земля). По сигналу фазы /1 емкости МОП-транзисторов 9, 19 и 2 зарядятся до потенциала, приблизительно Q равного потенциалу источника питания. Таким образом, при невозбужденных элементах управления 22, 23, что соответствует логическому «О, после прохождения сигналов фаз f 1 - /4 триггер сохраняет свое со5 стояние.

Допустим, элементы управления 22, 23 возбуждены, что соответствует логической «I. Сигнал фазы /2 поступает на входную шину 25. При поступлении сигнала /2 на затвор МОП-транзистора 3 последний открывается, так как возбужден элемент управления 22, что соответствует логической «1, и исток МОП-транзистора 3 замкнут через него на «Землю. Емкость МОП-транзистора 21 разрядится до потенциала, приблизительно равного потенциалу , через МОП-транзистор 3 и элемент управления 22.

При поступлении сигнала /2 на затвор МОП-транзистора 12 он не открывается, так как закрыт последовательно соединенный с ним МОП-транзистор 11 (на затворе потенциал, приблизительно равный потенциалу «Земля), и емкость МОП-транзистора И сохраняет свое состояние.

На входную шину 26 поступает сигнал фазы /3. При поступлении этого сигнала на затвор МОП-транзистора 10 последний открывается, так как возбужден элемент управления 22 и исток МОП-транзистора 10 замкнут через него на «Землю.

Емкость МОП-транзистора 17 разрядится до потенциала, приблизительно равного потенциалу «Земля. МОП-транзистор 15 откроется при поступлении сигнала fs и емкость МОП-транзистора 7 зарядится приблизительно до потенциала источника питания.

МОП-транзистор 20 откроется при поступлении на его затвор сигнала fs, так как исток МОП-транзистора 20 замкнут на «Землю через возбужденный элемент управления 23.

Емкость МОП-транзистора 18 разрядится приблизительно до потенциала «Земля.

При поступлении сигнала /4 на входную шину 27 МОП-транзистор 16 не откроется, так как закрыты носледовательно соединенные с ним МОП-транзисторы 14 и 17 (на затворах МОП-транзисторов потенциал, приблизительно равный потенциалу «Земля).

Па выходе 28 сохраняют потенциал, приблизительно равный потенциалу источника питания. При поступлении сигнала /4 на затвор МОП-транзистора 5 последний откроется и выходная емкость зарядится приблизительно до потенциала источника питания.

При поступлении сигнала fi на входную шину 24 откроются МОП-транзисторы 2, 9, 19 и зарядятся приблизительно до потенциала источника питания емкости МОПтранзисторов 17, 14, 21.

При поступлении сигнала fi на затвор МОП-транзистора 6 последний открывается, так как открыт последовательно соединенный с ним МОП-транзистор 7 (на затворе потенциал, приблизительно равный потенциалу источника питания). Следовательно, выходная емкость разрядится через МОП-транзисторы 6 и 17 и выход 29 будет иметь потенциал, приблизительно равный потенциалу «Земля.

Таким образом, после серии фазируюш,их импульсов /1-/4 триггер изм.енил свое состояние на противоположное.

677073

Формула изобретения

Д-Триггер, содержащий логический элемент НЕ на двух последовательно включенных МОП-транзисторах, затворы которых соединенй с двумя входными шинами, логический элемент НЕ-ИЛИ, состояш;ий из трех последовательно включенных МОПтранзисторов, затвор первого из которых

соединен с первой входной шиной, а затвор третьего - с второй входной шиной, и четвертого МОП-транзистора, включенного между истоками второго МОП-транзистора логического элемента НЕ и первого

МОП-транзистора упомянутого логического элемента НЕ-ИЛИ, причем затвор четвертого МОП-транзистора соединен с третьей входной шиной; второй логический элемент НЕ, состоящий из трех последовательно соединенных МОП-транзисторов, затвор первого из которых соединен с четвертой входной шиной, а затвор второго МОП-транзистора соединен с первой входной шиной, отличающийся тем, что, с целью повышения быстродействия, в него введены дополнительный логический элемент НЕ- ИЛИ, состоящий из четырех МОП-транзизисторов, два из которых соединены параллельно и включены последовательно с остальными двумя, и логический элемент ЗНЕ-ИЛИ, состоящий из трех последовательно включенных МОП-транзисторов, затвор первого из которых соединен с первой входной щиной, затвор второго соединен с

затвором Четвертого МОП-транзистора дополнительного логического элемента НЕ- ИЛИ и третьей входной шиной, а затвор третьего МОП-транзистора логического элемента ЗНЕ-ИЛИ соединен с истоком первого МОП-транзистора первого логического элемента НЕ, к истоку второго МОП-транзистора которого подключен первый упомянутый элемент управления, второй элемент управления соединен с истоком второго

МОП-транзистора логического элемента ЗНЕ-ИЛИ, сток которого подключен к затвору одного из параллельно включенных МОП-транзисторов дополнительного логического элемента НЕ-ИЛИ, затвор другого параллельно включенного МОП-транзистора этого логического элемента соединен со стоком второго МОП-транзистора логического элемента НЕ-ИЛИ, затвор которого соединен со стоком третьего МОП-транзистора дополнительного логического элемента НЕ-ИЛИ, при этом затвор третьего МОП-транзистора дополнительного логического элемента НЕ-ИЛИ соединен с четвертой входной щиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

| Устройство для выборки адресов из блоков памяти | 1976 |

|

SU744722A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU858110A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| ВСЕСОЮЗНАЯ ""}iATZh'TuD-- РТНГгч^Ргуде'^'^^КАЯ_ б::блио-|-е.на МБ АВ. А. Косинский, Ю. К. Судьин и А. П. Евдокимов | 1973 |

|

SU370712A1 |

| Накопитель постоянного запоминающего устройства с электрической записью информции | 1973 |

|

SU466552A1 |

| Многовходовый многозначный логический элемент минимум | 1983 |

|

SU1126171A1 |

| Многовходовый многозначный логический элемент максимум | 1983 |

|

SU1126172A1 |

| Ключ | 1975 |

|

SU531278A1 |

| Постоянное запоминающее устройство | 1973 |

|

SU444246A1 |

Авторы

Даты

1979-07-30—Публикация

1971-08-24—Подача