(54) ЦИФРОВОЙ ИМПУЛЬСНЫЙ. ФАЗОВЫЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНХРОННО-СИНФАЗНЫЙ ЭЛЕКТРОПРИВОД | 2011 |

|

RU2485665C1 |

| Дискриминатор временного сдвигадВуХ КОгЕРЕНТНыХ СлучАйНыХ СигНАлОВ | 1979 |

|

SU807314A1 |

| Частотно-фазовый дискриминатор | 2018 |

|

RU2695986C1 |

| Телевизионное устройство для поиска и слежения за двумя источниками излучения | 1981 |

|

SU985973A2 |

| ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР | 2010 |

|

RU2428785C1 |

| СИНХРОННО-СИНФАЗНЫЙ ЭЛЕКТРОПРИВОД | 2010 |

|

RU2422978C1 |

| Преобразователь фаза-код | 1980 |

|

SU960656A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2006 |

|

RU2309430C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| СИНХРОННО-СИНФАЗНЫЙ ЭЛЕКТРОПРИВОД | 2006 |

|

RU2310971C1 |

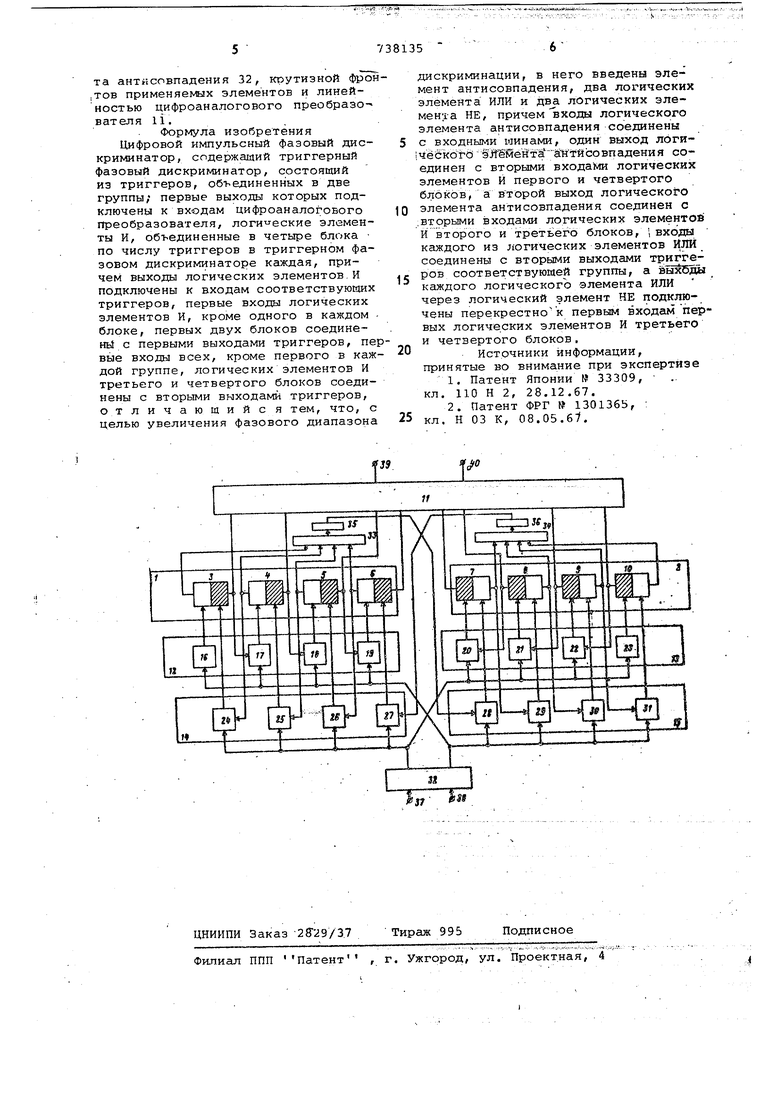

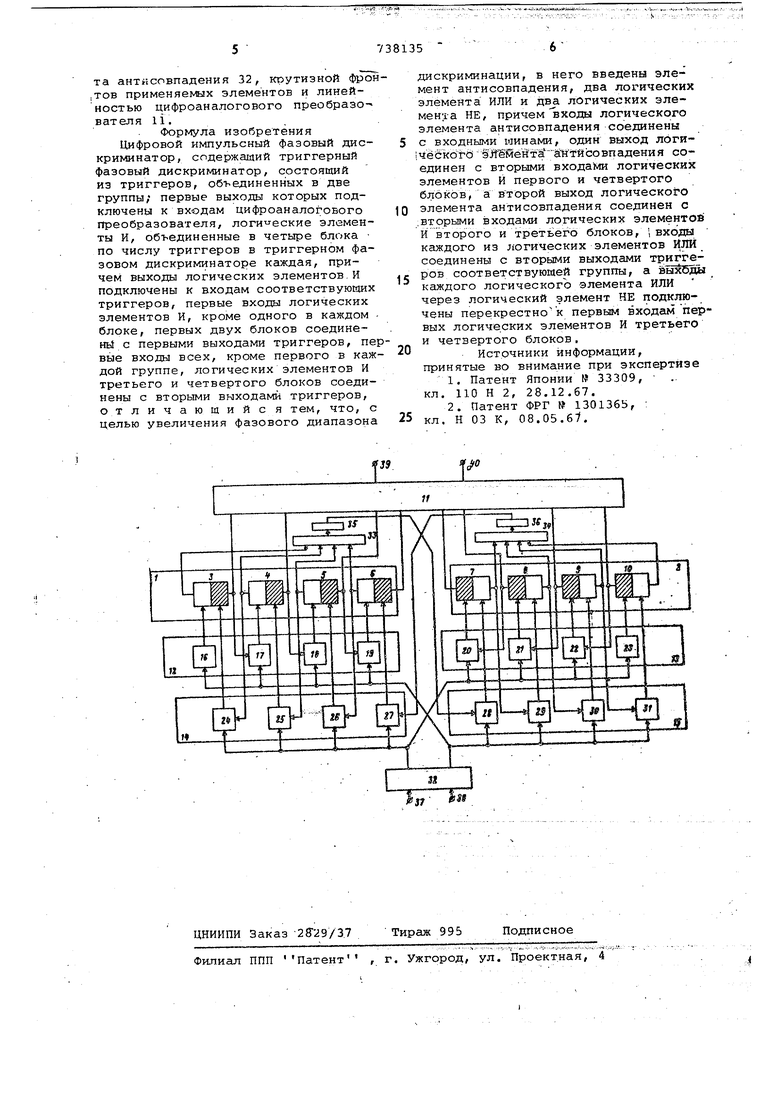

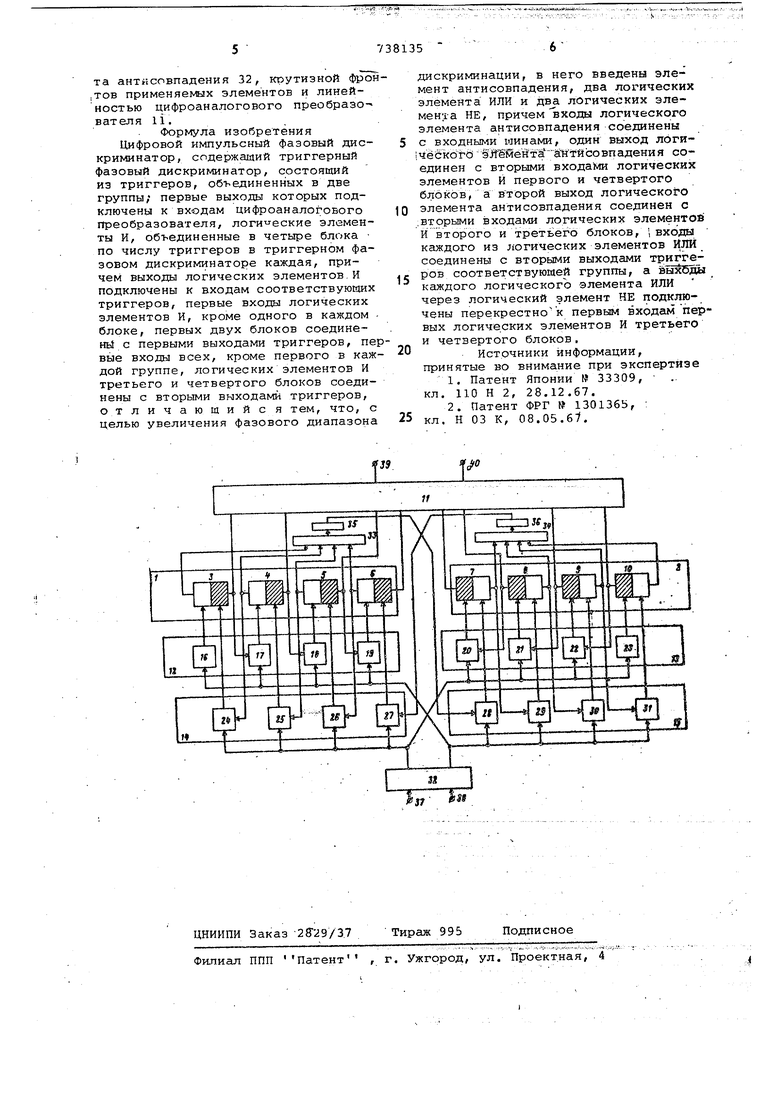

Изобретение относится к импульсной технике. Известен цифровой импульсно-фазовый дискриминатор, содержащий два канала, каждый из которых содержит счетчик импульсов,триггер, трехвходовый логический элемент И, блок индикации и логическую схему 1. Такой дискриминатор И1йеёт малый диапазон. Наиболее близким по технической сущности к предлагаемому является цифровой импульсно-фазовый дискриминатор, содержащий триггерный фазовый дискриминатор, состоящий из триггеров, об-ьединенных в две группы первые выходы которых подключены к входам цифро-аналогового преобразова теля, логические элементы И, объединенные в четыре блока по числу триггеров 5 триггерном фазовом дискриминаторе каждая, причем выходы логических элементов И подключены к входам соответствующих триггеров, первые входы всех логических элементов И, кроме одного в каждом блоке, пер вых двгух блоков соединен с первыми .выходё ми триггеров, первые входы ло гических элементов И третьей и четвертой групп, кроме первого в каждо группе, соединен с вторыми выходами триггеров 2. Данный дискриминатор не обеспечивает необходимого фазового диапазона. Целью изобретения является раа-трение фазового диапазона дискриминации. . Это достигается тем, что в фазовый дискриминатор, содержащий триггерный фазовый дискриминатор, состоящий из триггеров, объединенных в две группы, первые выхода которых подключены к входам цифро-аналогового преобразователя, логические элементы И,объединенные в четыре блока по числу триггеров в триггерном фазовом дискриминаторе каждая, причем выходы логических элементов И подключены к входам соответствующих триггеров, первые входы всех логических элементов И, кроме одного в каждом блоке, первых двух блоков соединены с первыми выходами триггеров, первые входы логических элементов И третьей и четвертой групп, кро- ме первого в каждой группе, соединены с ёторымйвыходами триггеров, введены логический элемент: антисовпадения, два логических элемента ИЛИ и два логических элемента НЕ, причем входы ; логического элемеАта антисовпаде.ния, .соединены d входными шинами, одни tio ход логического элемента антисовпад ния соединен с вторыми входгили логи ческих элементов И первого и четвер того блоков,а второй выход логическ го элемента йнтисовпадения соединен вторыми входами логических элементо И .рторого и третьего блоков, входы каждого из логических элементов ИЛИ соединены с вторыми выхояаыя три:- геров соответствующей группы, а выходы каждого логического ИЛИ через логический элемент НЕ под ключены перекрестно к первым входам первых логических элементов И треть его и четвертого блоков. На чертеже приведена структурная электрическая схема предлагаемого фазового дискриминатора. Цифровой импульсный фазовый дискриминатор содержит фазовый триггер ный дискриминатор из двух групп 1,2 состоящих соответственно из триггеров , цифроаналоговый преобразо ватель 11, блоки 12-15 логических элементов И 16-31, логический элемент антисовпадения 32, логические элементы ИЛИ 33, 34, логические эле менты НЕ 35, 36. Входной сигнал под на входные шины 37, 38. Выходной сиг нал снимается с вк1ходов 39, 40. Дискриминатор работает следующим образом. При нулевом положении всех триггеров 3-10 в группах 1, 2 триггерного фазового дискриминатора потенциала на выходе цифроаналогового преобразователя 11 также равны нулю и ток в нагрузке дискриминатора отсутствует; таким образом, исходная точка выходной характеристики устройства проходит через начало координат. Поступающие на входы логического элемента антисовпадения 32 импульсы подвергаются фазовой селекции, в результате которой совпадающие по фазе импульсы не проходят на вторые входы блоков 12-15 логических элементов И и состояние схемы не изменяется. Запись информации в группы 1, 2, триггеров триггерного фазового дискриминатора осуществляется импульсами с блоков 14, 15 элементов И последовательно, начиная с первого триггера в каждой группе (1 или 2), которому соответствует первый логический элемент И блоков 14, 15, первым входом соединенный с выходом соот1ветствующего логического элемента НЕ 35, 36. После записи логической Ч . в любую из групп 1, 2 триг геров запись, в другую группу триггеров блокируется сигналом логичесс выходов логических элементов НЕ группы 1 или 2, в которую осуществлена за:пись. логической 1 Запись в другую группу тригге«рв становится возможной лишь после возвращения всех триггеров группы в нулевое положение, что осуществляется импульсами с блоков 12, 13 логических элементов И. Таким образом, работа триггеров групп 1, 2 происходит последовательно в соответствии со знаком фазового рассогласования. Также последовательно происходит запись 1 и внутри групп 1, 2 триггеров. Последовательная установка триа:- г-еров групп 1, 2 В положение логической 1 приводит к линейному изменению тока в нагрузке (не показана) цифрЬаналогового преобразователя 11 до тех пор, пока все триггеры соответствующей группы не окажутся в положении . Дальнейшее поступление импульсов на тот же вход устройства изменить состояния схемы не может,и выходная характеристика дискриминатора с этого момента имеет вид типа ограничение. Так как периоду следования импульсов соответствует 2ТХ-радиан, то линейный фазовый диапазон дискриминации предлагаемого дискриминатора составляет ±2Дп радиан (п - число импульсов заполнения групп триггеров фазового дискриминатора) . При поочередном поступлении импульсов на входные шины триггеры групп 1, 2 будут поочередно, начиная с первых, работать в режиме установка 1 - установка О. При этом через нагрузку цифроаналогогового преобразователя 11 будут протекать импульсы тока, ширина которых пропорциональна фазовому рассогласованию, а с учетом постоянства их амплитуды С1реднее значение процесса также будет пропорционально фазовому рассогласованию. Если разность фаз между импульсами на входах дискриминатора становится больше 2 Д радиан, т.е. периода следования, то соответстьующий триггер группы 1 или 2 (в зависимости от знака фазового рассогласования) остается в положении ЛО а последующий начигическойнает работать, выделяя фазовое рассогласование за вычетом 2 Jc радиан. Предыдугаий триггер при этом является по существу элементом памяти, к содержимому которого добавляется среднее значение широтно-модулированного импульса последующего триггера. Таким образом, к концу линейного участка 1сарактеристики элемейтарного триггерно-фазового дискриминатора, представляющего собой триггер группы 1 или 2, примыкает начальный участок характеристики последугогоего элементарного триггерного фазового дискриминатора и т.д. В целом устройство работоспособно в широком диапазоне частот, РазрешЪетаая способность его определяется чувствител|)Ностью логического элемента антисовпадения 32, крутизной фро.тов применяемых элементов и линейностью цифроаналогового преобразователя li.

Формула изобретения Цифровой импульсный фазовый дискриминатор, содержащий триггерный фазовый дискриминатор, состоящий из триггеров, объединенных в две группы; первые выходы которых подключены к входам цифроаналогоБого Преобразователя, логические элементы И, объединенные в четыре блока по числу триггеров в триггерном фазовом дискриминаторе каждая, причем выходы логических элементов.И подключены к входам соответствующих триггеров, первые входы логических элементов И, кроме одного в каждом блоке, первых двух блоков соединень1 с первыми выходами триггеров, певые входы всех, кроме первого в каждой группе, логических элементов И третьего и четвертого блоков соединены с вторыми выходами триггеров, отличающийс я тем, что, с целью увеличения фазового диапазона

дискриминации, в него введены элемент антисовпадения, два логических элемента ИЛИ и логических элемента НЕ, причем входы логического элемента антисовпадения соединены с входными минами, один выход логи чё ёкоtd ЭЙШён со вп ад ени я со единен с вторыми входа)«1и логических элементов И первого и четвертого блоков, а второй выход логического

0 элемента антисовпадения соединен с ;вторыми входами логических элементов И второго и третьего блоков, iвходы каждого из логических элементов ИЛИ соединены с вторыми выходами триггеC ров соответствующей группы, а каждого логического элемента ИЛИ через логический элемент НЕ подключены перекрестно к первым входам первых логических элементов И третьего и четвертого блоков.

0

Источники информации, принятые во внимание при экспертизе

5 кл. Н 03 К, 08.05.6.

Авторы

Даты

1980-05-30—Публикация

1973-04-18—Подача