Изобретение относится к области автоматики и вычислительной техники и может быть использована в качестве логического элемента сравнения частоты следования импульсов задающего генератора, определяющего частоту вращения двигателя в дискретных астатических электроприводах, и частоты следования импульсов датчика обратной связи, расположенного на валу двигателя, а также в других системах фазовой синхронизации.

Известен частотно-фазовый дискриминатор (Патент RU №2428785, МПК H03D 13/00, опубл. 10.09.2011г.), содержащий блок фазового сравнения, первый и второй входы которого являются соответственно первым и вторым входами частотно-фазового дискриминатора, а первый и второй выходы подключены соответственно ко второму и четвертому входам блока логической блокировки, выход которого является первым выходом частотно-фазового дискриминатора, а также первый и второй блокирующие триггеры, выходы которых соединены соответственно с первым и третьим входами блока логической блокировки, при этом информационные входы первого и второго блокирующих триггеров подсоединены соответственно к первому и второму выходам логического устройства, а тактовые входы - ко второму входу блока фазового сравнения, первый и второй входы логического устройства соединены соответственно с первым и вторым выходами блока фазового сравнения, а третий и четвертый входы - с выходами соответственно первого и второго блокирующих триггеров, тактовый вход первого счетчика импульсов подключен ко второму входу блока фазового сравнения, а вход сброса является третьим входом частотно-фазового дискриминатора, выходы первого счетчика импульсов подключены к информационным входам второго счетчика импульсов, тактовый вход которого является четвертым входом частотно-фазового дискриминатора, а выход - вторым выходом дискриминатора, кроме того первый и второй входы дешифратора подключены соответственно к первому и второму выходам блока фазового сравнения, первый выход дешифратора подключен к информационному входу третьего триггера, тактовый вход которого соединен со вторым входом блока фазового сравнения, выход третьего триггера подключен к первому входу первого цифрового ключа, второй вход которого соединен со вторым входом блока фазового сравнения, выход первого цифрового ключа подключен к входу суммирования импульсов второго счетчика импульсов, вход вычитания импульсов которого подключен к выходу второго цифрового ключа, первый вход которого подключен к третьему выходу дешифратора, а второй вход - к первому входу блока фазового сравнения.

Недостатком такого устройства являются узкие функциональные возможности, не позволяющие комплексно его использовать в синхронно-синфазном электроприводе для определения как фазовой ошибки импульсов сравниваемых частот и угловой ошибки электропривода, так и ошибки по угловой скорости в режимах насыщения дискриминатора.

Наиболее близким техническим решением к заявляемому устройству является частотно-фазовый дискриминатор (Патент RU 134375 опубл. 10.11.2013г.), содержащий блок фазового сравнения, первый и второй входы которого являются соответственно первым и вторым входами частотно-фазового дискриминатора, а первый и второй выходы подключены соответственно ко второму и четвертому входам блока логической блокировки, выход которого является первым выходом частотно-фазового дискриминатора, а также первый и второй блокирующие триггеры, выходы которых соединены соответственно с первым и третьим входами блока логической блокировки, при этом информационные входы первого и второго блокирующих триггеров подсоединены соответственно к первому и второму выходам логического устройства, а тактовые входы - ко второму входу блока фазового сравнения, первый и второй входы логического устройства соединены соответственно с первым и вторым выходами блока фазового сравнения, а третий и четвертый входы - с выходами соответственно первого и второго блокирующих триггеров, тактовый вход первого счетчика импульсов подключен ко второму входу блока фазового сравнения, а вход сброса является третьим входом частотно-фазового дискриминатора, выходы первого счетчика импульсов подключены к информационным входам второго счетчика импульсов, тактовый вход которого является четвертым входом частотно-фазового дискриминатора, а выход - вторым выходом дискриминатора, кроме того, первый и второй входы дешифратора подключены соответственно к первому и второму выходам блока фазового сравнения, первый выход дешифратора подключен к информационному входу третьего триггера, тактовый вход которого соединен со вторым входом блока фазового сравнения, выход третьего триггера подключен к первому входу первого цифрового ключа, второй вход которого соединен со вторым входом блока фазового сравнения, выход первого цифрового ключа подключен к входу суммирования импульсов второго счетчика импульсов, вход вычитания импульсов которого подключен к выходу второго цифрового ключа, первый вход которого подключен к третьему выходу дешифратора, а второй вход - к первому входу блока фазового сравнения, первый вход логического элемента ИЛИ соединен с выходом первого цифрового ключа, второй вход элемента ИЛИ соединен с выходом второго цифрового ключа, тактовый вход третьего счетчика импульсов соединен со вторым входом блока фазового сравнения и входом преобразователя "частота - код", вход сброса третьего счетчика импульсов соединен с выходом элемента ИЛИ и тактовым входом регистра, выходы третьего счетчика импульсов подключены к информационному входу регистра, выходы регистра подключены к первым входам вычислительного устройства, выходы преобразователя "частота-код" подключены ко вторым входам вычислительного устройства, а выход вычислительного устройства является третьим выходом частотно-фазового дискриминатора.

Недостатком данного устройства является невысокая точность определения частотного рассогласования и узкий диапазон работы.

Техническим результатом изобретения является расширение диапазона измерения частотного рассогласования сравниваемых сигналов.

Данный технический результат достигается тем, что в известный частотно-фазовый дискриминатор, содержащий первый блок фазового сравнения, первый вход которого является первым входом частотно-фазового дискриминатора, а первый и второй выходы подключены соответственно ко второму и четвертому входам блока логической блокировки, выход которого является первым выходом частотно-фазового дискриминатора, а также первый и второй блокирующие триггеры, выходы которых соединены соответственно с первым и третьим входами блока логической блокировки, при этом информационные входы первого и второго блокирующих триггеров подсоединены соответственно к первому и второму выходам логического устройства, первый и второй входы логического устройства соединены соответственно с первым и вторым выходами первого блока фазового сравнения, а третий и четвертый входы - с выходами соответственно первого и второго блокирующих триггеров, кроме того, первый выход дешифратора подключен к информационному входу третьего триггера, выход которого подключен к первому входу первого цифрового ключа, выход которого подключен к первому входу логического элемента ИЛИ, второй вход которого соединен с выходом второго цифрового ключа, первый вход которого подключен к третьему выходу дешифратора, а второй вход - к первому входу первого блока фазового сравнения, выход логического элемента ИЛИ соединен с входом сброса счетчика импульсов и с тактовым входом регистра, информационный вход которого подключен к выходу счетчика импульсов, а выход подключен к первому входу вычислительного устройства, первый выход которого является вторым выходом частотно-фазового дискриминатора согласно заявляемому техническому решению, введены второй блок фазового сравнения, первый и второй выходы которого соединены с первым и вторым входами дешифратора, первый вход объединен с первым входом первого блока фазового сравнения и является первым входом частотно-фазового дискриминатора, а второй вход объединен с вторым входом первого цифрового ключа, с тактовыми входами третьего триггера и счетчика импульсов и подключен к выходу второго делителя частоты, информационный вход которого подключен к второму выходу вычислительного устройства, а вход объединен с входом первого делителя частоты и подключен к выходу генератора высокой частоты, выход первого делителя частоты подключен к второму входу первого блока фазового сравнения и к тактовым входам первого и второго триггеров, информационный вход первого делителя частоты объединен с вторым информационным входом вычислительного устройства является вторым входом частотно-фазового дискриминатора.

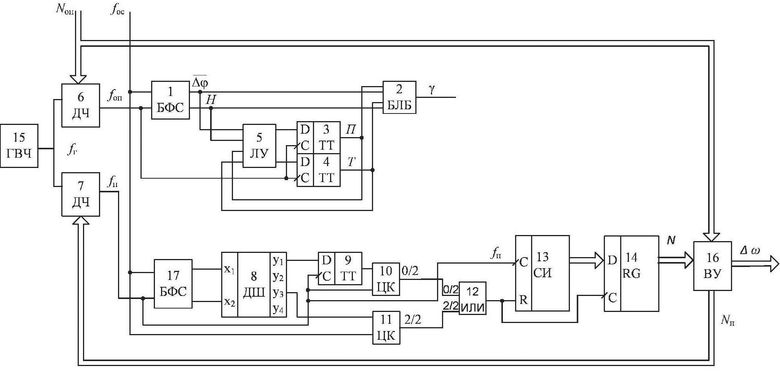

Сущность технического решения пояснена на чертеже, где на фиг. приведена функциональная электрическая схема предлагаемого устройства.

Частотно-фазовый дискриминатор содержит первый блок фазового сравнения 1, блок логической блокировки 2, блокирующие триггеры 3 и 4, логическое устройство 5, делители частоты 6 и 7, дешифратор 8, триггер 9, цифровые ключи 10 и 11, логический элемент ИЛИ 12, счетчик импульсов 13, регистр 14, генератор высокой частоты 15, вычислительное устройство 16, второй блок фазового сравнения 17.

Первый вход первого блока фазового сравнения 1 объединенный с первым входом второго блока фазового сравнения 17 является первым входом частотно-фазового дискриминатора и соединен со вторым входом второго цифрового ключа 11. Второй вход первого блока фазового сравнения 1 соединен с тактовыми входами первого 3 и второго 4 блокирующих триггеров и подключен к выходу первого делителя частоты 6. Первый выход первого блока фазового сравнения 1 подключен ко второму входу блока логической блокировки 2 и к первому входу логического устройства 5. Второй выход первого блока фазового сравнения 1 подключен к четвертому входу блока логической блокировки 2 и ко второму входу логического устройства 5. Первый вход блока логической блокировки 2 соединен с третьим входом логического устройства 5 и выходом первого триггера 3. Третий вход блока логической блокировки 2 соединен с четвертым входом логического устройства 5 и выходом второго триггера 4. Выход блока логической блокировки 2 является первым выходом частотно-фазового дискриминатора. Первый вход первого триггера 3 соединен с первым выходом логического устройства 5, а первый вход второго триггера 4 соединен со вторым выходом логического устройства 5. Первый выход дешифратора 8 подключен к информационному входу третьего триггера 9, а третий выход подключен к первому входу второго цифрового ключа 11. Выход третьего триггера 9 подключен к первому входу первого цифрового ключа 10. Первый вход логического элемента ИЛИ 12 соединен с выходом первого цифрового ключа 10, второй вход элемента ИЛИ 12 соединен с выходом второго цифрового ключа 11. Тактовые входы счетчика импульсов 13 и третьего триггера 9 соединены со вторым входом первого цифрового ключа 10 и со вторым входом второго блока фазового сравнения 17 и подключены к выходу второго делителя частоты 7. Первый и второй выходы второго блока фазового сравнения 17 соединены соответственно с первым и вторым входами дешифратора 8. Вход сброса третьего счетчика импульсов 13 соединен с выходом элемента ИЛИ 12 и тактовым входом регистра 14. Выход счетчика импульсов 13 подключен к информационному входу регистра 14. Выход регистра 14 подключен к первому информационному входу вычислительного устройства 16. Первый выход вычислительного устройства 16 является вторым выходом частотно-фазового дискриминатора. Второй выход вычислительного устройства 16 подключен к информационному входу второго делителя частоты 7. Входы делителей частоты 6 и 7 объединены и подключены к выходу генератора высокой частоты 15. Второй информационный вход вычислительного устройства 16 объединен с информационным входом первого делителя частоты 6 и является вторым входом частотно-фазового дискриминатора.

Частотно-фазовый дискриминатор работает следующим образом.

Импульсы

Блокирующие триггеры 3 и 4 служат для формирования сигналов индикации режимов работы частотно-фазового дискриминатора. Эти сигналы используются для работы логического устройства 5 и блокировки выходного сигнала блока фазового сравнения 1 с помощью блока логической блокировки 2. При этом высокий уровень сигнала П на выходе блокирующего триггера 3 соответствует режиму фазового сравнения частотно-фазового дискриминатора при

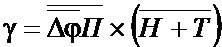

Блок логической блокировки 2 служит для формирования выходного сигнала в соответствии с логической функцией

Режиму фазового сравнения частотно-фазового дискриминатора соответствует наличие низких уровней сигналов H и Т и высокого уровня сигнала П, который с выхода блокирующего триггера 3 проходит на блок логической блокировки 2, разрешая прохождение сигнала

В режимах насыщения частотно-фазового дискриминатора на первый вход блока логической блокировки 2 поступает низкоуровневый сигнал П с выхода блокирующего триггера 3. В этом случае на выходе блока логической блокировки 2 появляется высокий уровень сигнала γ в режиме насыщения при

Логическое устройство 5 в зависимости от состояния выходов блока фазового сравнения 1 и блокирующих триггеров 3 и 4 формирует сигналы текущего режима работы, поступающие на информационные входы этих триггеров и записываемые в них в момент прихода импульса частоты

Таблица 1

при

0 0 0 1

0 0 1 0

0 0

0 1

при

0 1 0 1

0 1 1 0

0 1

1 0

при

1 0 0 1

1 0 1 0

1 0

1 0

Дешифратор 8 предназначен для выделения состояний второго блока фазового сравнения 17, соответствующих приходу 0 или 2 и более импульсов частоты

Таблица 2

Второй y2 и четвертый y4 выходы дешифратора 8 в работе частотно-фазового дискриминатора не используются.

При приходе импульса частоты

Если после прихода на второй вход блока фазового сравнения 17 импульса частоты

Выходной сигнал D-триггера 9 и сигнал с третьего выхода дешифратора 8 используются для управления цифровыми ключами 10 и 11 соответственно, выполненными на основе двухвходовых элементов И. На информационные входы цифровых ключей 10 и 11 поступают импульсы частот

Логический элемент ИЛИ 12 осуществляет функцию логического сложения двух логических сигналов.

Счетчик импульсов 13 предназначен для подсчета количества импульсов подстроечной частоты между двумя ситуациями прохождения двух импульсов одной из сравниваемых частот между двумя соседними импульсами другой.

Регистр 14 предназначен для запоминания подсчитанного счетчиком 13 количества импульсов N подстроечной частоты в момент прихода двух импульсов одной из сравниваемых частот между двумя соседними импульсами другой.

Вычислительное устройство 16, в зависимости от параметров электропривода, импульсного датчика частоты, количества N подсчитанных счетчиком 13 импульсов подстроечной частоты, от коэффициентов деления первого и второго делителей частоты и от частоты высокочастотного генератора осуществляет вычисление текущего значения рассогласования угловой скорости ∆ω сравниваемых сигналов

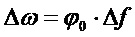

Частотно-фазовый дискриминатор широко используется в системах управления электроприводами с импульсными датчиками угловой скорости, то рассмотрим в качестве выходного параметра не рассогласование сравниваемых частотных сигналов Δ

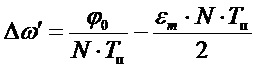

где φ0 – угловое расстояние между двумя соседними метками импульсного датчика частоты электропривода.

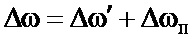

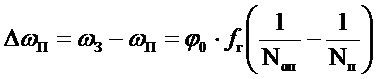

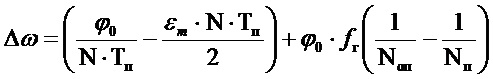

На основе данной частоты определяется значение ошибки по угловой скорости ∆ω', которое в дальнейшем пересчитывается на реальное значение ошибки по угловой скорости путем добавления разности ΔωП между заданной угловой скоростью ωЗ и угловой скоростью, соответствующей дополнительной подстраиваемой частоте fп:

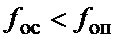

где ɛm – максимальное угловое ускорение электропривода, ωз – заданная угловая скорость электропривода, ωп – подстроечная угловая скорость, Nоп – коэффициент деления первого делителя частоты (определяет заданную угловую скорость), Nп – коэффициент деления второго делителя частоты (определяет подстроечную угловую скорость). Данный метод определения ошибки по угловой скорости позволяет получать более точные значения при больших отклонениях текущей угловой скорости от заданной. Первое слагаемое в выражении (5), соответствующее ∆ω', дает большую точность измерения по сравнению с выражением (3), т.к. при выборе fп ≈ fос происходит значительное увеличение N и снижение погрешности (1/N) его измерения. Второе слагаемое в выражении (5), соответствующее ΔωП, может быть рассчитано с высокой точностью, т.к. входящие в его состав аргументы характеризуются высокой точностью.

В отличие от реализованного в устройстве частотно-фазового дискриминатора, описанного в патенте RU 134375 от 10.11.2013, где непосредственно сравнивались частоты

В вычислительном устройстве 16 сначала вычисляется текущее значения частотного рассогласования Δ

Частотно-фазовый дискриминатор может находиться в трех основных режимах работы: насыщения при

При приходе двух подряд импульсов частоты

а) из режима насыщения при

б) из режима фазового сравнения происходит переход в режим насыщения при

в) режим насыщения при

При отсутствии импульсов частоты

В результате в частотно-фазовом дискриминаторе достигается расширение диапазона измерения величины частотного рассогласования сравниваемых частот.

Таким образом, предлагаемое техническое решение позволяет расширить диапазон измерения величины частотного рассогласования сравниваемых сигналов в частотно-фазовом дискриминаторе, за счет введения в него дополнительного блока фазового рассогласования, генератора высокой частоты и двух делителей частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР | 2010 |

|

RU2428785C1 |

| Частотный компаратор | 1983 |

|

SU1167719A2 |

| СТАБИЛИЗИРОВАННЫЙ ЭЛЕКТРОПРИВОД | 2016 |

|

RU2621288C1 |

| Частотно-фазовый дискриминатор | 1988 |

|

SU1589373A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Цифровой частотный детектор | 1979 |

|

SU815863A1 |

| Устройство для измерения фазовых сдвигов сигналов от многоканальных интерферометров термоядерных установок | 1983 |

|

SU1352395A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Частотный компаратор | 1981 |

|

SU1023630A1 |

Изобретение относится к области автоматики и вычислительной технике. Технический результат заключается в расширении диапазона измерения частотного рассогласования. Частотно-фазовый дискриминатор содержит второй блок фазового сравнения, первый и второй выходы которого соединены с первым и вторым входами дешифратора, первый вход объединен с первым входом первого блока фазового сравнения и является первым входом частотно-фазового дискриминатора, а второй вход объединен с вторым входом первого цифрового ключа, с тактовыми входами третьего триггера и счетчика импульсов и подключен к выходу второго делителя частоты, информационный вход которого подключен к второму выходу вычислительного устройства, а вход объединен с входом первого делителя частоты и подключен к выходу генератора высокой частоты, выход первого делителя частоты подключен к второму входу первого блока фазового сравнения и к тактовым входам первого и второго триггеров, информационный вход первого делителя частоты объединен с вторым информационным входом вычислительного устройства и является вторым входом частотно-фазового дискриминатора. Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах фазовой синхронизации и системах прецизионного синхронно-синфазного электропривода. 2 табл., 1 ил.

Частотно-фазовый дискриминатор, содержащий первый блок фазового сравнения, первый вход которого является первым входом частотно-фазового дискриминатора, а первый и второй выходы подключены соответственно ко второму и четвертому входам блока логической блокировки, выход которого является первым выходом частотно-фазового дискриминатора, а также первый и второй блокирующие триггеры, выходы которых соединены соответственно с первым и третьим входами блока логической блокировки, при этом информационные входы первого и второго блокирующих триггеров подсоединены соответственно к первому и второму выходам логического устройства, первый и второй входы логического устройства соединены соответственно с первым и вторым выходами первого блока фазового сравнения, а третий и четвертый входы - с выходами соответственно первого и второго блокирующих триггеров, кроме того, первый выход дешифратора подключен к информационному входу третьего триггера, выход которого подключен к первому входу первого цифрового ключа, выход которого подключен к первому входу логического элемента ИЛИ, второй вход которого соединен с выходом второго цифрового ключа, первый вход которого подключен к третьему выходу дешифратора, а второй вход - к первому входу первого блока фазового сравнения, выход логического элемента ИЛИ соединен с входом сброса счетчика импульсов и с тактовым входом регистра, информационный вход которого подключен к выходу счетчика импульсов, а выход подключен к первому входу вычислительного устройства, первый выход которого является вторым выходом частотно-фазового дискриминатора, отличающийся тем, что в него введены второй блок фазового сравнения, первый и второй выходы которого соединены с первым и вторым входами дешифратора, первый вход объединен с первым входом первого блока фазового сравнения и является первым входом частотно-фазового дискриминатора, а второй вход объединен с вторым входом первого цифрового ключа, с тактовыми входами третьего триггера и счетчика импульсов и подключен к выходу второго делителя частоты, информационный вход которого подключен к второму выходу вычислительного устройства, а вход объединен с входом первого делителя частоты и подключен к выходу генератора высокой частоты, выход первого делителя частоты подключен к второму входу первого блока фазового сравнения и к тактовым входам первого и второго триггеров, информационный вход первого делителя частоты объединен с вторым информационным входом вычислительного устройства и является вторым входом частотно-фазового дискриминатора.

| Подогреватель вискозы к прядильной машине | 1960 |

|

SU134375A1 |

| US 6567482 B1, 20.05.2003 | |||

| Устройство для геофизических измерений в скважинах | 1950 |

|

SU95439A2 |

| Частотно-фазовый дискриминатор | 1988 |

|

SU1589373A1 |

Авторы

Даты

2019-07-29—Публикация

2018-11-27—Подача