соединены соответственно к вторым входам первого и второго блока сумматоров по модулю два, выходы которых подключены соответственно к второму и третьему входам элемента ИЛИ, информационные входы блока отбраковки ошибок подключены соответственно к выходам первого и второго регистров, выход демодулятора подсоединен

к информационному входу блока разделения посыпок, а выход синхронизатора подсоединен к объединенным тактовым входам блока разделения посыпок, первого и второго регистров, блока отбраковки ошибок и демодулятора, ;причем выходы блока отбраковки Ьиибок являются выходами цифровой системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи и приема цифровых сигналов с обнаружением ошибок | 1984 |

|

SU1221759A1 |

| Система передачи и приема цифровых сигналов | 1985 |

|

SU1314463A1 |

| Система передачи цифровых сигналов | 1982 |

|

SU1091359A1 |

| Система передачи и приема информации с коррекцией ошибок | 1982 |

|

SU1078653A1 |

| Система передачи цифровых сигналов | 1987 |

|

SU1548849A1 |

| Система передачи и приема информации с коррекцией ошибок | 1981 |

|

SU964998A1 |

| Устройство передачи информации с защитой от ошибок | 1984 |

|

SU1188893A1 |

| Система для передачи и приема цифровой информации | 1989 |

|

SU1637025A1 |

| Цифровая система связи с исправле-НиЕМ ОшибОК | 1979 |

|

SU818024A1 |

| Устройство передачи сообщений | 1985 |

|

SU1506555A1 |

ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ОШИБОК, содержащая на передающей стороне последовательно соединенные генератор эталонного кода, блок сумматоров по модулю два, регистр и модулятор, последовательно соединенные синхронизатор и блок считывания, а также блок кодирования, при этом выход синхронизатора подсоединен к объединенным тактовым входам блока . кодирования и генератора эталонногокода, выход блока считывания подсоединен к тактовому входу регистра, а втором входы блока сумматоров по модулю два подключены к соответствующим вторым входам регистра, на приемной стороне - последовательно соединенные демодулятор, блок задержки, сумматор по модулю два, коррелятор, синхронизатор и генератор эталонного кода, причем :вход блока кодирования является входом цифровой системы, отличающаяся тем, что, с целью повышения достоверности принимаемой информации, на передающей стороне введены первый и второй сумматоры по модулю два, при этом выходы блока кодирования подсоединены к соответствующим вторым входам регистра, входы первого сумматора по модулю два подключены к соответствующим не- четным выходам блока кодирования, четные выходы которого подсодинены к соответствующим входам второго сумматора по модулю два, выходы первого сумматора по модулю два подсоединены к объединенным первым дополнительным входам блока сумматоров по модулю два и регистра, объединенные вторые дополнительные входы которых подключены к выходу второго сумматора по i модулю два, на приемной стороне введены последовательно соединенные бпоу (П разделения посылок, первый регистр и. первый блок сумматоров по модулю два, последовательно соединенные второй регистр и второй блок сумматоров по модулю два, последовательно соединенные третий блок сумматоров по модулю два, элемент ИЛИ и блок отбраковки ошибок, при этом выход демодулятора .и выход Задержка блока задержки подсоединены соответственно к второму и третьему входам сумматора по модулю два, выход которого подсоединен к первому входу третьего блок сумматоров по модулю два, прямой и Ийверсный выходы генератора эталонного кода подсоединены соответствен но к вторым входам коррелятора и третьего блока сумматоров по модулю два, выход нечетных посылок блока разделения посьток подсоединен к информационному входу второго регистра, а выходы сигнала суммы четных посьток и сигнала суммы нечетных посылок блока разделения посыпок под

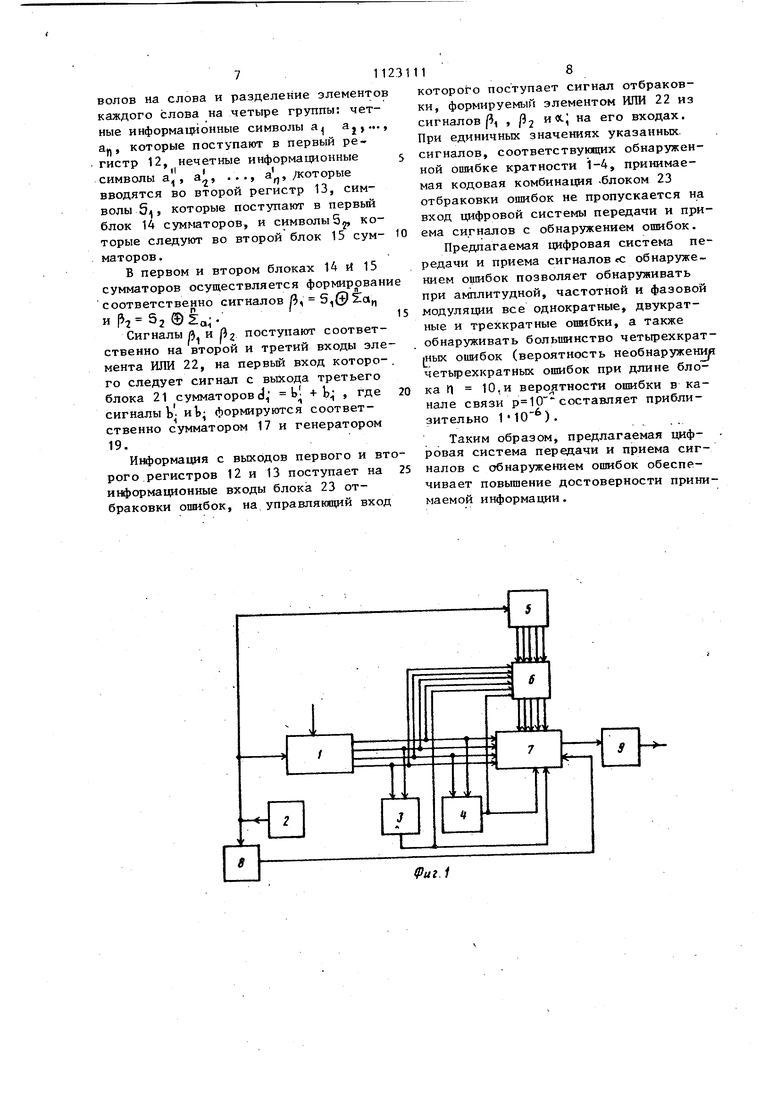

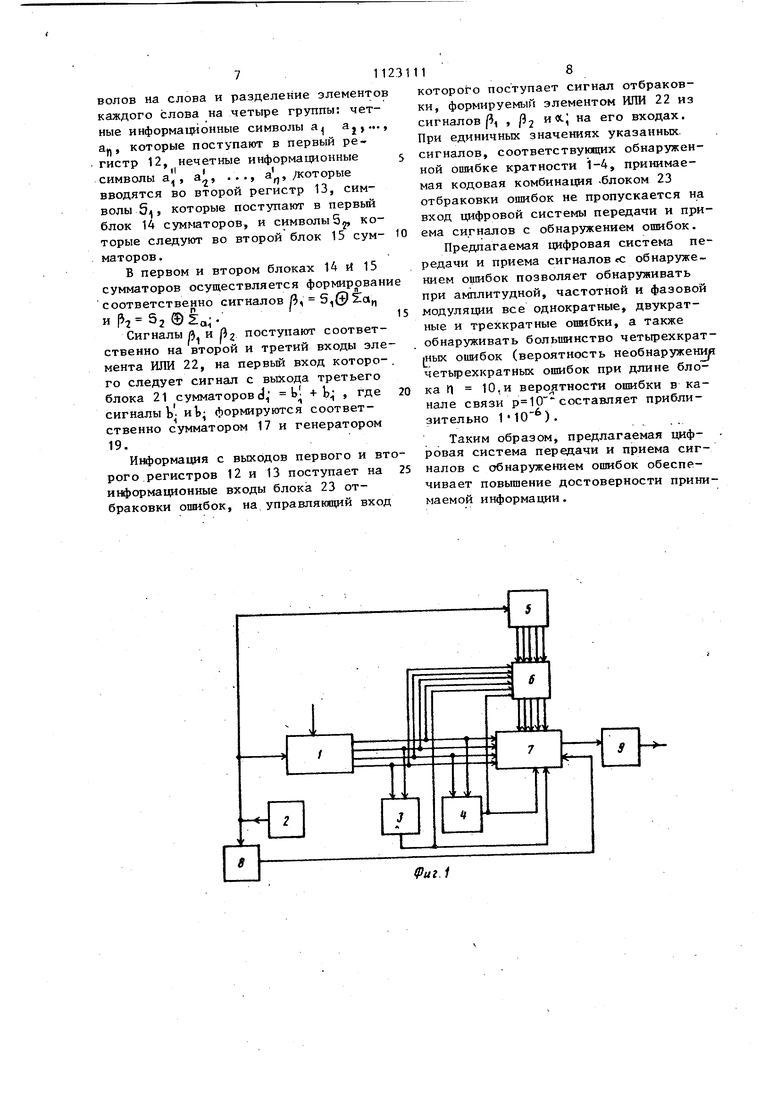

Изобретение относится к электросвязи и может быть использовано в телеметрии и при передаче данных. Известна цифровая система передачи и приема информации с обнаружением ошибок, содержащая на передающе стороне последовательно соединенные синхронизатор, генератор эталонного кода, блок сумматоров по модулю два и регистр, а также модулятор сигналов ФГМ, на приемной стороне - демодулятор и объединенные по входу сумматор по модулю два и элемент задержки, выход которого подключен к второму входу сумматора по модулю два,, выход которого подключен к первому входу коррелятора, к второму входу которого подключен выход генератора эталонного кода, к второму 4входу которого подключен выход син хронизатора l . Недостатком такой цифровой системы передачи и приема информагри с . обнаружением ошибок является низкая достоверность принимаемой информации Наиболее близкой к изобрет ению является цифровая система передачии приема И11формации с обнаружением ош бок, содержащая на передающей сторо не последовательно соединенные генератор эталонного кода, блок сумма торов по модулю два, регистр и моду лятор, последовательно соединенные синхронизатор if блок считывания, а также блок кодирования, при этом вы ход синхронизатора подсоединен к объединенным тактовым входам блока кодирования и генератора эталонного кода, выход блока считывания подеое динен k тактовому входу регистра, а вторые входы блока сумматоров по модулю два подключены к соответствующим вторым входам регистра, на приемной стороне - последовательно соединенные демодулятор, блок задержки, сумматор по модулю два, корреляторе, синхронизатор и генератор эталонного кода, причем вход блока кодирования является входом цифровой системы, на передающей стороне выходы блока кодирования через преобразователь кода подсоединены к соответствующим вторым входам регистра, а выход синхронизатора подсоединен к тактовому входу преобразователя кода, а на приемной стЬроне выход демодулятора подсоединен к объединенным входам блока задержки и второго корректора ошибок и к объединенным вторым входам, синхронизатора и сумматора по модулю два, выход которого через первый корректор ошибок подсоединен к входу второго корректора ошибок, выход генератора эталонного кода подсоединен к второму информационному входу первого корректора ошибок, а тактовые входы первого и второго корректоров ошибок подключены к выходу синхро1шзатора 2, Недостатком известной цифровой системы передачи и приема информации с обнаружением ошибок является низкая достоверность принимаемой информации. Цель изобретения - повышение достоверности принимаемой информации. Для достижения поставленной цели в цифровую систему передачи и приема информации с обнаружением ошибок, содержащую на передающей стороне последовательно соединенные генератор эталонного кода, блок сумматоров по мо3дулю два, регистр и модулятор, последовательно соединенные синхронизатор и блок считывания,а также блок кодирования, при этом выход синхрони . затора подсоединен к объединенным та товым ;входа блока кодирования и гене ;ратора эталонного кода, выход блока считывания подсоединен к тактовому входу регистра, а вторые входы блока сумматоров по модулю два подключены к соответствующим вторым входам регистра, на приемной стороне - последовательно соединенные дембдулятор, блок задержки, сумматор по модулю два, коррелятор,, синхронизатор и генератор эталонного кода, причем вход блока кодирования является входом цифровой системы, на передаю щей стороне введены первый и второй сумматоры по модулю два, при этом выходы блока кодирования подсоединены к соответствующим вторым входам регистра, входы первого сумматора по модулю два подключены к соответствующим нечетным выходам блока кодирования, четные выходы которого подсоединены к соответствующим входам второго сумматора по модулю два, выходы первого сумматора по модулю два подсоединены к объединенньпм первым дополнительным входам блока сумматоров по модулю два и регистра, объединенные вторые дополнительные входы которых подключены к выходу второго сумматора по модулю два, на приемной стороне введены последовательно соединенные блок разделения посыпок, первый регистр и первый блок сумматоров по модулюдва, последовательно соединенные второй регистр и второй блок сумматоров по модулю два, последовательно соединенные третий блок сумматоров по модулю два, элемент ИЛИ и блок отбраковки ошибок, При этом выход демодулятора и выход Задержка 2 блока задержки подсоединены соответственно к второму и третьему входам сумматора по | модулю два, выход которого подсоединен к первому входу третьего блока сумматоров по модулю два, прямой и инверсный выходы генератора-эта.лонного кода подсоединены соответственно к вторым входам коррелято-ра и третьего блока сумматоров по но дулю два, вь1ход нечетньк посыпок бл ка ; разделения посыпок подсоеДинен информационному входу второго регист 114 ра, а выходы сигнала суммы четных посылок и сигнала суммы нечетных посьшок блока разделения посыпок подсоединены соответственно к вторым входам первого и второго блока сумматоров по модулю два, выходы которых подключены соответственно к второму и третьему входам элемента ИЛИ, информационные входы блока отбраковки ошибок подключены соответственно к вы- ) первого и второго регистров, выход демодулятора подсоединен к информагр онному входу блока разделения посылок, а выход синхронизатора подсоединен к объединенным тактовым входам блока разделения ,росыnoKjnepBoro и второго регистров,блока отбраковки ошибок и демодулятора,причем выходы блока отбраковки ошибок являются выходами цифровой системы. На фиг. 1 приведена структурная электрическая схема предлагаемой цифровой системы передачи и приема информации с обнаружением ошибок, передающая часть; на фиг. 2 - то же, приемная часть. Передающая часть цифровой системы передачи и приема информации с обнаружением ошибок содержит блок 1 кодирования, синхронизатор 2, первый сумматор 3 по модулю два, второй сумматор 4 по модулю два, генератор 5 эталонного кода, блок 6-сумматоров по модулю два, регистр 7, блок 8 считывания, модулятор 9, Приемная часть цифровой системы передачи и приема информации с обнаружением ошибок содержит демодулятор 10, блок 11 разделения посыпок, первый регистр 12, второй регистр 13, первый блок 14 сумматоров по модулю два, второй блок 15 сумматоров по модулю два, блок 16 задержки, сумматор 17 по модулю два, коррелятор 18, генератор 19 эталонного кода, синхронизатор 20, третий блок 21 сумматоров по модулю два, элемент ИЛИ 22, блок 23 отбраковки ошибок. Цифровая система передачи и приема информации с обнаружением ошибок работает следующим образом. На передающей стороне (фиг. 1) в блоке 1 кодирования 2п-значные информационные слова преобразуются в 2л-значные кодовые слова формируемого кода 3(П + 1), 2ll. Полученные 2п-значные кодовые слова записьгоаются в регистр 7 и в виде параллельного кода подаются в блок 6 сумматоров по модулю два. Все нечетные посыпки с выхода блока 1 кодирования поступают на вход первого сумматора 3 по модулю два, а все четные посыпки вводятся вО второй суг матор 4. Выходы первого и второго сумматоров 3 и 4 связаны с регистром 7 и блоком 6 сумматоров, на вторые входы которого подаются посыпки (М + О-значного эталонного кода, с выходов генератора 5, например типа М-п6следовательности или другого код ic острой функцией корреляции. Регистр 7 имеет 3(П + 1) ячеек. На 211 ячеек подаются информационные посылки из блока 1 кодирования, по одной посылке вьщают первый и второ сумматоры 3 и 4. Эти посыпки образу ются по правилу. 5, ®.|a,;.,i .tq2;7 где S сигнал на выходе первого сумматора 3J Sg сигнал на выходе второго сумматора 4. В блок 6 сумматоров поступают 2п .информационных символов блока 1 кодирования, а .также посылки 5 и Sj Поразрядное суммирование по модулю два производится в блоке 6 сумматоров по правилу а,©а,, aj0aj©b2 Cjj , 5,©е,®Ъ„,С„+,, где а и а-- информационные четные и нечетные символы, символы эталонного код Таким образом, блок 6 сумматоров вьщает (п+1) посылок С, С,...,С, , которые записываются в соотве ствующих ячейках регистра 7. В результате в ячейках регистра 7 будет записана кодовое слово, сое тоящее из 3(п+1) элементов: а,с,аХсга2а,с,а,,...,с „с„а„5,С„,9,. С помощью блока В считывания, уп равляемого синхронизатором 2, производится преобразование параллельного 3(), , записанного в регистре 7, в последовательный ко Последовательность двоичных посылок поступает на вход модулятора 9, где осуществляется амплитудная, частотная или фазовая модуляция несущего колебания, на выходе демодулятора 10 получается двоичный видеосигнал в виде последовательности слов длиной 3(п+1) элементов, В любом слове с номерами (Зг-2) и 3, где г 1,2,.,.,Г1, являются информационными. Элементы с номерами 3(1-1 образованы из элементов с номерами (ЗГ-2), Зг и элемента с номером 2 эталонного кода путем их суммирования по модулю два. Последние h элементов в кодовой комбинации являются проверочными. С помощью сумматора 17 и блока 16 задержки, который обеспечивает задержку на с и 2ь, получаются комбинации из (Зп+3) элементов, в которых каждьш третий элемент является элементом Ь; восстановленного эталонного кода. Действительно, если а и a- - информационные четные и нечетные символы, Ь, элементы этаib a;@al+с; . При лонного кода, тоЬ поразрядном суммировании по модулю два прямого кода и кода, задержанного «. и на 2t, получаем. .а агСга аэС аза С а б С.бз . ... ,oi2CjO(ja3C3a3....- а 5 U 1. 1- г. t. oj ..... bjь„Ьп, Сигнал с выхода сумматора 17 пос- . тупает в коррелятор 18, куда подаются также символы эталонного кода, а также на блок 21 сумматоров, на вторые входы которогб поступают также сигналы эташонного кода с выходов генератора 19. В результате осущестявляется поэлементная проверка соответствия восстановленного и местного эталонного кодов, Вьщеленные синхросигналы (пики функции корреляции коррелятора 18) управляют работой синхронизатора 20. Синхронизатор 20 в свою очередь обеспечивает синхронную работу демодулятора, блока 11 разделения посьшок, первого и второго регистров 12 и 13 и блока 23 отбраковки ошибок. Сигнал с выхода демодулятора 10 поступает на информационный вход блока 11 разделения посылок, в котором происходит разделение потока символов на слова и разделение элементо каждого слова на четыре группы: четные информащюнные символы а а,... ajj, которые поступают в первый регистр 12, нечетные информационные символы а , а, ..., а, /которые вводятся во второй регистр 13, символы 5ц которые поступают в первый блок 14 cyм aтopoв, и символы Sp которые следуют во второй блок 15 сумматоров. В первом и втором блоках 14 rt 15 сумматоров осуществляется формирован соответственно сигналов в, S,@5Ia(, И|, 52®1„.. Сигналы Л и 2 поступают соответственно на второй и третий входы эле мента ИЛИ 22, на первьй вход которого следует сигнал с выхода третьего блока 21 сумматоров Ь. + Ь , где сигналы Ь- иЬ- формируются соответственно сумматором 17 и генератором 19. Информация с выходов первого и вт рого регистров 12 и 13 поступает на информационные входы блока 23 отбраковки ошибок, на управляюпщй вход 1 118 которого поступает сигнал отбраковки, формируемый элементом ИЛИ 22 из сигналов f, 2 ° входах. При единичных значениях указанных сигналов, соответствующих обнаруженной ошибке кратности 1-4, принимаемая кодовая комбинация -блоком 23 отбраковки ошибок не пропускается на вход цифровой системы передачи и приема сигналов с обнаружением ошибок. Предпагаемая цифровая система передачи и приема сигналов «с обнаружением оцибок позволяет обнаруживать при амплитудной, частотной и фазовой модуляции все однократные, двукратные и трехкратные ошибки, а также обнаруживать большинство четырехкрат1НЫХ ошибок (вероятность необнаруженш четырехкратных ошибок при длине блока Ц 10.и вероятности ошибки в канале связи составляет приблизительно 1 10 ) . Таким образом, предлагаемая цифровая система передачи и приема сигналов с обнаружением ошибок обеспечивает повьш ение достоверности принимаемой информации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровая система связи с исправле-НиЕМ ОшибОК | 1979 |

|

SU818024A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Система передачи и приема информации с коррекцией ошибок | 1981 |

|

SU964998A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-11-07—Публикация

1982-11-10—Подача