Изобретение относится к электро связи и может быть использовано в телеметрии и при передаче данных, Известна система передачи и прие информации с коррекцией ошибок, содержащая на передающей стороне последовательно соединенные синхрониза тор, генератор эталонного кода, бло сумматоров по модулю два и регистр, а также модулятор, на приемной стор не - демодулятор и объединенные по входу сумматор по модулю два и элемент задержки, выход которого подкл чен к второму входу сумматора по мо дулю два, выход которого подключен к первому входу коррелятора, к втор му входу которого подключен выход генератора эталонного кода, к второ му входу которого подключен выход синхронизатора Cl.J Недостаток- указанной системы низкая помехоустойчивость. Известна также система передачи и приема информации с коррекцией ошибкок, содержащая на передающей стороне последовательно соединенные блок кодирования и преобразователь кода, последовательно соединенные синхронизато э и генератор эталонного кода, последовательно соединенны регистр и модулятор, а также блок сумматоров по модулю два и блок счи тывания, выход которого подключен к управляющему входу регистра, при этом выходы преобразователя кода подключены к объединенным первым входам блока сумматоров по модулю два и регистра, выходы генератора эталонного кода подключены к вторым входам блока сумматоров по модулк) два, выходы которого подключены к другим входам регистра, выход синхр низатора подключен к объединенным входам блока кодирования, преобразо вателя кода и блока считывания, вхо ды блока кодирования являются входа ми системы, на приемной стороне последовательно соединенные элемент задержки, сумматор по модулю два, коррелятор, синхронизатор и генератор эталонного кода, последовательно соединенные первый корректор О1ии бок и второй корректор ошибок, а также демодулятор, выход которого подключен к входу элемента задер ки и другим входам синхронизатора и сумматора по модулю два, выход кото рого подключен к первому входу первого корректора ошибок, выход генеipaTopa эталонного кода подключен к второму входу первого корректора сяйибок и другому входу коррелятора, выход демодулятора подключен к второму входу второго корректора ошибок, а выход синхронизатора подключен к объединенным третьим входам первого корректора ошибок и второго корректора ошибок, выход которого является выходом систем С2 3. Недостатком известной системы является низкая помехоустойчивость, вследствие чего 25% двухкратных ошибок не исправляется и не обнаруживается. Цель изобретения - повьлиение помехоустойчивости . Для достижения указанной цели в систему передачи и приема информации с коррекцией ошибок, содержащую на передающей стороне последовательно соединенные блок кодирования и преобразователь кода, последовательно соединенные синхронизатор и генератор эталонного кода, последовательно соединенные регистр и модулятор, а также блок сумматоров по модулю два и блок считывания, выход которого подключен к управляющему входу регистра, при этом выходы преобразователя кода подключены к объединенным первым входам блока сумматоров по модулю два и регистра, выходы генератора, эталонного кода подключены к вторым входам блока сумматоров по модулю два, выходы которого подключены к другим входам регистра, выход синхронизатора подключен к объединенным входам блока кодирования, преобразователя кода и блока считывания, входы блока кодирования являются входами системы, на приемной стороне - последовательно соединенные элемент задержки, сумматор по модулю два, коррелятор, синхронизатор и генератор эталонного кода, последовательно соединенные первый корректор ошибок и второй корректор ошибок, а также демодулятор, выход которого подключен к входу элемента задержки и другим входам синхронизатора и сумматора по модулю два, выход которого подключен к первому входу первого корректора ошибок, выход генератора эталонного кода подключен к второму входу первого корректора ошибок и другому входу коррелятора, на передающей стороне введён сумматор по модулю два, входы которого соединены с выходами преобразователя кода, а выход сумматора по модулю дваподключен к дополнительным входам регистра и блока сумйаторов по модулю два, на приемной cfoроне введены последовательно соединенные преобразователь кода, дополнительный сумматор по модулю два и первый инвертор, последовательно соединенные первый элемент ИЛИ, второй инвертор, элемент И и третий инвертор, а также выходной блок элементов И и второй элемент ИЛИ, которого соединены с первыми выхо|дами второго корректора ошибок, а выход второго элемента ИЛИ подключен к второму входу элемента И, вторые выходы второго корректора ошибок подключены к входам выходного блока элементов И, дополнительный вход которого соединен с выходом третьего инвертора, выход демодулятора подключен к входу преобразователя кода и третьему входу первого корректора ошибок, st выход первого инвертора подключен к третьему входу элемента и.

На фиг, 1 приведена структурная электрическая схема системы передачи и приема информации с коррекцией ошибок; на фиг. 2 - схема преобразователя кода.

Система передачи и приема информции с коррекцией ошибок содержит на передающей стороне блок 1 кодирования, преобразователь 2 кода, регист 3, блок 4 сумматоров по модулю два, генератор 5эталонного кода, синхронизатор 6, блок 7 считывания, модулятор 8 и сумматор 9 по модулю два, на приемной стороне - демодулятор 10, сумматор 11 гго модулю два, элемент 12 задержки, синхронизатор 13, генератор 14 эталонного кода, коррелятор 15, первый корректор 16 ошибок, второй корректор 17 ошибок, элементы ИЛИ 18 и 19, второй инвертор 20, элемент И 21, третий инвертор 22, выходной блок 23 элементов И, преобразователь 24 кода, дополнительный сумматор 25 по модулю два и первый инвертор 26.

Система работает следующим образом.

В блоке 1 кодирования формируется исходный двоичный кодовый сигнал в виде К-разрядных слов, которые в преобразователе 2 кода (фит, 2) преобразуются в П -значные слова в соответствии с кодом Хэминга, исправляющим однократные ошибки. Полученные п-значные кодовые комбинации записываются в регистр 3 (подаются на его первые входы) и следуют на первые входы блока 4 сумматоров по модулю два. На вторые входы блока 4 сумматоров по модулю два подаются h-значные эталонные слова, вырабатываемые в генераторе 5 эталонного кода, В блоке сумматоров по модулю два производится поэлементное суммирование по модулю два символов информационного и эталонного слов.

В сумматоре 9 по модулю два определяется символ.

где а - символ кбда на выходе преобразователя 2 кода. Этот символ с выхода сумматора 9 по. модулю два поступает на вход блока 4 сумматоров по модулю два, где формируется символ

с 0 ©ь

П+-1 П-И

П + 1

где bf,,. - дополнительный символ, выдаваемый генератором 5 эталонного кода.

Кодовый сигнал с выходов блока 4 сумматоров по модулю два вводится в регистр 3 через его другие входы. |При этом в регистре 3, содержащем 2 ячеек, формируется кодовый сиг нал

l l«2 2°3S- «n -,(n.-,10

причем символы d и c.j размещаются соответственно в ячейках с нечетными и четными номерами,

Из регистра 3 кодовый сигнал считывается по сигналам, которые вырабатывает блок 7 считывания. При этом параллельный код преобразуется в последовательный. В модуляторе 8 производится преобразование этого кода

в код, который используется для передачи сигналов,

На выходе демодулятора 10 при отсутствии помех образуется такая же последовательность посылок а у и с ,

которая поступает на вход модулятора 8, Последовательный кодовый си.гнал вводится на первый вход сумматора 11 по модулю два непосредственно и с задержкой на длительность

одной посылки (посредством элемен30

та 12 задержки) на второй вход сумматора 11 по модулю два. При этом происходит восстановление на четных позициях кодового слова элементов Ь. эталонного кода

- . V4%Cf - h.,

:- ... o,C, о,

п-и

1 1 2Ч з ; Л Л- пЬпОпиЧ..

где .с. ; Ъ .®с. , так как Cj а,-®Ъ .

Восстановленный эталонный кодовый сигнал Ь поступает на вход коррелятора 15, на другой вход которого следует кодовый сигнал Ъ с выхода генератора 14 эталонного кода. Коррелятор 15 в каждой тактовой точке

1

вычисляет функцию L-bib- и выделяет

. V

основной ПИК функции корреляции, соответствующий групповому синхросиг- . налу, т.е. сигналу, обозначающему, например, начало кодового 2(п + ()-раз рядного сигнала. Этот синхросигнал служит для обеспечения синфазности сигнала, формируемого синхронизатором 13, с входным СИГНоШОМ.

В первый корректор 16 ошибок вводится последовательность посылок с выхода демодулятора 10 , . .q-c ajC....

«п сn о n+1 сигналы Ц с выхода сумматора 11 по модулю два и сигналы bib2b,,b4 . n+vj с выхода генератора 14 эталонного кода.

Первый корректор 16 ошибок проиэ-водит инвертирование тех посылок .«, которые находятся между двумя искаженными элементами fc, Например, если сравнение Ъ и Ъ показывает, что имеются отличия в элементах/Ъ и ,Ъ,, а также Ър Ъ, то посылка 0 инвертируется.

Частично скорректированная последовательность .. ,.о|..,й подается во второй корректор 17 слпибок, В нем по правилу Хэминга исправляются однократные ошибки. Например, если на вход первого корректора 16 ошибок поступает последовательность в которой искажены элементы 5 с-,02 «э то из-за отли.чия элементов Ъ2 и Ъ а также fcj и Ьд в первом корректоре 16 ошибок инвертируют элемент Wj , .Далее последовательность с искаженным элементом e(j вводится во второй корректор 17, в котором обнаруживается и исправляется искаженный элемент .

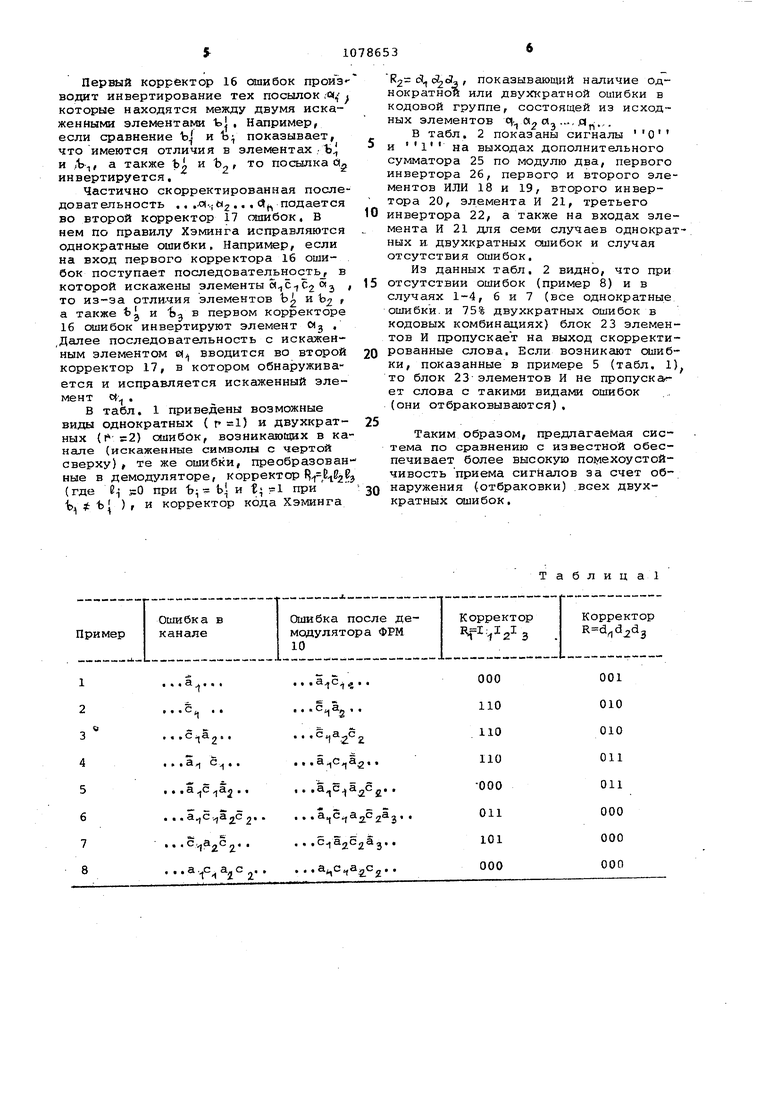

В табл. 1 приведены возможные виды однократных { р 1) и двухкратных (г s:2) ошибок, возникающих в канале (искаженные символы с чертой сверху), те же ошибки, преобразованные в демодуляторе, корректор Ri, (где е sO при Ц и f- -1 при Ъл Ь ) , и корректор кода Хэминга

R2 (Я , показывающий наличие однократной или двухкратной ошибки в кодовой группе, состоящей из исходных элементов Ч- « а, ..., д .,.

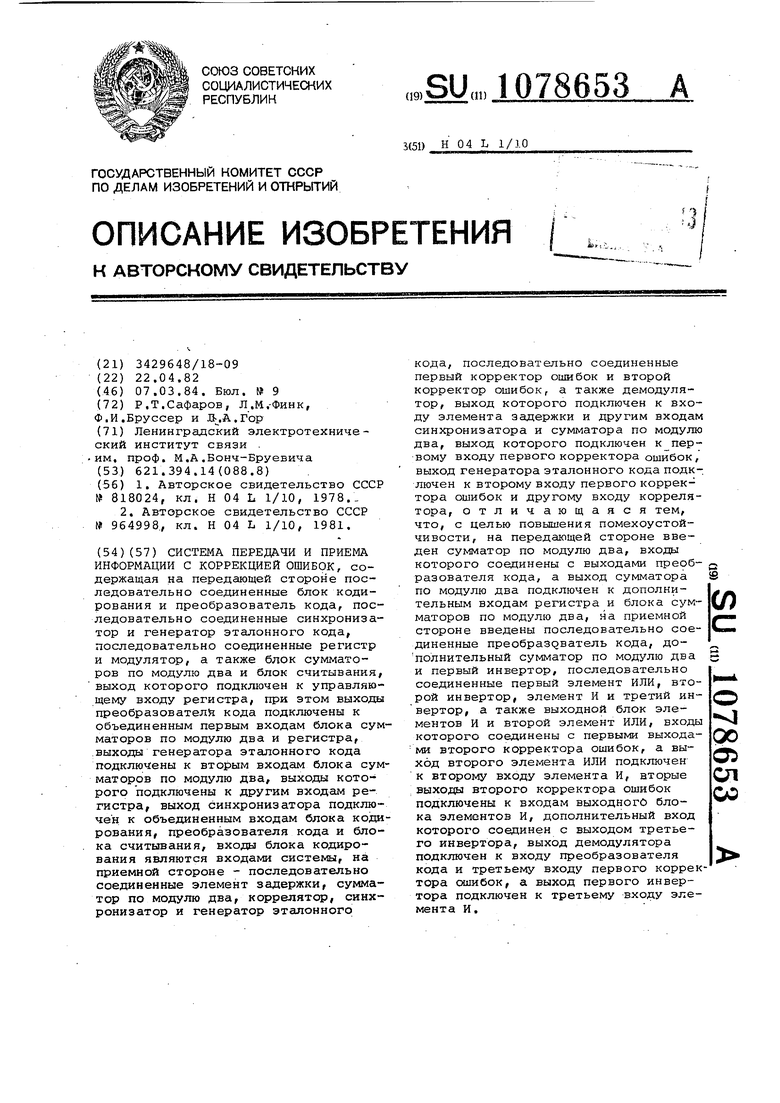

В табл. 2 показаны сигналы О и на выходах дополнительного сумматора 25 по модулю два, первого инвертора 26, первого и второго элементов ИЛИ 18 и 19, второго инвертора 20, элемента И 21, третьего

0 инвертора 22, а также на входах элемента И 21 для семи случаев однократных и двухкратных оиибок и случая отсутствия ошибок.

Из данных табл. 2 видно, что при

5 отсутствии ошибок (пример 8) и в случаях 1-4, 6 и 7 (все однократные ошибки, и 75% двухкратных ошибок в кодовых комбинациях) блок 23 элементов И пропускает на выход скорректи0 рованные слова. Если возникают олибки, показанные в примере 5 (табл. 1) то блок 23-элементов И не пропуска ет слова с такими видами ошибок (они отбраковываются).

Таким образом, предлагаемая система по сравнению с известной обеспечивает более высокую помехоустойчивость приема сигналов за счет обQ наружения (отбраковки) всех двухкратных ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи и приема информации с коррекцией ошибок | 1981 |

|

SU964998A1 |

| Система передачи и приема цифровых сигналов с обнаружением ошибок | 1984 |

|

SU1221759A1 |

| Цифровая система передачи и приема информации с обнаружением ошибок | 1982 |

|

SU1123111A1 |

| Система передачи цифровых сигналов | 1987 |

|

SU1548849A1 |

| Система передачи цифровых сигналов | 1982 |

|

SU1091359A1 |

| Система передачи и приема цифровых сигналов | 1985 |

|

SU1314463A1 |

| Система для передачи и приема цифровой информации | 1989 |

|

SU1637025A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Устройство передачи информации с защитой от ошибок | 1984 |

|

SU1188893A1 |

| Устройство передачи сообщений | 1985 |

|

SU1506555A1 |

СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ С КОРРЕКЦИЕЙ ОШИБОК, содержащая на передающей стороне последовательно соединенные блок кодирования и преобразователь кода, последовательно соединенные синхронизатор и генератор эталонного кода, последовательно соединенные регистр и модулятор, а также блок сумматоров по модулю два и блок считывания, выход которого подключен к управляющему входу регистра, при этом выходы преобразователи кода подключены к объединенным первым входам блока сумматоров по модулю два и регистра, .выходы генератора эталонного кода подключены к вторым входам блока сумматоров по модулю два, выходы которого подключены к другим входам регистра, выход синхронизатора подключен к объединенным входам блока кодирования, преобразователя кода и блока считывания, входы блока кодирования являются входами системы, на приемной стороне - последовательно соединенные элемент задержки, сумматор по модулю два, коррелятор, синхронизатор и генератор эталонного кода, последовательно соединенные первый корректор ошибок и второй корректор ошибок, а также демодулятор, выход которого подключен к входу элемента задержки и другим входам синхронизатора и сумматора по модулю два, выход которого подключен к первому входу первого корректора ошибок, выход генератора эталонного кода подключен к второму входу первого корректора ошибок и другому входу коррелятора, отличающаяся тем, что, с целью повышения помехоустойчивости, на передающей стороне введен сумматор по модулю два, входы которого соединены с выходами преоб& разователя кода, а выход сумматора по модулю два подключен к дополни(Л тельным входам регистра и блока сумматоров по модулю два, на приемной стороне введены последовательно соединенные пpeoбpaзQвaтeль кода, дополнительный сумматор по модулю два и первый инвертор, последовательно соединенные первый элемент ИЛИ, второй инвертор, элемент И и третий инвертор, а также выходной блок эле ментов И и второй элемент ИЛИ, входы 00 которого соединены с первыми выхода ми второго корректора ошибок, а выо ход второго элемента ИЛИ подключен ел к второму входу элемента И, вторые выходы второго корректора ошибок СО подключены к входам выходного блока элементов И, дополнительный вход которого соединен с выходом третьего инвертора, выход демодулятора подключен к входу преобразователя кода и третьему входу первого корректора ошибок, а выход первого инвертора подключен к третьему входу элемента И.

Таблица

2

25

CO

ю

J

J2

7J

28

eJ

re

77

у y Ф J у y

fS

Г8

20 - f - 22

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровая система связи с исправле-НиЕМ ОшибОК | 1979 |

|

SU818024A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Система передачи и приема информации с коррекцией ошибок | 1981 |

|

SU964998A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-03-07—Публикация

1982-04-22—Подача