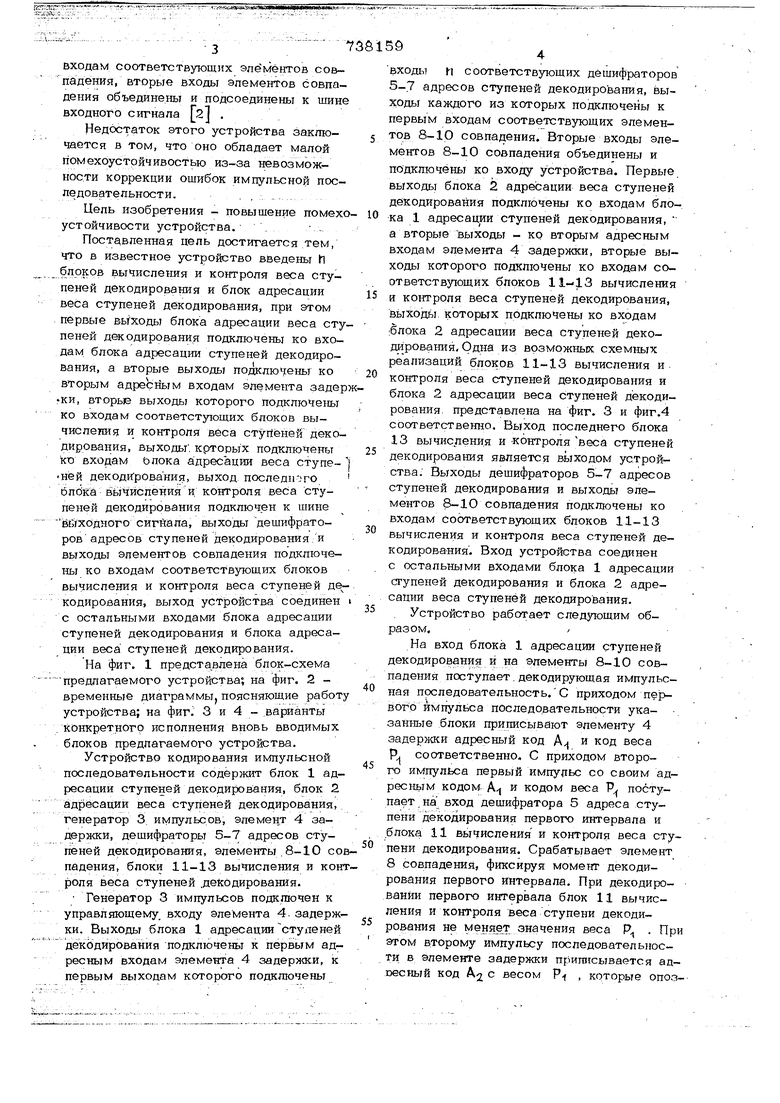

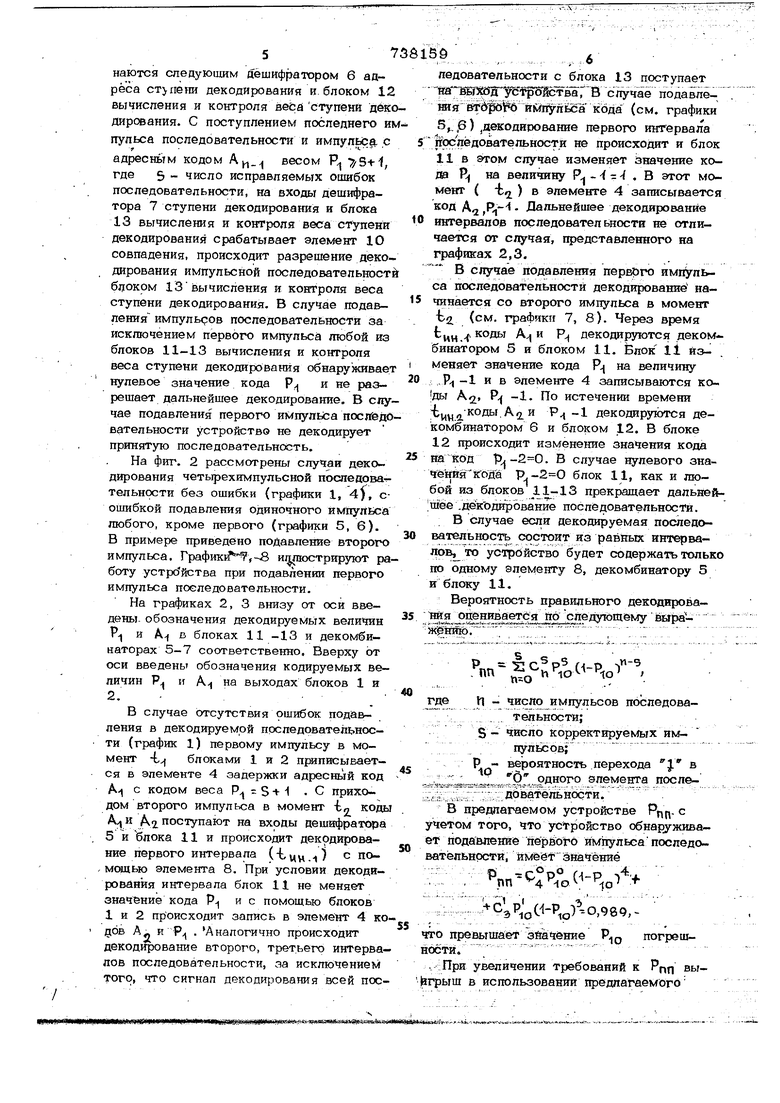

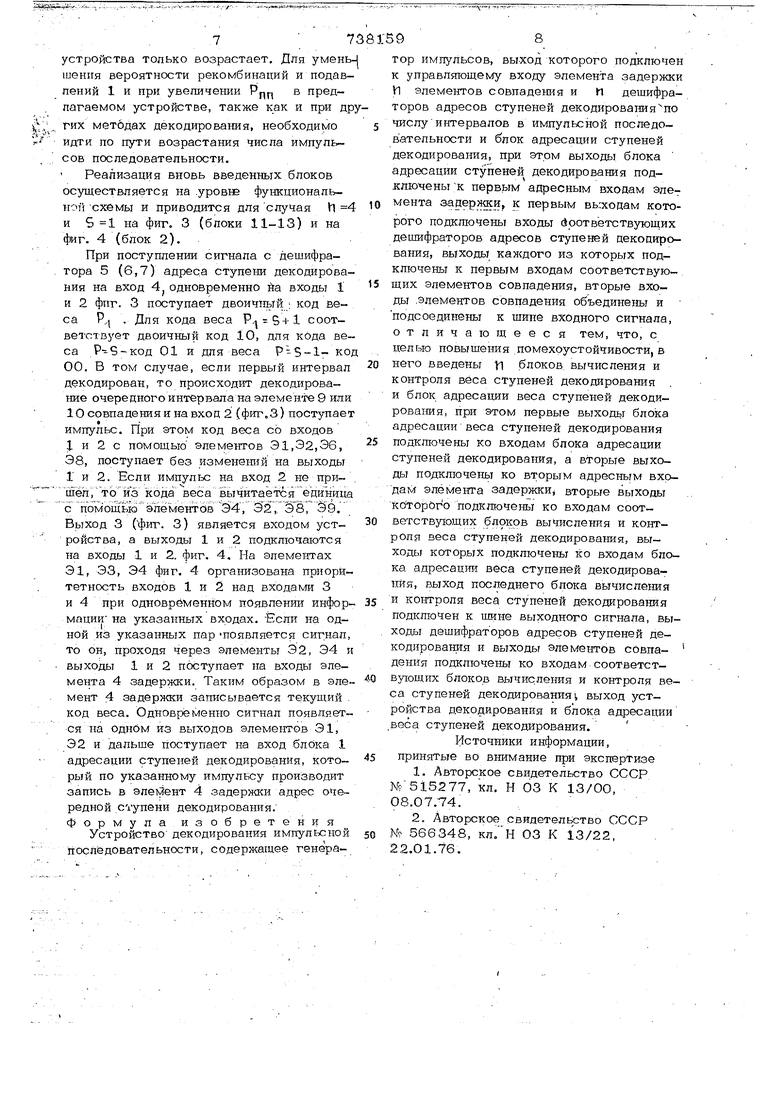

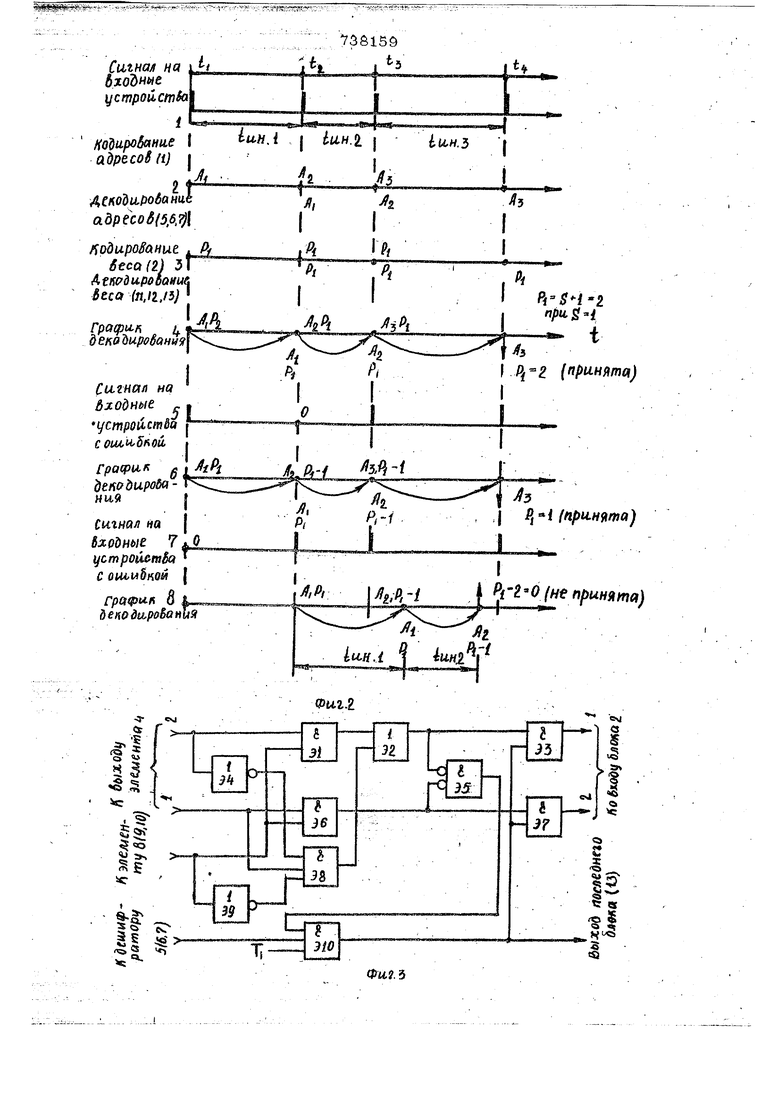

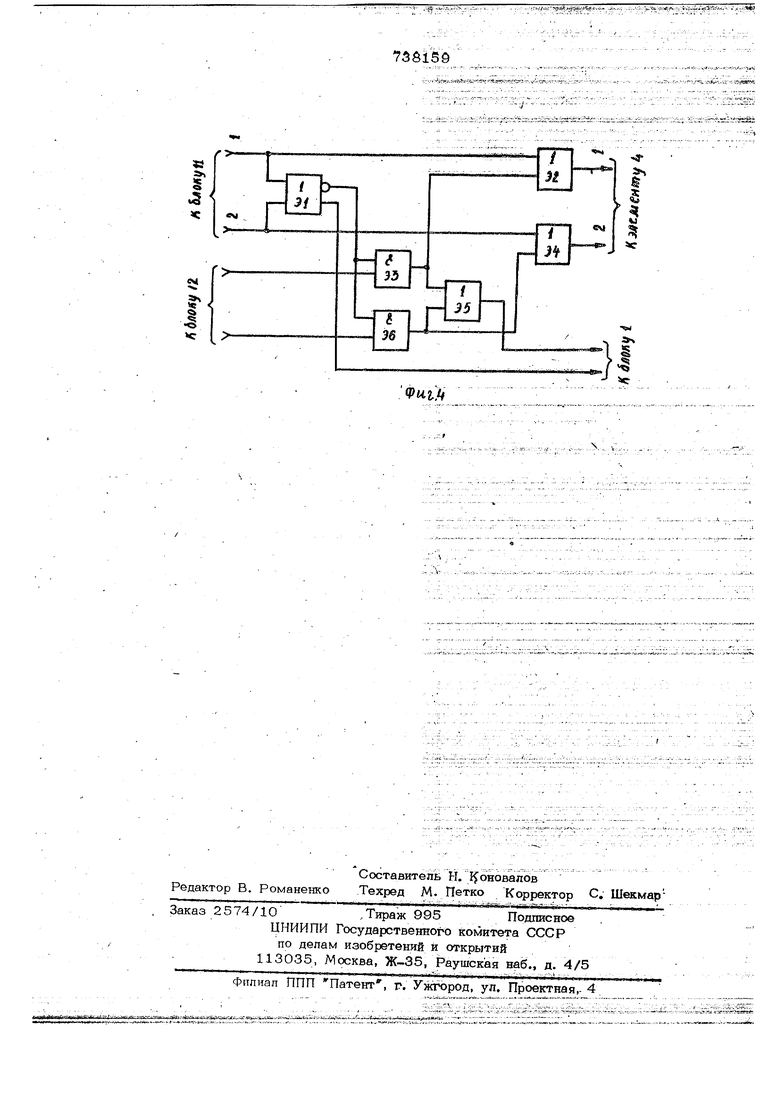

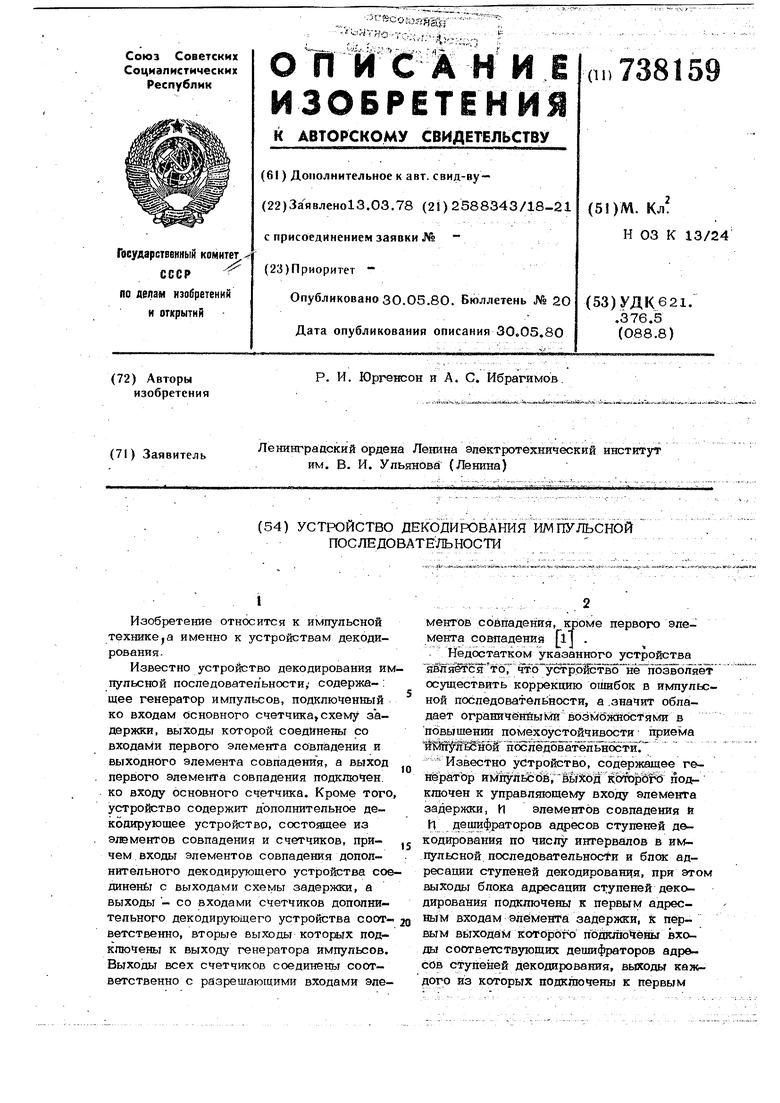

Изобретение относится к импульсной технике,а именно к устройствам декодирования. Известно устройство декодирования им пульсной последовательности, содержа- ; щее генератор импульсов, подключенный ко входам основного счетчика, схему задержки, выходы которой соединены со входами первого элемента совпадения и выходного элемента совпадения, а выход первого элемента совпадения подключен, ко входу основного счетчика. Кроме того устройство содержит дополнительное декодирующее устройство, состоящее из элементов совпадения и счетчиков, причем входы элементов совпадения дополнительного декодирующего устройства сое диненЬт с выходами схемы задержки, а выходы - со входами счетчиков дополнительного декодирующего устройства соот ветственно, вторые выходы которых подключены к выходу генератора импульсов. Выходы всех счетчиков соединень соответственно с разрешающими входами элементов совпадения, кроме первого элемента совпадени 3 fit . -.1 , .. - ,.,- и J« Недостатком указанного устройства ШпШгс тЬ7 ЗДВ устррйствВ нёТ оэвГопяе осуществить коррекцию ошибок в импульсной последовательности, а .значит обладает ограниченными вбзм6ядабсТя «т в повышении помехоустойчивости приема 11Ш л18н6Ж пбспедов1атё ьности, Известно устройство, содержащее гейёратЬр кШугК Х:6&Г а подключен к управляющему входу элемента задержки, И элементов совпадения и И дешифраторов адресов ступеней декодирования по числу интервалов в импульсной последовательности и блок адресации ступеней декодирования, при этом выходы блока адресации ступеней декодирования подключены к первым адресным входам элемента: задержки, к первым выходам котброгч) подключёны входы соответствующих дешифраторов адресов ступеней декодирования, выходы каждого из которых подключены к первым входам соответствующих элементов совпадения, вторые входы элементов совпадения объединены и подсоединены к шин входного сигнала 2 . Недостаток этого устройства заключается в том, что оно обладает малой помехоустойчивостью из-за невозможности коррекции ошибок импульсной последовательности..... Цель изобретения - повышение помех устойчивости устройства. , , Поставленная цель достигается тем, что в известное устройство введены h .. ..блоков вычисления и контроля веса ступеней декодирования и блок адресации веса ступеней декодирования, при этом первые выходь) блока адресации веса сту пеней декодирования подключены ко входам блока адресации ступеней декодирования, а вторые выходы подключены ко вторым адресным входам элемента заде Ки, вторье выходы которого подключены ко входам соответстующих блоков вычисления и контроля веса стуйенеи декодирования, выходы , крторых подключены ко входам ьлока а:дресации веса ступеней декодирование, выход последпого олбка вычисленияи контроля вес:а ступеней декодирования подключен к шине |5Г,1Ходного сигнала, выходы дешифраторовадресов ступеней декодирования и выходы элементов совпадения подключены ко входам соответствующих блоков вычисления и контроля веса ступеней де кодирования, выход устройства соединен с остальными входами блока адресации ступеней декодирования и блока адресации веса ступеней декодирования. На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 временные диаграммы, поясняющие работ устройства; на фиг. 3 и 4 - ,варианты .конкретного исполнения вновь вводимых блоков предлагаемого устройства. Устройство кодирования импульсной последовательности содер}кит блок 1 ад ресации ступеней декодирования, блок 2 адресации веса ступеней декодирования, генератор 3 импульсов, элеменл 4 задержки, дешифраторы 5-7 адресов ступеней декодирования, элементы . 8-10 со падения, блоки 11-13 вычисления и ко роля веса ступеней .декодирования. Генератор 3 импульсов подключен к управляющему, входу элемента 4- задерж ки. Выходы блока 1 адресации сту11еней декодирования подключены к первым ад ресным входам элемента 4 задержки, к первым выходам которого подключены вход111 м соответствующих дешифраторов 5-7 адресов ступеней декодирования, выходы каждого из которых подключены к первым входам соответствующих элементов 8-10 совпадения. Вторые входы элементов 8-10 совпадения объединены и подключены ко входу устройства. Первые выходы блока 2 адресации веса ступеней декодирования подключены ко входам блока 1 адресации ступеней декодирования, а вторые выходы - ко вторым адресным входам элемента 4 задержки, вторые выходы которого подключены ко входам соответствующих блоков вычисления и контроля веса ступеней декодирования, выходь которых подключены ко входам :ёлока 2 адресации веса ступеней декоди рования. Одна из возможных схемных реализаций блоков 11-13 вычисления иконтроля веса ступеней декодирования и блока 2 адресации веса ступеней декодирования, представлена на фиг. 3 и фиг.4 соответственно. Выход последнего блока 13 вычисления и -контроля веса ступеней декодирования является выходом устройства. Выходы дешифраторов 5-7 адресов ступеней декодирования и выходы элементов 8-10 совпадения подключены ко входам соответствующих блоков 11-13 вычисления и контроля веса ступеней декодирования. Вход устройства соединен с остальными входами блока 1 адресации ступеней декодировагшя и блока 2 адресации веса ступеней декодирования. Устройство работает следующим образом. На вход блока 1 адресации ступеней декодирования и на элементы 8-10 совпадения поступает. декодирующая импульсная последовательность. С приходом первого импульса последовательности ука- заншг1е блоки приписывают элементу 4 задержки адресный код Д и код веса р. соответственно, С приходом второго импульса первый импудьс со своим адреспьтм кодом А и кодом веса Р поступает на вход дешифратора 5 адреса ступени декодирования первого интервала и блока 11 вычисления и контроля веса ступени декодирования. Срабатывает элемент 8 совпадения, фиксируя мометгг декодирования первого интервала. При декодировании первого интервала блок 11 вычисления и контроля веса ступени декодирования не меняет значения веса Р . При атом второму импульсу последовательности в элементе задержки приписывается адпесный код А2 с весом Р , которые опоз57наются следующим дешифратором 6 адреса декодирования и. блоком 12 вычисления и контроля вера ступени деко дирования. С поступлением последнего им пульса последовательности и импульса с f.. -л. --- адресньтм кодом А весом Р , где 5 - число исправляемых ошибок последовательности, на входьг дешифратора 7 ступени декодирования к блока 13 вычисления и контроля веса ступени декодирования срабатывает элемент 10 совпадения, происходит разрешение декодирования импульсной последовательности блоком 13вычисления и ковггроля веса ступени декодирования, В случае подавления импулы ов последовательности за исключением первого импульса любой из блоков 11-13 вычисления и контроля веса ступени декодирования обнаруживает нулевое значение кода Р,) и не разрешает дальнейшее декодирование, В слу чае подавления первого и пупьса последо вательности устройство не декодирует принятую последовательнссть. На фиг, 2 рассмотрены случаи декодирования четырехту1пульсной последова-гтельности без ошибки (графики 1, 4J, сошибкой подавления одиночного импульса любого, кроме первого (графики 5, 6), В примере приведено подавление второго импульса. График1,-ч8 Hjj/nocTpnpyioT ра боту устройства при подавлении первого импульса последовательности. На графиках 2, 3 внизу от оси введены, обозначения декодируемых величин Р и А в блоках 11 -13 и декомбинаторах 5-7 соответственно. Вверху от оси введены обозначения кодируемых величин Р и А-) на выходах блоков 1 и 2.-. В случае отсутствия ошибок подавления в декодируемой последовательности (грюфик 1) первому импульсу в момент 4- блоками 1 и 2 приписывается в элементе 4 задержки адресный код Л с кодом веса P-j S 1 -С приходом второго импульса в момент ,п коды A-l и Д. поступают на входы дешифратора 5 и блока 11 и происходит декодирование первого интервала (Ьцц.) с по, мсидью элемента 8. При условии декодирования интервала блок 11 не меняет значение кода Р и с помощью блоков 1 и 2 происходит запись в элемент 4 ко дов АЛ и Р . Аналогично происходит 2 декодирование второго, третьего интервалов последовательности, за исклю чением того, что сигнал декодирования всей пос9ледовательности с блока 13 поступает -iffiTШЖ5дГр- ро1стБ1ГГВ случае подавледан ййпупьса сЬДа (см, графики 5 6) декодирование первого интервала прспедовательностй не происходит и блок 11в этом случае изменяет значение кода R) на величину Р - f г -/ . В этот момеиг ( t/j ) в элементе 4 записывается код A,j . Дальнейшее декодирование интервалов последовательности не отличается от случая, представленного на графиках 2,3. В случае подавления импульса последовательности декодирование начинается со второго импульса в момент t (см. графики 7, 8). Через время А и Р декодируются декомбинатором 5 и блоком 11. Блок 11 изменяет значение кода Р на величину и в элементе 4 записываются коды А. Р-( -1- По истечении времени , Р -1 декодирутотся декомбинатором 6 и блоком 12. В блоке 12происходит изменение значения кода на КОД р,. В случае нулевого зна11, как и люр, блок Ч ёНйя Кода бой из блоков 11-13 прекращает дальней;шёе .дакодирбвание последовательности. В случае если декодируемая последовательность состоит из равных интервалов, то устройство будет содержать только по одному элементу 8, декомбинатору 5 и блоку 11. Вероятность правильного декодирова1п1я ойбнивается - спеДувэщбму вмра)Й|НШ). --- - -- у - -р : ГЧ О 5о °° где и - число импульсов последовательности;S- число корректируемых им пульсов; г вероятность перехода J. в б одного элемента послеrft-4K S :i Ss n: V::Sf-- i:J;T---r-.-;::- - -Tl:;Si,. ,- ..-.,.-,----- г--;...-.-. .--. -.. - . - , - .-- - -п ; л ;-:ГП;,:.ЕДС1ватёпьности, . В предоагаемом устройстве Р, с учетом того, что устройство обнаруживает подавление перёого импульса последовательности, ймёёТ Значение : c;p;,a-R ,ПО,989,то превышает эйачение погрешости. .При увеличении требований к РПП выгрыш в использовании предлагаемого

77381

устройства только возрастает. Для умень-1 шенпя вероятности рекомбинаций и подавлений 1 и при увеличении Ррр в предлагаемом устройстве, также как и при других методах декодирования, необходимо5

j.

/ идти по пути возрастания числа импульсов последовательности.

Реализация вновь введенных блоков осуществляется на .уровш функциональHOfi схемы и приводится для случая h 4 и S 1 на фиг. 3 (блоки 11-13) и на фиг. 4 (блок 2).

При поступлении сигнала с дешифратора 5 (6,7) адреса ступе1-ш декодирования на вход 4 одновременно йа входы 1 и 2 фпг. 3 поступает двоичпьтй; код веса Р,( , Для кода веса P.j 9+l соответствует двоичный код 10, для кода веса P-S-код 01 и для веса код . 00. В том случае, если первый интервал декодирован, то происходит декодирование очередногоинтервала на элементе 9 или 10 совпадения и на вхоп 2 (фиг.З) поступает импульс. При этом код веса со входов 1 и 2 с помощью элементов Э1,Э2,Э6, Э8, поступает без изменештй на выходы 1 и 2. Если импульс на вход 2 не при- , щеп,то из кода веса вычитается единица спомощью элементов Э4, ,. §8, &д. Выход 3 Сфиг. 3) является входом уст- 30 ройства, а выходы 1 и 2 подключаются на входы 1 и 2. фиг. 4. На элементах Э1, ЭЗ, Э4 фиг. 4 организована приоритетность входов 1 и 2 над входами 3 и 4 при одновременном появлении инфор- 35 мации на указанных входах. Если на одной иЗ указанных пар -появляется сигнал, то он, проходя через элементы Э2, Э4 и выходы 1 и 2 поступает на входы элемента 4 задержки. Таким образом в эле- мент 4 задержки записывается текущий , код веса. Одновременно сигнал появляет- ся на одном из выходов элементов Э1, Э2 и дальше поступает на вход блока 1 адресации ступеней декодирования, кото- рый по указанному импульсу производит запись в элеК5ент 4 задержки адрес очередной ступени декодирования; формула изобретения

Устройство декодирования импульсной 50 последовательности, содержащее генера98

гор импульсов, выход которого подключен к управляющему входу элемента задержки Vl элементов совпадения и И дешифраторов адресов ступеней декодированияпо числуинтервалов в импульсной последовательности и блок адресации ступеней декодирования, при этом выходы блока адресации ступеней декодирования подключены к первым адресным входам элемента задеряоси, к первым выходам которого подключены входы йротвётствующих дешифраторов адресов ступеней декодирования, выходь каждого из которых подключены к первым входам соответствую- , щих элементов совпадения, вторые входы .элементов совпадения объединены и подсоединены к шине входного сигнала, отличающееся тем, что, с повышения помехоустойгивости, в него введены ti блоков, вычисления и контроля веса ступеней декодирования . и блок адресации веса ступеней декодирова1шя, при этом первые выходьг блока адресации веса ступеней декодирования подключены ко входам блока адресации ступеней декодирования, а вторые выходы подключены ко вторым адресньгм входам элемента задержки,; вторые выходы которого подключень ко входам соответствующих блоков вычисления и контроля веса ступеней декодирования, выходы которых подключены ко входам блока адресации веса ступеней декодирова нйя, выход последнего блока вычисления и контроля веса ступеней декодирования подключен к щине выходного сигнала, выходы дешифраторов адресов ступеней декодирования и выходы элементов совпадения подключены ко входам соответствующих блоков вычис.ления и контроля веса ступеней декодирования выход устpofjcTBa декодирования и блока адресации веса ступеней декодирования.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР N9 515277, хл. Н 03 К 13/00, 08.07.74..

2.Авторское свидетельство СССР № 566348, клГн 03 К 13/22, 22.01.76.

. ;feb--.b;- F

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования импульсной последовательности | 1976 |

|

SU566348A1 |

| Устройство декодирования импульсной последовательности | 1978 |

|

SU741451A1 |

| Устройство декодирования импульсной последовательности | 1978 |

|

SU729837A1 |

| Способ передачи и приема информации и система для его осуществления | 1978 |

|

SU1086446A1 |

| Устройство для контроля параметров полупроводниковых приборов | 1978 |

|

SU781721A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| ИНФОРМАЦИОННАЯ СИСТЕМА СВЯЗИ | 1991 |

|

RU2019851C1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

| СПОСОБ ОЦЕНКИ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2085045C1 |

чг-А ;:;;г й

Авторы

Даты

1980-05-30—Публикация

1978-03-13—Подача