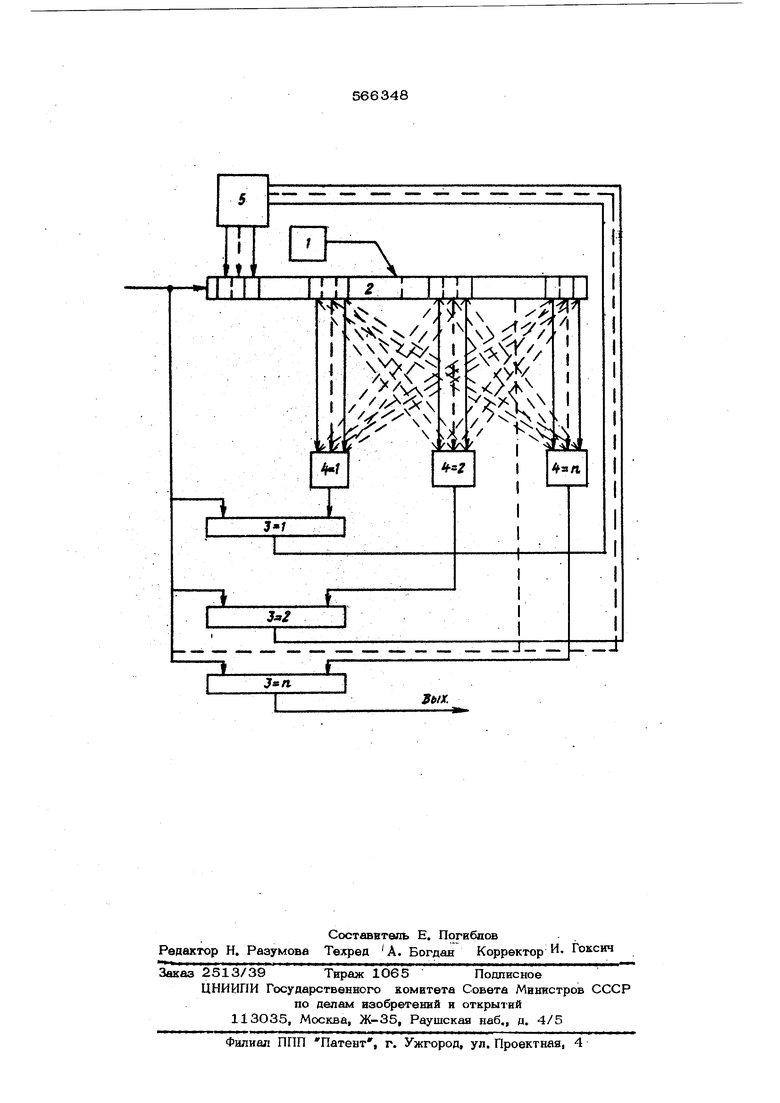

этом выходы блока адресации 5 подключены к адрвсць1м входам элемента задержки 2, к выходам которого подключены входы соответствующих дешифраторов 4 1-4 п , выходы каждого из которых подключены к первым входам соответствующих элементов совпадения 3 1-3«« , вторые входы которых обьеДЕнеяы к подключены к сигнальнск му входу элемента задержки 2, а выходы элементов совпадения п подключены к соответствующим входам блока адреса ции 5 ступеней декодирования. Устройство работает следующим образом Первому импульсу, поступающему на вхо элемента задержки 2, приписывается «адресный код А|( ;соответствующий первому интервалу импульсной последовательности. С приходом второго импульса первый импульс со своим адресным кодом поступает на вхо дешифратора адресов ступеней декодирования. Срабатывает элемент совпадения 3, фиксируя момент декодирования первой ступени в блок адресации ступеней декодирования 5, и второму импульсу приписывается адресный код А который опознается следующим дешифратором . С поступлением на вход элемента задержки 2 последнего импульса последовв1 ельности и прад, последнего импульса с адресным кодом на вход дешифратора 4 п адресов, ступеней декодирования срабатывает дешифратор 4 И и выходной элемент совпадения . Предложенное устройство по сравнению с известным позволяет повысить помехоус.тойчивость передачи информации за счет более эффективного декодирующего алгорит ма. Повышенная эффективность достигается путем адресации каждого входного импульса, что повышает разрешающую способность устройства. Формула изобретения Устройство для декодирования импульсной последовательности, содержащее генератор импульсов, выход которого подключен к управляющему входу элемента задержки и /7 элементов совпадения по числу интерва-, лов в импульсной последовательности, о тличающееся тем, что, с целью повышения помехоустойчивости, введены Jn дешифраторов адресов ступеней декодирования по числу интервалов в импульсной последовательности и блок адресации ступеней декодирования, при этом выходы блока адресации ступеней декСдирования подключены к арресным входам элемента задержки, к выходам которого подключены входь и соответствующих деши4 1аторов адресов ступеней декодирования, выходы кажг дого из которых подключены к первым входам соответствующих п элементов совпадение вторые входы п- элементов совпадения объединены и подключены к сигнальному входу элемента задержки, а выходы п элементов совпадения подключены к соответствующим входам блока адресации ступеней декодирования. Источники информации, принятые во BJUHмание при экспертизе: 1. Авторское свидетельство СССР №515277,кл.:Н 03 К 13/00, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство декодирования импульсной последовательности | 1978 |

|

SU738159A1 |

| Устройство декодирования импульсной последовательности | 1978 |

|

SU741451A1 |

| Устройство декодирования импульсной последовательности | 1978 |

|

SU729837A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| Способ передачи и приема информации и система для его осуществления | 1978 |

|

SU1086446A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1564693A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Многоканальный программируемый генератор импульсов | 1986 |

|

SU1374413A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

Авторы

Даты

1977-07-25—Публикация

1976-01-22—Подача