4. Система для передачи и приема информации, содержащая на центральном пункте блок кодовой адресации, первый вход и выход которого соединены с первыми выходом и входом фо{ ироБателя последовательности синхроимпульсов, второй вход которого подключен к выходу генератора синхроимпульсов, второй выход к первому входу блока кодировани первый выход которого соединен с первым входом передатчика, подключенного к каиаду связи, приемник, выход которого и третий выход формирователя последовательности синхроимпульсов соединены соответственно с первым и вторым входами блока декодирования и регистра вьюода данных, ко второму входу которого и к третьему вхору формирователя последовательности синхроимл льсов подключены соответственно первый и второй выходы блока декодирования, на каждой периферийной станции адресны избиратель, приемник, первый выход которого соединен с первым входом блока декодирования, выходом под кл1оченного к первому входу регистра вьгоода данных регистр ввода данных, первый выход ко торого соединен с первьпу входом блока кодирования, выход которого через передатчик пощслючен к канаду связи, отличающаяся тем, что, с пелью повышения пропускной способности канала связи, в систему на центрадь-дой станций введены регистр ввода данных, генератор адресных сигналов, бяок выделения сигнала наличия информации, первый вход которого подключен к выход приемника, второй вход и выход соединен соответственно с четвертым БЫХ.ОДОМ и входом формирователя последовательности синхроимпульсов, первый и второй выходы генератора адресных сигналов подключены соответственно к вторым входам блока кодовой адресации к передатчика, третий выход - к третьему входу блока декодирования и второму входу блока кодирования, пятый и второй выходы формирователя псюледовательности синхроимпульсов подключены соответст венно к входу генератора адресных сигналов к к входу регистра ввода данных, .выход которого соединен с третьим входом блока кодирования, на каждом периферийном пункте введены генератор импульсов, блок выделения синхроимпуль сов адресов, управляемый формирователь последовательности синхроимпульсов, фильтр, элемент контроля синхроимпульсов адреса и формирователь сигнала наличия информации, выход и первый вход которого подключень оответственно к входу передатчика и к второму выходу регистра ввода данных, второй выход приемника через генератор импульсов подключен к первым входам блока выделения синхроимпульсов адреса и управляемого формирователя последовательности синхроимпульсов, третий выход приемника соединен с первым входом фильтра и с вторым входом блока шлделения синхроимпульсов адреса, выход которого соединен с вторыми входами фшштра и управляемого формирователя последовательности синхроимпульсо(в и с первым входом элемента контроля сшосроимпульсов адреса, выход которого и первый и второй выходы фильтра подключены к входам адресного избирателя, третий выход фильтра соединен с вторыми входами блока кодирования и блока декодирования выход адресного избирателя подключен

к третьему входу управляемого формирователя последовательности синхроимпульсов, первый и второй выходы которого

соединены соответственно с вторыми входами элемента контроля синхроимпуяь сов адреса и формирователя сигнала наличия информации, третий выход - с третьим входом блока кодирования я первым входом регистра ввода данных, четвертый выход - с третьим ех-ощам блока декодирования н вторым входе регистра вьгоода данных.

5, Система по п, 4, о т л и ч а ющ а я с я тем, что формирователь последовательности синхроимпульсов выполнен на элементах -задержки, элементах ИЛИ-НЕ, распределителях на триггерах, блоках задания режима на плементах ИЛИ-НЕ и И-НЕ, выход первого элемента ИЛИ-НЕ через последовательно соединенные триггеры первого распределителя подключен к первым входам первого и второго элементов И-НЕ первого блока задания режима, выход элемента ИПИ-НЕ которого соединен с вторым входом первого элемента И-НЕ, вьрсоды второго и первого элементов И-НЕ первого блока задания режима соединены соответственно с первЬ1МИ входами первого и второго элементов ИЛИ-НЕ, выход последнего из которых через последовательно соединенные триггеры второго распределителя подключен к первым входам элементов И-НЕ второго блока задания режима, выход первого из которых

соединен с вторым входом второгч элемента И-НЕ, выходы йервого и втдрого элементов И-НЕ второго блока задания режима подключены соответственно к вторым входам второго и первого эле ментов ЙЛИ-НЕ, управляющие входы триггеров распределителей соединены с вторым входок- формирователя последовательн ости синхроимпульсотв, выходы каждого триггера первого распределителя непосредственно и через первый элемент задержки подключены соответст Бенно к пятому и четвертому выходам формирователя последовательности синхроимпульсов, вкоды элемента ИЛИ-НЕ первого блока задания режима соединены соответственно с первым и четвертым входами формирователя последовательности синхроимпульсов, третий вход которого подключен к второму входу первого элемента И-НЕ второго блока задания режима, выход каждого триггера второго распределителя непосредственно и через второй элемент задержки соединен соответственно с вторым и третьим выходами формирователя последовательности синхроимпульсов, выход второго элемента И-НЕ второго блока задания режима - с первым выходом формирователя последовательности синхроимпульсов.

6. Систед1а по п. 4, о т л и ч а ю ш а я с я тем, что управляемый формирователь, последовательности синхро10 4пульсов выполнен на элементах ИЛИНН, И-НЕ, элементах задержки, распределителях на триггерах, управляемых блоках задания режимов, выход, элемента ИЛИ-ИЕ через последовательно соединенные триггеры первого распределителя подключен к первым входам первого и второго элементов И-НЕ первого упраэ гаемого блока задания режима, выход первого из которых подключен к второму входу второго и к первому входу элемента ИЛИ-НЕ первого управляемого блока задания режима, выход которого через последовательно соединенные триггеры второго распределителя подключен к первым входам элементов И-НЕ второго управляемого блока задания режима, выход первого из которых подключен к вто рому входу второго элемента И-НЕ, выходы первого и второго элементов И-НЕ второго управляемого блока заданияГ режима соединены соответственно с вторыми входами элемента ИЛИ-НЕ первого управляемого блока задания режима и элемента ИЛИ-НЕ, второй вход управляемого формирователя последовательности синхроимпульсов соединен с первыми управлякнцими входами триггеров распределителей и с вторым входом первого элемента ИЛИ-НЕ второго управляемого блока задания режима, первый вход упраляемого формирователя последоватгельности синхроимпульсов подключен к вторым управляющим входам триггеров распредетштелей, третий вход и выходы каждого триггера первого распределителя через соответствующий элемент И-НЕ объединены и через первый элемент задержки подключены к второму выходу управляемого формирователя последовательности сш1хроимпульсов, третий . которого и выход каждого триггеравторого-распределителя через соотеетст гющий элемент ИЛИ-НЕ объединены и через второй элемент задержки к непосредственно подключены к четвертому и к третьему выходу управляемого формирователя последовательности синхроимпульсов, вы-

-ходы триггеров распределителей - к первому выходу.

7. Система по п. 4, о т л и ч а ющ а я с я тем, что блоки кодирования выполнены на кодере адреса, последовательно соединенных триггерах, сумматорах, триггерах, элементах НЕ, ИЛИ-НЕ и И-НЕ, выходы первого и второго элементов И-НЕ подключены через элемент ИЛИ-НЕ :: выходу блока кодирования, выход третьего элемента И-НЕ через .первый элемент НЕ подключен к первым входам первого и второго сумматоров, выход первого триггера через в-юрой триггер соединен с вторым входом пе| заого сумматора, кыход которого через цепочку из последовательно соединённых триггеров подключен к второму входу второго сумматора, выход которого чере

-последовательно соединенные третий и четвертый триггеры подключен к йервом входу третьего сумматора, к второму входу которого через второй элемент НЕ

подключен выход четвертого элемента И-НЕ, а к выходу подключены входы третьего и второго элементов ,

первый, второй и третий входьт блока кодирования соединены соответственно с объединенными вторыми входами первого, третьего, четвертого и через.второй элемент НЕ с вторым входом второго элемента И-НЕ и с установочными входами триггеров, с входом кодера адреса и с первыми объединенными вхдами первого и четвертого элементов И108.Система по п. 4, о т п и ч а ю1ц а я с я тем, что бшжи декодирования в дпошены на кодере адреса из последовательно соединенных триггерсда, сумматорах, дешифраторе и триггерах, выход первого триггера через второй подключен к первому входу первого сумматора, выход которого через пепочку из последовательно соединенных триггеров соединен с первым входом второго сумматора, выход которого через последова тельно соединенньте третий и четвертый триггеры соединены с первым входом третьего сумматора, вйходы всех триггеров через дешифратор соединены с выхошял блока декодирования, первый вход которого и выход последнего триггера кодера адреса через четвертый сумматор йодключен к второму входу третьего сумматора, выход которого соединен с вторыми входами первого и второго сум маторов и с первым входом первого триггера, установочные входы триггеров соединены с вторым входом блока декодирсяаания, вход первого триггера кодера адреса - с третьим входом блока декодированш. 9.Система по п. 4. о т л и ч а ющ а я с я тем, что формирователь сигнала наличия информации выполнен на последов;ательно соединенных триггерах и группах элементов И-НЕ, первый вход ф«.рмирователя сигнала наличия информапии подключен к первому входу первого элемента И-НЕ в каждой группе элементов И-НЕ, которого соединен с первым входом второго элемента И-НЕ и первым инверсным входом одноименного триггера, второй инверсный вход которого, подключен к выходу второго элемента И-НЕ, второй вход фор шроват ля сигнала наличия информации соединен с вторыми входами элементов И-НЕ и с счетными входа1«1И триггеров, выход по-л следнехч) из которых подключен к выходу формирователя сигнала налич1Ш инфор мации. 6 Ю. Система по п. 4, о т л и ч а ющ а я с я тем, что блок выделения сигнала наличия информации выполнен на последовательно соединенных триггерах и дешифраторе, входы которого соединены с выходами триггеров, а выход - с выходсни блока шлдёления сигнала инфо1 4ации, первый вход которого соединен с инфо{я ационным входом перФого триггера, второй вход - со счетными входами триггеров. 11.Система по п. 4, о т л и ч а ющ а я с я тем, что блок кодовой адресации выполнен на адресных регистрах, последовательно соединенных триггерах и группах элементов И-НЕ, первый вход блока кодовой адресации соединен с первыми входами первого и второго элемента И-НЕ в каждой группе элементов ИНЕ, выход первого из подключен к второму входу второго элемента И-НЕ и к пертому инверсному входу одноименного триггера, второй инверсный вход которого соединен с выходом второго элемента И-НЕ, второй вход блока кодовой адресации подключен к второму входу первого алеменфа каждой группы элементов И-НЕ, к первым входам адресных регистров,к вгормоу входу когорого подключен третий вход блока кодовой адресации,выходы адресных регистров черерез ИЛ И-НЕ соединены с первым клходом блока кодовой адресаци. 12.Система по п. 11, отличающаяся тем, что адресные регистры )выполнены на цепочке из последсжательно соединенных триггеров, на элементах НЕ и триггерах, первый вход каждого триггера непосредственно и второй вход через соответстэукиций элемент НЕ сое. динены с первыми входами адресных регистров, третий и четвертый входы каждого триггера соединены соответственно с прямым и инверсным выходами одноименного триггера в цепочке из последовательно соединенных триггеров, выходы триггеров через элемент И подключены к выходу адресного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для обмена информацией | 1990 |

|

SU1815646A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1140172A1 |

| Устройство для дистанционного контроля защитных потенциалов трубопроводов | 1980 |

|

SU934844A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ТЕЛЕВИЗИОННЫМ ПРИЕМНИКОМ | 1987 |

|

RU2066936C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

1. Способ передачи и приема информации, заключающийся в том, что на центральной станции формируют рекуррентные адресные последователа ности ст налов, передают в канал связи приращения сформированных рекуррентных адресных последовательностей сигналсж, соответствующие адресам периферийных станций, на всех периферийных станциях выделяют переданные приращения рекуррентных адресных поаледовательностей сигналов, восстанавливают по ним сформированные на центральной станции рекуррентные адресные пос юдовательности сштналов, сравнивают восстансналенные рекуррентные адресные пос/юдовательности сигналов с адресной последовательвестью данной периферийной станшт, отличающийся тем, что, с целью повышения таформативности передачи путем увеличения пропускной способности канала связи, при совпадении зйосстаноеленной рекуррентной адресной последовательности сигналов и рекуррент ной адресной постхедовательности данной периферийной станции передают в канал связи сигнал наличия информации на пери ферийной станции, выделяют его на цент ральной станции и задерживают передачу приращения последующей рекуррентной «адресной последовательности сигналов на время передачи инфоряиационной последовательности сигналов с периферийной станции. 2.Способ по п. 1, о т л и ч а ю щ и и с я тем, что, с целью повыщения Постоверности передачи информации, при пеg редаче исходную информационную последовательность сигналов и соответствующую (Л рекуррентную адресную последовательность сигнал«ю преобразуют в одну информационную последовательность Сигналов той же длительности и при приеме производят обратное преобразование в исходную информационную последовательп ность сигналов с использованием соот 00 ветствукщей рекуррентной адресной по05 следовательности сигналов. 3.Способ по п. 1, отличающийся .тем, что при восстановлении о: рекуррентных адресных последовательностей сигналов формируют на периферийных станциях приращения рекуррентных адресных последсиаательностей сигналов, соответствующих приращениям рекуррен-р. ных адресных последовательностей сигналов центральной станции, и осуществляв ют сравнение путем корреляции приращений сформированных- реиуррентных адресных посладсюательностей сигналов и при ращений соответствующих рекуррентных адресных последовательностей сигналов периферийных станций.

Изобретение относится к системам пере-, дачи инфо| мации, касается способа для обjwieHa данными между центральной и перифер Ьюй станциями по многоиунктовьш каналам связи и может, бьггь использовано для обмена данными в реальном масштабе времени по многопунктовым каналам (каналам, pa6oTaiontmvi в многопунктовом режиме) между кентральной станцией и многими удаленными, территориально рассредоточек1л 1ми н пойВ1ш: ными периферийными станшшми в сетях дос-гупа пользователей в электронные вычиспительныг машины и в автоматизированных системах управления, контроля, диспетчеризации различных классов. В основу изобретения положена задача создания способа для обмена данными между центральной и периферийными стан циями путем последовательной во времени передачи адресов периферийных стан- ций в виде элементов рекуррентной последовательности и элементарных сигналов данных. Наиболее близкими по технической сущности и достигаемому результату к изобретению являются способы дяя передачи и приема информации между кентр льной и периферийными станциями, закшочающиеся в том, что на центральной станции генерируют рекуррентные адресные последовательности сигналов, передают в канал связи приращения сформированных рекуррентных адресных последо ватепьностей сигналов, соответствующие адресам периферийных станций, на всех периферийных станциях выделяют передан ные приращения рекуррентных адресных последовательностей сигналов, восстанав ливают по ним сформированные на цент ральной станции рекуррентные адреогые последовательности сигналов, сравнивают восстановленные рекуррентные адрес ше. последовательности сигналов с адресной последовательностью данной периферий:ной станции, причем адресный сигнал представляет д: гхуровневый сигнал с за даваемым значением адресного бита l кли О следукяцими друг за другом рав костоящими. Переходами l и , . Совокупность указанных переходов и уровней содержит информацию адресных . битов, информацию синхронизации периодов адресных битов и информацию синхронизации фиксированного количества , периодов информационных битов в виде регулярных последовательностей. Следовательно, адресный сигнал пред ставляет периодическую адресную последовательность. Элементы этой последова тельности удовлетворяют данной рекур.рентной зависимости. Указанная адресная последовательность охватывает некоторое число М неповторяющахсн иоап.едова.тег5,ностей, обозначающи:;-: asijsca выбранных периферийных станКйй. ГЕосгюйовательности, обозначающие адреса предыдущей и последующей пернфертгйных станпнй, частично пересекают ся. Однако известная система не позволяет э зфективно передавать данные по многойушгтовому каналу при поступлении naHifficc на периферийные станции в случай чие моменты времени. Наиболее близкой к предлагаемой явnstei-ся система передачи и приема информации, содержащая на центральн 4 nyiiKTe блок кодовой адресации, первый вход и выход которого соединены с первымг вькодом и входом формирователя .последовательности синхроимпульсов, второй вход которого подключен к выходу генератора синхроимпульсов, второй выход - к первому Ьходу блока кодирования, первый выход которогчэ соединен с пер-. вым выходом передатчика, подключенного к связи, приемник, выход которого и третий выход формирователя последоват-еяьности синхроимпульсов соединен соответственно с первым и вторым выходами бло1са декодирования к регистра вывода да.ннь2х, к второму входу которого н к. третьему входу формирователя поспедоБательности сшхроимпульсов подключены соответственно первый и второй выходы декодирования, блок сравнения, блок управления, ключи, распределитель, на каждой периферийной станции адресный избиратель, приемник, перБЬ7й выход которого соединен с першыми входом блока декодирования, выходом пой.--;.шоч;энкого к первому входу регистра вывода данных, регистр ввода данных, первый выход которого соединен с Bxonotvs бяока кодирования, выход которого через передатчик подключен к канаяу связи, управляемые ключи 3j . Дшгная система также не обладает большой шформацконной емкостью и не .. позволяет э4эфективно передавать данные по многонунктоьому каналу связи. Целью изобретения является повышение шформативиостк передачи информации между центральной и периферийными станциями путем увеличения пропускной способности канала связи, а более конкретно увеличение часпа обсдуживаемых перифер1 й1пых станций, уменьшение времени доставки данных при их передаче в реальном масщтабе времени по многопунктным каналам, снижение затрат на передачу данных, достижение высокой верности передачи данных. Поставленная цель достигается тем, что при соытадении восстановленной рекуиэентной адресной последовательное ти сигналов и рекуррентной адресной последовательности данной периферийной станшга передают в канал связи сигнал наличия информации на периферийной . сташши, выделяют его на центральной станции и задернгавают передачу приращения последующей рекуррентной адресвой пЪспедовательности сигналов на вре мя передачи информапионной последовательности сигналов с периферийной станшт. С целью повышения достоверности ле редачи инфо и 1ашга, при передаче исходную информационную последовательность сигнаясш и соответствующую рекуррент ую адресную последовательность сигналов преобразуют в одну последовательность сигналов той же длительности и при приеме производят обратное преобразование в иcxoдti7ю информационною последовательность сигналов с использованием соответствующей рекуррентной адресной последовательности сигналов. При восстановлении рекуррентных адресшлх последовательностей сигналов формируют на периферийных станциях прирашения рекуррентных адресных последовательностей сигналов соответст-и еуюших прирашениям рекуррентных адрес ных носледовательностей центральной станции и осушествляют сравнение путем корреляции приращений сформированных рекуррентных а{фесных последовательностей сигналов и приращений соответствукицих рекуррентных адресных noследовательностей сигналов периферийных станций. Кроме того, в систему на центраяь к й станции введены регистр ввода данных, генератор адресных сигналов, блок выделения сигнала наличия информации, вход которого подключен к выхо приемника, второй вход и выход соединен соответсовенно с четвертыми выходс н входом формирователя последовательности синхроимпульсов, первый и второй выход генератора адресных сигналов под 1шючёнь1 соответственно к вторым входам блока. Еюдовой адресации и передатчика, третий выход - к третьему входу блока декодирования и второму входу блока ко ПИрования, пятый и второй выходы формирователя последовательности синхрОп импульсов подключены соответственно к входу генератора адресных сиггталов и к входу регистра ввода данных, выход которого соединен с третьим входом блока кодирования, на каждой периферийной станции введены генератор импульсов, блок выделения синхроимпульсов адресов, управляемый формирователь последова тельности синхроимпульсов, фильтр, элемент контроля синхроимпульсов адоеса и формирователь сигнала наличия информации, выход и первый вход которого подключены соответственно к входу передатчика и к второму выходу регистра ввода данных, второй выход приемника через генератор импульсов подклкпен к первым входам блока выделения синхроимпульсов адреса и управляемого формирователя последовательности синхроимпульсов, третий выход прие-чника соединен с первым входом фильтра и с вторым входом блока выделения синхроимпульсов адреса, кыход которого соедннен с вюрыми выходами фильтра и управляемого формирователя последовательности синхроимпульсов и с первым входом эле мента контроля синхроимпульсов адреса, выход которого и первый и второй выходы фильтра подключены к входам адреснсйго избирателя третий выход фильтра соединен с в-йфыми входами блока К(-дирования и блока декЬдир жания, выход адресного избирателя подключенк третьему входу управляемого формирователя последовательности синхроимпульсов, первый и второй выходы котор нх соединены соответственно в вторыми входами элемента контроля синхроимпульсов адреса и формирователя сигнала наличия информации, третий выход - с третьим входом блока декодирования и первым входсйл регистра вывода даншых, четвертый выход - с третьим входся блока кодирования и втсфым входом регистра ввода данных. Формирователь последовательности синхроимпульсов выполнен на элементах задержки, элементахИЛИ-НЕ, распредели-г т элях на триггерах и блоках задания режима на элементах ИЛИ-НЕ, выход первого элемента ИЛИ-НЕ через последовательно соединенные триггеры первого распределителя подключен к первым входам первого и вочэрого элементов И-iiE первого блока задания режима, выход элемента ИЛИ-НЕ которого соединен с вторым входом первого элемента И-НЕ, выход которого подключен к второму входу второго элемента И-НЕ, выходы Iвторого и первого элементов И-НЕ первого блока задания режима соединены соответственно с первыми входами первого и второго элементов ИЛИ-НЕ, выход последнего из которых через последовательно соединенные триггеры второго распределителя подклкяен к первым входам элементов И-НЕ второго блока задания режима, выход первого из которых соединен с вторым входом второго элемента И-НЕ, выходы первого и вто рого элементов И-НЕ второго блока задания режима подключены соответственно к вторым входам второго и первого элементе® ИЛИ-IiE, управляпощяе входы триггеров распределителей соединены с вторым входом формирователя последова тельности синхроимпульсов, выходы триггера первого распределителя непосредственно и через первый элемент задержки подЕшючены соответственно к пятому и четвертому выходам формирова теля последовательности синхроимпульсов, входы элемента, первого блока задания режима соединены соответственно с первым и четвертым входа ми формирователя последовательности синхроимпульсов, третий вход которого подключен к второму входу первого элемента И-НЕ второго блока задания режима, выход каждого триггера второго распределителя непосредственно и через второй элемент задержки соединен соответственно с вторым и третьим выходаMB формирователя последовательности синхроимдульссхв, выход второго элемента И-НЕ второго блока задания режима - с выходом формирователя последовательности синхроимпульсов. Управляемый формирователь послеДоватешэности синхроимпульсов выполнен также на элементах ИЛИ-НЕ, И-НЕ, элементах задержки, распределителях на триггерах, управляемых блоках задания режима, выход элемента ИЛИ-ЛЕ через последовательно соединенные триггеры первого |}аспре делителя лодвлючен к пер вым входам первого и второго эл:е1«ленто И-йЕ первого управляемого блока задаН11Я режима, выход первого из которых подклкучен к второму входу второго и к первому входу элемента ИЛИ-НЕ первого управляемого блока задания режима выход которого через последовательно соединенные триггеры второго распределителя подключен к первым входам элементов И-НЕ второго управляемого блок задания режима, выход первого из которых подключен к второму входу второго элемента И-НЕ, выходы первого и второго элементов И-НЕ второгх управляемо-го блока задания режима соединены соответственно-с вторыми входами элемента ИЛИ-НЕ первого управляемого блока задания режима иэлемента ИЛИ-НЕ, второй вход управляемого формирователя последовательности синхроимпульсов соединен с первыми управлякяцими входами триггеров распределителей и с вторым входом первого элемента ИЛИ-НЕ второго управляемого блока задания режима, первый вход управляемого рм«- рователя последовательности синхроимпульсов подключен к вторым управляющим входам триггеров распределителей, третий вход и выходы каждого триггера первого распределителя через соответствующий элемент И-НЕ объединены и через первый элемент задержки подключены к второму выходу управляемого формирователя последовательности синхроимпульсов, третий вход которого и выход каждого триггера второго распределителя через соответствукиций элемент ИЛИ-НЕ обьедтшены и через второй элемент задержки и непосредственно подклк чены к четвертому и к третьему выходу управляемого формирователя последовательности синхроимпульсов,выходы триггеров распределителей - к первому выходу. Блоки кодирования выполнены н коде. ре адреса, последовательно соединенных триггерах, сумматорах, триггерах, элементах НЕ, ИЛИ-НЕ, И-НЕ, выходы первого и второго элементов И-НЕ подктпочены через элемент ИЛИ-НЕ к выходу блока кодирования, выход третьего элемента И-ЛЕ через пе1жый элемент НЕ подключен к первым входам первого и второго сумматоров, выход первого трш гера через второй триггер соединен с вторым входом первого сумматора, выход которого через цепочку из последовательно соединенных триггеров подшпо чен к BTOpca iy входу вторсою сумматора, вькод которого через последовательно соединенные третий и четвертый триггеры подключены к первому входу третьего сумматора, к второму входу которого через второй элемент НЕ подключен четвертого элемента И-НЕ, а к выходу подключены входы третьего и второго элементов И-НЕ, первый, вггорой и третий входы блока кодирования соепв- йены соответственно с обьединешолми вторык и входами первого, третьего, четвертого и через второй элемент НЕ с вторым входом второго элемента И-Н и с установочными входами тригтеров, с входом кодера адреса и с первыми объединенными входами первого и че-зувертсго элементов И-НЕ. Бае1си11екодирования также выполнены на кодере адреса из последовательно соед ненных триггеров, сумматорах, дешифраторе/ и триггерах, выход первого трйЬ гера Через второй подключен к первому входу первого сумматора, выход которого через цепочку из последовательно со диненных триггеров соединен с первым восодом втсфого сумматора, выход которого через последовательно соединенные третий и четвертый триггеры соединены с первым входом третьего сумматора, выходы всех триггеров через дешифратор соед1шены с вы содо1л блока декодирования, первый вход которого и выход последнего триггера кодера адреса через четвергай сумматор подключен к второму влюду третьего сумматора, выход которого соединен с вторыми входа ми первого и второго сумматоров и с первым входом первого триггера, установочные входы триггеров соединены с vfOpOM входом блока декодирования, вход перйвсйРО триггера кодера адреса с третьюл входом блока декодирования. Формирователь сигнала наличия информации выполнен на последовательно соединенных триггерах и грухЕпах элемен те И-НЕ, первый вход формирователя сигнала наличия информашш подключен к входу первого элемента И-НЕ в каждой группе элементов И-НЕ, вько которого соединен с первым входом вто рого элемента И-НЕ первым инверсным входом одноименного триггера, второй инверсный вход которого подключен к выходу второго элемента И-НЕ, второй вход фор,4ирователя сшшала наличия инфс виашш соединен с вторыми входами элементов и со счетюлми входами триггеров, выход последнего из которых подключен к выходу формирователя сигнала наличия информации. выделения сигнала наличия ин ормааия выполнен на последовательно соединенных триггерах и дешифраторе, входы которого соединены с выходами триггеров, выход подключен к выходу блока выделения сигнала наличия инфор шш, первый вход которого соединен с информационным входом первого триггера, второго вход - со счетными входами триггеров. Блок кодовой адресации выполнен . на адресных регистрах, последовательно соединенных триггерах и группах элементов И-НЕ, первый вход блока кодовой адресации соединен с первыми входами первого и второго элемента И-НЕ в каждой группе элементсхб И-НЕ, выход первого из которых подключен к входу второго элемента И-НЕ и к первое му инверсному входу одноименного трш гера, второй инверсный вход которого соединен с выходом второго элемента И-НЕ, второй вход блока кодовой адресации подключен к второму входу перветч) элементй И-НЕ каждой группы элементов И-НЕ, к первым входам адресных регистров к второму входу которосю поаклрючены третий вход блока кодоааой адресации, выходы адресных регистре через элемент ИЛИ-НЕ соединены с первым выходом блока кодовой адресации. Ащюсные регистры выполнены на ав. почке из последовательно соединенных триггеров, на элементах НЕ и триггерах, первый вход каждого триггера непосредственно и второй вход через соответс вующий элемент НЕ соеданены с первыми входами адресных регистров, третий и четвертый входы каждого триггера соединены соответственно с прямым mmepcным выходом одноименного трврпрера в цепочке из последовательно соещшенншк триггеров, выходы триггеров через эле.мент И подключены к выходу ащ)еснаго регистра. На фиг. 1 изображена блок-схема центральной станции системы для пер©-. дачи данных между оентраяыюй и пе|жферийными стЕШЦиями согласно too peтению; Hai фиг. 2 - то же, периферийной станции, на фиг. 3 - функционально-, принципиальная схема формирователя пен спедовательности синхронизирующих тлпульсов; на фиг.. 4 - то же, управляемого формировате ш после довательностн синхроимпульсов; на фиг. 5 - то ж, блока кодирования и регистра ввода яовных; на фиг. б - то ЖЕ, блока декоднрования и регистра вывода данных; на фиг, 7 - принципиальная схема фо1 ирователя сигнала наличия инфор|{ации на фиг. 8 - выполнение блока выделения сигнале наличия инфор ации, на фиг. 9 .пошшшхаальная схема блока кодовой а; ресадви, на фиг; 10 - временные диаграммы, поясняющие процесс обмена данными между централькыми и периферийными станциями.

Система для обмена данными между центральной и периферийными станциями содержит на центральной станции генератор 1 (фиг. 1) адресных сигналов, вырабатьшаюший адресный сигнал в виде последовательности, элементы конторой удовлетворяют заданной рекуррентной зависимости и которая охватьшает некоторое число М неповторяющихся последовательностей, обозначающих адреса вы инных периферийных станций, связанный с ; входом 2 блока 3 кодовой адресацки, предназначенным для сравнения нак«мшенных последовательностей с адре с м 1 выбранной периферийной станции и для выработки разрешения на прием и/нЛй передачу данных с/на выбранную перифери ную станцию в случае совпадения накопленной поипоспеловательности с адресом выбранной периферийной станции. Вход 4 блока является входом адресов вводимых йанйых а его выход 5 является выходом адресов, выводимых с центральной станции. . Схема содержит также на центральной станции регистр 6 ввода данных, вход 7 которого является информационным вам рю/м центральной станции, а выход соединен с входом 8 блока 9 кодирования, выход которогю подключен к входу 10 передатчика 11, Вход 12 передатчика 11 п /дключен к выходу генератора 1, а его выход 13 является сигнальным выходом центральной станции.

На центральной сташши содержится регистр 14 вывода данных, выход 15 которого является информационным иыходом центральной сташши, вход 16 под- соединен к выходу блока 17 декодирования. Вход 18 блока 17 декодирования подсоединен к выходу приемника 19, вход 2О которого является сигнальным вкодом центральной станвди.

В дополнение к перечисленным бпо, кам на центральной станции содержится генератор 21 синхроимпульсов, предназначенный для выработки выбранной peiyЯяркоЪ сетки тактовых частот, формирователь 22 последовательности синхронизирующих импульсов, предназначенный для определения зависящих от случаййох .Лотоков данных нерегулярных отрезков времени между следующими друг за дру- гом элементарными сигналами акресав и для выработки соответствующей этим отрезкам последовательности с1юдующих

друг за другом синхронизирующих импульсов адреса и синхронизирующих импульсо данных. Вход 23 формирователя 22 подсоединен к выходу блока 3 кодовой адресации, вход 24 - к выходу генератора 2 выкоду синхронизирующих импульсов данг ных. Вход 23 формирователя 22 подсоединен к выходу блока 3 кодовой адр&сации, вход 24 - к выходу генератора 2 выход синхронизирующих импульсов передаваемых данных формировате131 22 соединен со входом 25 регистра 6 ввода данных и с входом 26 блока 9 кодирования, -Выход синхронизирующих импульсов принимаемых данных формировате ля 22 подсоединен к входу 27 регист- ра 14 вывода данных и к входу 28 блока 17 декодирования, выход синхронизирующих импульсов адреса этого формирователя 22 подсоединен к входу 29 генератора 1 адресных сигналов.

На центральной станции между выходом приемника 19 (фиг. 1)и выходом формирователя 22 включен блок 30 вььделения сигналов наличия информации, синхронизирующий вход которой подсоединен к выходам синхронизирующих импульсов распределителя 31 (фиг.З) через блок выделения сигнала наличия информации 30 временной задержки, а. выход бдока 30 соединен с другим входом элемента ИЛИ-НЕ 32 (фиг. 3).

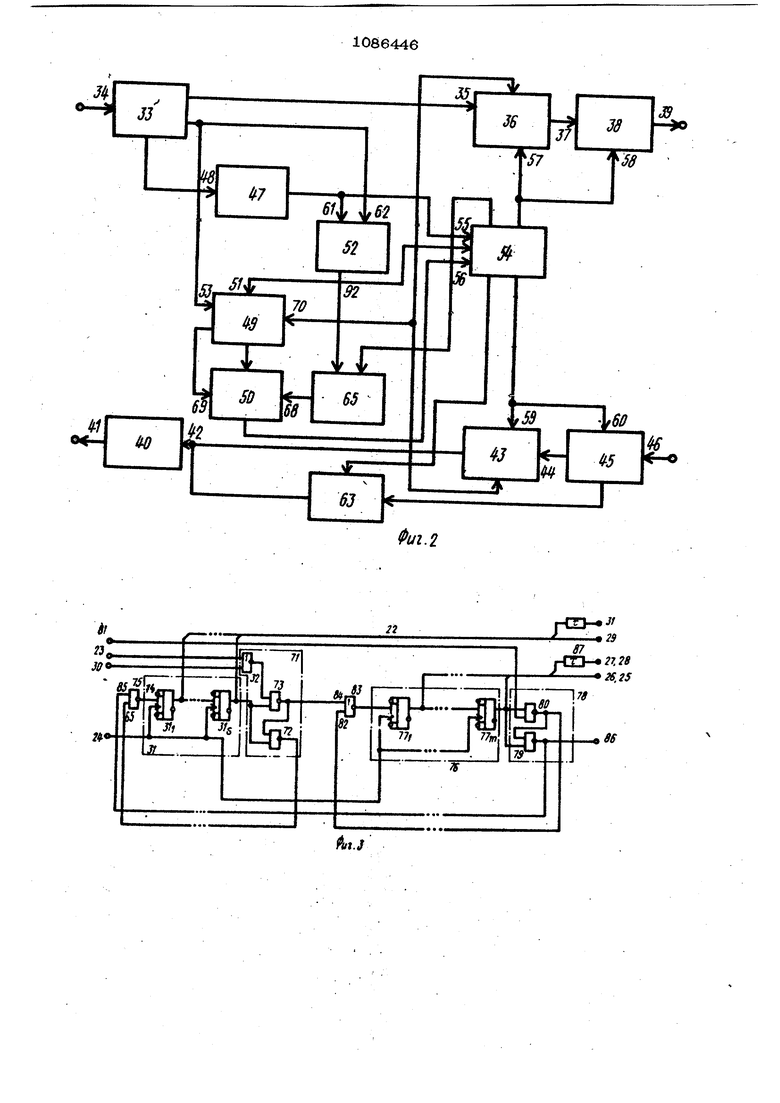

периферийная станция содержит приемник 33 (фиг. 2), вход 34 которого является сш нальным входом периферийной станции, выход подсоединен к входу 35 блока 36 декодирования, выход блока 36 подсоединен к входу 37 регистра 38 вывода данных, а выход 39 регистра 38 является информационным выходом периферийной стйнции.

Каждая периферийная станция содержит также передатчик 40, выход 41 которого является сигнальным выходом перн- ферийной станции, а выход 42 подсоединен к выходу блока 43 кодирования. Вход 44 блока 43 подсоединен к выхо ду регистра 45 ввода данных-. Вход 46 Гегистра 45 является информационным входом периферийной станции.

В дополнение к перечисленным . кам на каждой периферийной станции имеется синхронизируемый генератор 47 импульсов, вход 48 которого соединен с выходом приемника 33, фильтр 49, выде шющий рекуррентную последовательность, выходы которого соединены с соответствующими входами адресного

избирателя 50. Вход 51 фильтра 49 подсоединен к выходу блока 52 выцеления синхроимпульсов адреса, вход 53 фильтра 49 соединен с выходом приемника 33.

На каждой периферийной станции име ется управляемый формирователь 54 последовательности синхронизирующих импульсов, вход 55 которого подсоединен к выходу синхронизируемого генератора 47импульсов, вход 56 подсоединен к разрешающему ы 1ходу адресного избирателя 5О. Выход синхронизирующих импульсов принимаемых данных управляемого формирователя 54 подсоединен

к входу 57 блока 36 декодирования и к входу 58 регистра 38 вывода данных. Выход синхронизирующих импульсов передаваемых: данных управляемого формирователя 54 соединен с входом 59 бло ка 43 кодирования и с входом 60 регистра 45 ввода данных.

Вход 61 блока 52 объединен с входом 55 управляемого формирователя 54 и подсоединен к выходу синхронизируемого генаратора 47 импульсов, вход 62 блока 52 йодсоединен к выходу приемника 33.

На каждой периферийной станции между дополнительным выходом регистра 45 (фиг. 2) ввода данных и перецарчиком 40 включен формирователь 63 сигнала наличия информации, синхронизирующий вход которого подсоединен к выходам элементов И-НЕ 64|, ..., 64д (фиг, 4) управляемого формирователя 54 через элемент 63 задержки. Кроме этого, на каждой периферийной стёнции имеется элемент 65 контроля синхроимпульсов адреса, соединенного с выхорами распределителей 66 и 67, (фиг. 4) управляемого формирователя 54. Выход элемента 65 (фиг. 2) соединен с входом 68 адресного избирателя 5О, второй вход 69 которого соединен с выходом фильтра 49, выделяющего рекурренные последовательности, другой выход 7 последнего соединен одновременно с блоком 43 и 36.

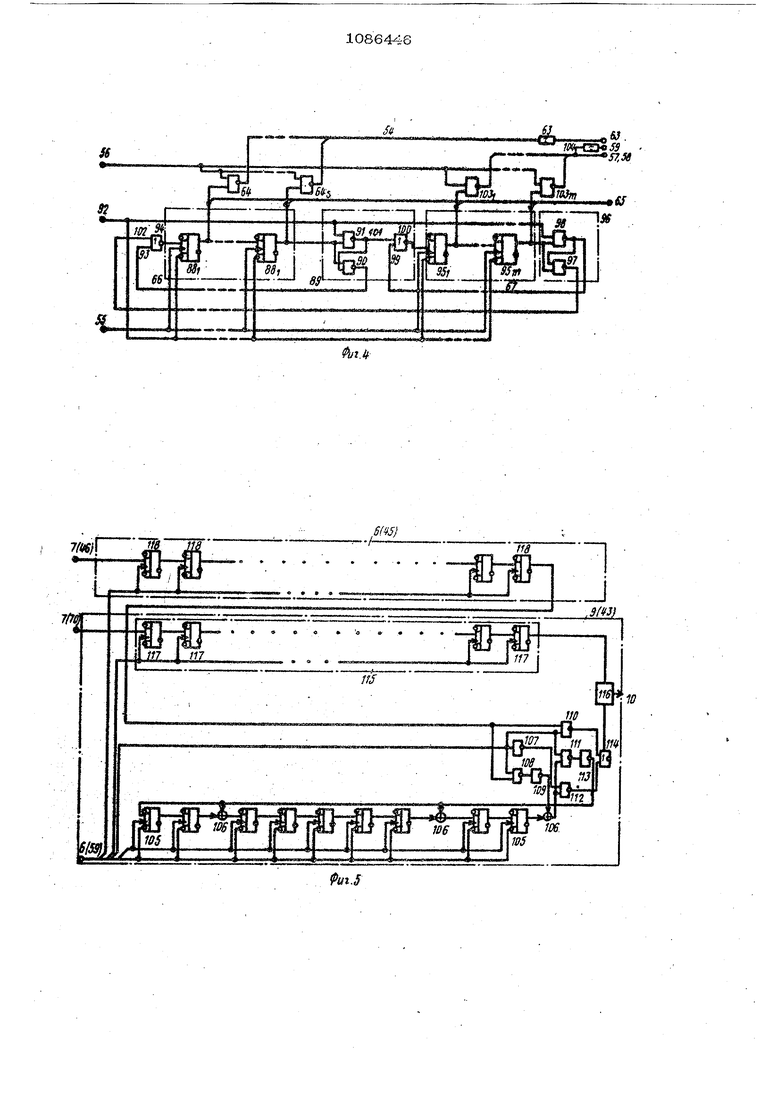

На центральной станции формирова-тель 22 последовательности синхронизирующих импульсов содержит распредели.тель 31 (фиг. 3) импульсов, вырабатывающий синхронизирующие импульсы адреса, включающий последовательно сое/шшенные триггеры 30,..., 30.

Формирователь 22 содержит таюке баок задания режима 71, определяющий условие начала передачи данных, включающий элементы И-НЕ 72, 73 и , ИЛИ-НЕ 32. Один вход элемента ИЛИНЕ 32 подсоединен к выходу блока 3 (ф}пг. 1) кодовой адресации, а выход подключен к одному входу элемента ИНЕ 73 (фиг. 3), другой вход которого объединен с одним из входов элемента И-НЕ 72 и подключен к выходу триггера 31g распре делителя 31. Другой вход элемента И-НЕ 72 подсоединен к кьткоду элемента И-НЕ 73. Выход элемента И-НЕ 72 подсоединен к входу 74 элемента ИЛИ-НЕ -75. Выходы синхронизирующих импульсов распределителя 31 . подсоединены к входу 29 генератора 1 (фиг. 1) рекуррентной последовательности.

Формирователь 22 содержит также р,аслределитель 76 (фиг. 3) импульссиа, вырабатьшающий синхронизируюшне импульсы данных, включающий последовательно соединенные триггеры 77-t ,...77,

«Формирователь 22 содержит блок за Дания режима 78, определяющий условие повторения и окончания передачи данных, включающий элементы И-НЕ 79 н 80. Один вход элемента И-НЕ 80 соединен с выходом 81 (фиг. 1) блока 17 декодирования, другой его вход объединен с одним входом элемента И-НЕ 79 (фиг.З) и подсоединен к выходу триггера 77|. Другой вход элемента И-НЕ 79 подсоединен к выходу элемента И-НЕ 80, соединенному с входом 82 элемента ИНЕ 80, соединенному с входом 82 элемента ИЛИ-НЕ 83. Вход 84 элемента ИЛИ-НЕ 83 соединен о выходом элемента И-НЕ 73 и Подсоединен s входит элемента И-НЕ 72, выход элемента ИНЕ 79 соединен с входом 85 элемента ИЛИ-НЕ 75 и с входом 86 (фиг. 1) блока 3 кодовой адресации .Выход элемента ИЛИ-НЕ 75 подсоедиен к одному из входов триггера 21 распределителя 31.

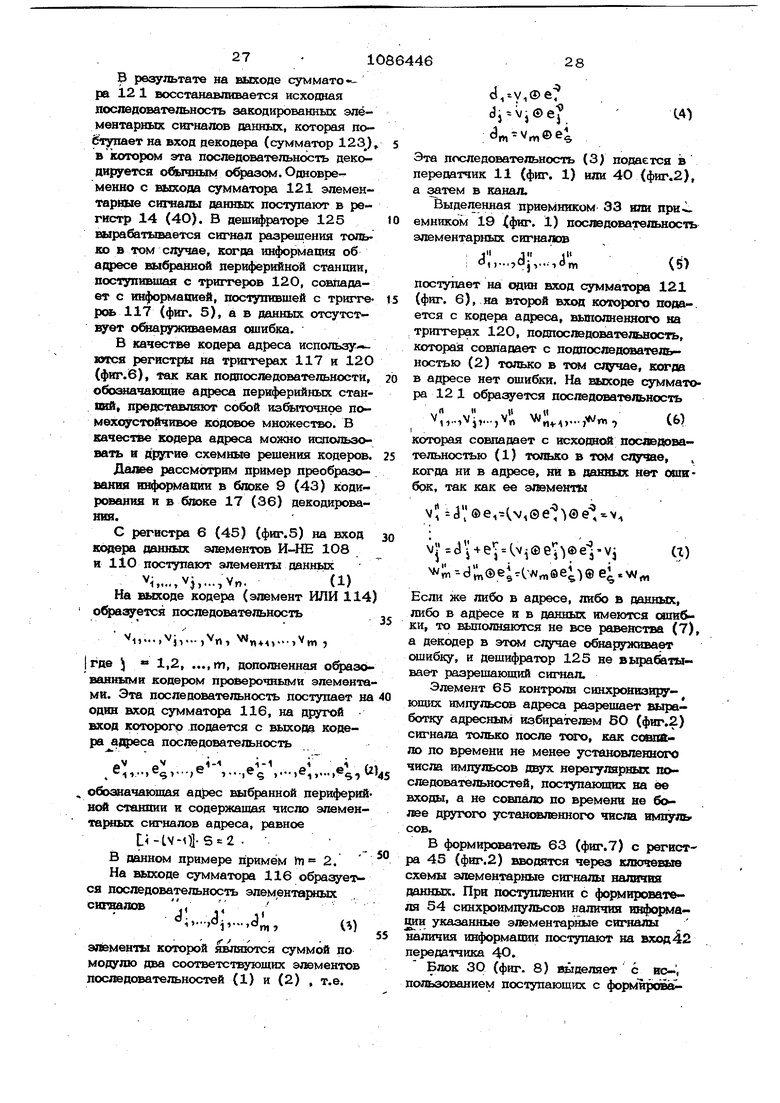

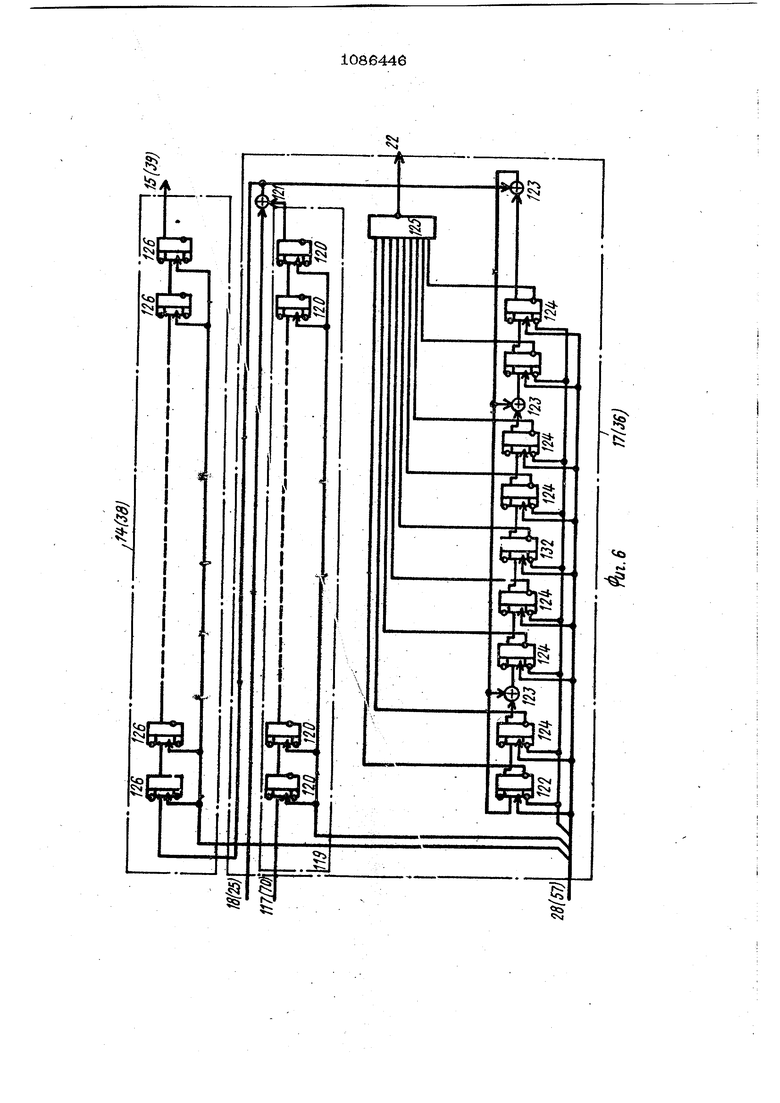

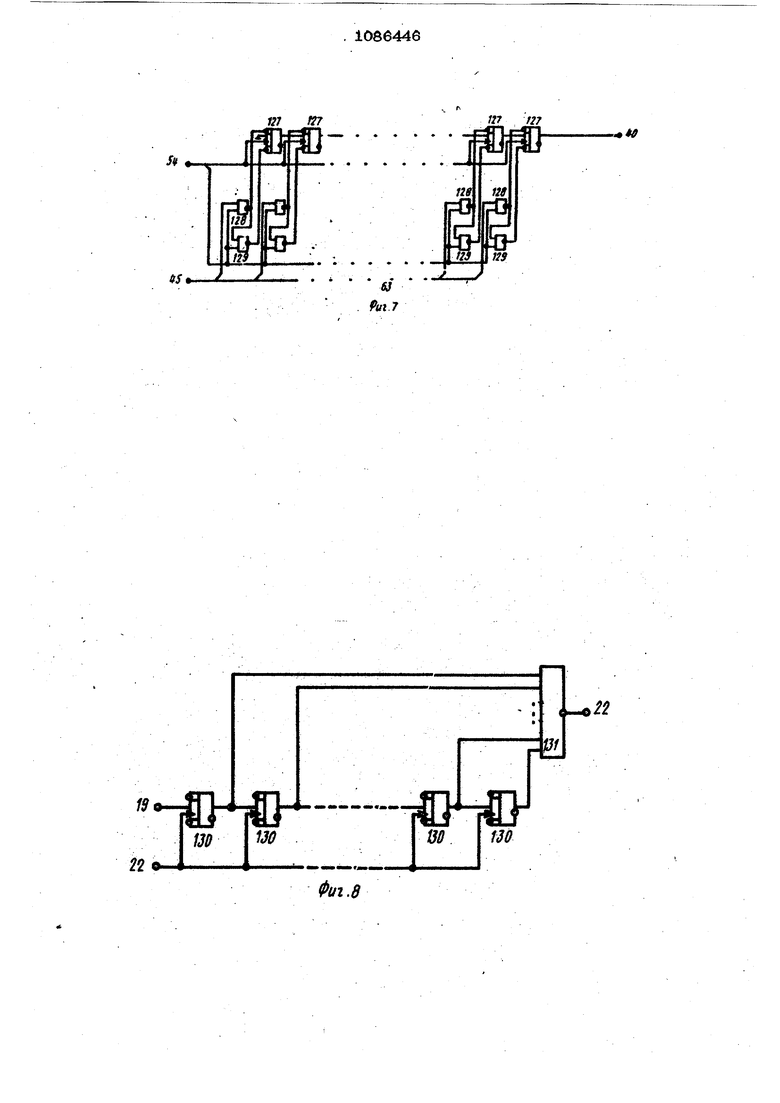

Выходы синхронизирукяцих импульсов данных распределителя 76 (фиг. 3) подсоединены к входам 25 и 26 (фиг. 1) регистра 6 ввода данных и блока 9 кодирования соответственно и через элемент 87 (фиг. 3) задержки подключены к входам 27 и 28. (фиг. 1) регистра 14 вьтоцд данных и блока 17 декодирования соответственно. Синхронизирующие входы распределителей 31 и 76, являющиеся входом 24 (фиг. 1) формирователя 22 подсоед1шены к выходу генератора 21 сю1хронизйрующнх импульсов. 15 Hia кажоой периферийной станции управляемый формирователь 54 (фиг. 2) последовательности синхронизирующих импульсов содержит распределитель 66 (фиг. 4), вырабатъшающий синхронизи рующие импульсы адреса и включающий последовательно соединенные тригге-ры 88 , ... 885 . Управляемый формирователь 54 содержит также управляемый блок задания режима 89, включающий элементы И-НЕ 9О и 91. Один из входов элемента 9О объединен с одним входом элемента ИНЕ 91 и подсоединен к выходу триггера 88. Другой вход элемента И-ЙЕ 91 подсоединен к выходу 92 (фиг. 2) 52. Выход элемента И-НЕ 90 (фиг. 4) подсоединен к входу 93 элемента ИЛИ-ЛЕ 94, выход которого подсоединен к одному входу триггера 88. Управляемый формирователь 4 содержит также распределитель 67, включакшшй прследовате:г&но соединенные триггеры 95 (, ... 95 щ, управляемый блок задания режима 96, включающий элемен1ы И-НЕ 97 и 98. Один из входов элемента И-НЕ 98 подсоединен к выходу 92 (фиг. 2) блока 52, другой вход элемента И-НЕ 98 объединен с одним из входов элемента И-НЕ 97 и подсоединен к выходу триггера 95. Другой вход элемента И-НЕ 97 подсоединен к ыях-опу элемента И-НЕ 98 сое диненному с входом 99 элемента ИЛИНЕ 1ОО, вход 101 которого подключен невыходу элемента 91 и к входу элемента И-НЕ 90. Въкод элемента И-41Е 97 подсоединен к входу 102 цемента ИЛИ-НЕ 94. Синхронизирующие входы распределителей 66 и 67, 51вляющиеся входом 55 (фиг, 2) управляемого формировате.: ля 54, по(юоединены к выходу синхронизируемого генератора 47 импульсов, установочные входы распределителей 66 и 67 (фиг. 4) подсоединены к выходу 9 блока 52 (фиг. 2} въщеления синхроимпульсов адреса. Вь1ходы распределите- ля 66 (фиг. 4) подсоединены к одним входам элементов И-НЕ 64, ... , 64с Выходы распределителя 67 подсоединены к одним входам элементов И-НЕ 103 |, ... , 103 tn I выходы которых подсоединены к входам 57 (фиг. 2) бло ка 36 декодирования и к входам 58 регистра 38 вьшода данных соответственн и через элемент задержки 104 (фиг. 4) 1 46 лодключены jt входам 59 и 6О (фиг. 2) блока 43 кодирования и регистра 45 ввода данных соответственно. Другие входы элементов И-НЕ 641, ..., 64$ (фиг. 4) и lO3f, ... , 1ОЗ , обра гющне вход 56 (фиг. 2) управляемого форсирователя 54, подсоединены к выходу адресного избирателя 5О. Блок 43 (фиг.2) кодирования выполнен аналогично блоку 9 кодирования (фиг.5) I,Блок 9 (фиг. 5) кодирования содер-, .жит кодер, вьшолнешшй на триггерах 105 с сумматорами 106 в пепнх обратной связи, включающий элемент управления на элементах НЕ 1О7, И-НЕ 108 112, НЕ 113 и ИЛИ-НЕ 114, а также последовательно соединш1ные кодер адреса 115 и сумматор 116 ио модулю два. К одному аз входов сумматора 116 подключен выход элемента ИЛИ-НЕ 114. Выход сумматора 116 подключен к выходу элемента ИЛИ-41Е 114. Выход сумматора 116 соединен с входом 10 (фиг. 1) передатчика 11. Кодер адреса 115, например, ваьшолнен на триггерах 117 и соединен с соответствующим выходом (фиг. 1) генератора 1. Выход кодера ащэеса 115 соединен с втор(ЫМ входом сумматора 116. ВыхОд регист--. ра 6 (фиг. 1) ввода даншых, вътолнен- .ный на триггерах 118, соединение входом элементами И-НЕ 108 в НО. На центральной станции используется несколько регисторс® 6, Блок 33. (фиг.2) выполнен аналогично блоку 17 декодирования. В блок 17 (фиг. 6} декодирования введены последовательно соединенные кодер адреса 119, выполненный на триггерах 12 О, и сумматор 121 по модулю два. Ошш из входов сумматора 121 по;ь соединен к выходу приемника 19. Выход сумматора 121 подсоединен к входу 16 регистра 14 вывода данных и к входу декодера , выполненного на триггерах 122 с сумматорами 123 - в обратной свази, другие входы декодера подсоединены к соответствующему выходу генератора 1 (фиг. 1) импульсов, формирующих рекуррентную последователь кость. Выходы 124 триггеров 122 подключены к дешифратору 125, выход которого соединен с формирователем 2Z (фиг. 1). Выход сумматора 121 подсоединен к входу регистра 14 въюода дан-. ных, выполненного на триггерах 126. Регистр 35 (4яг. 2) вывода данных выполнен аналсоично.

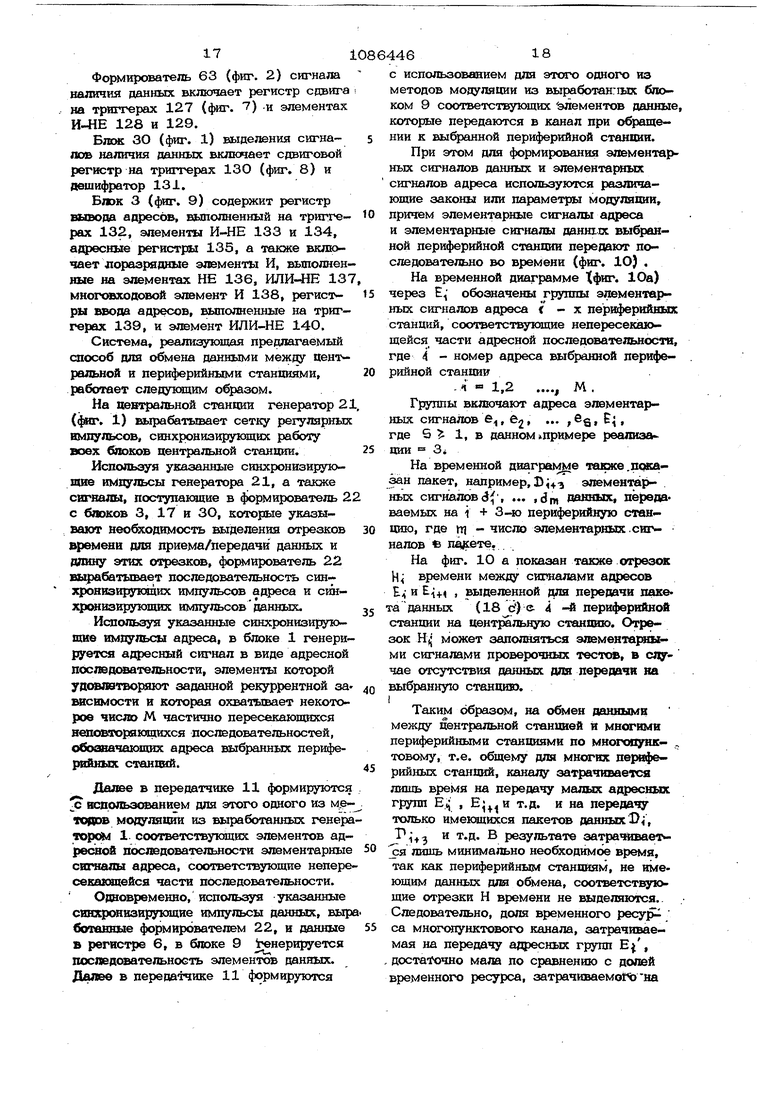

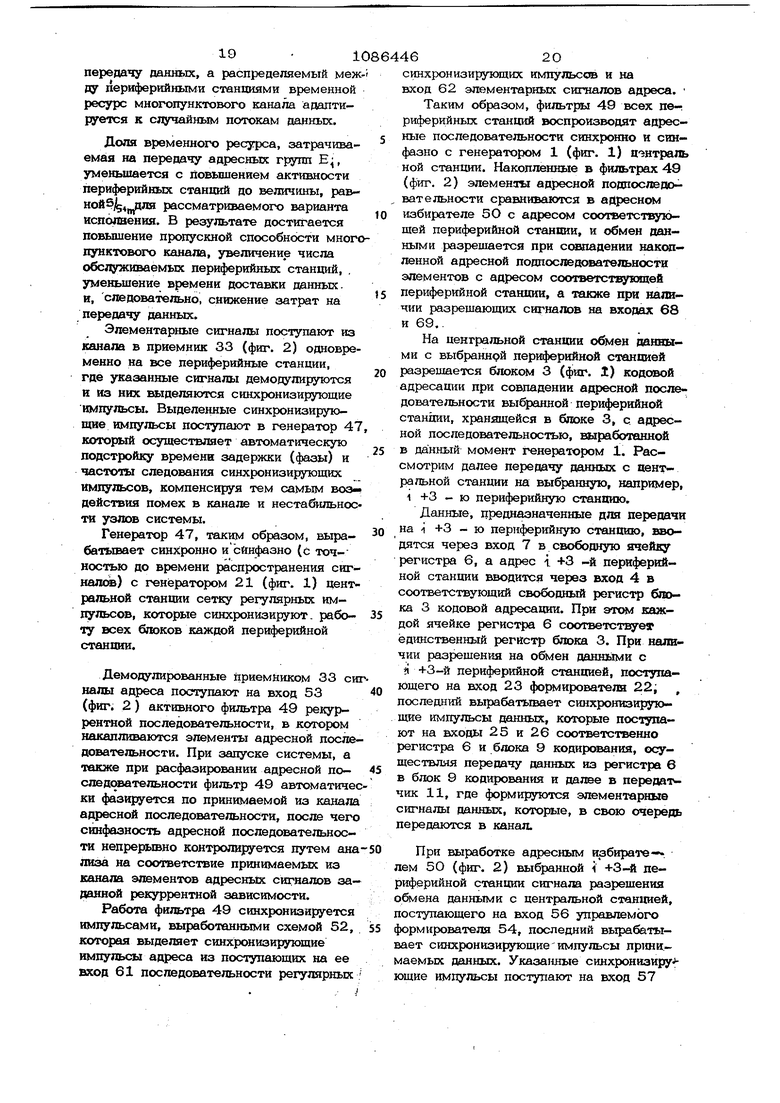

Формирователь 63 (фиг. 2) сигналю наличия данных включает регистр сдвига на триггерах 127 (фиг. 7) -и элементах И-НЕ 128 и 129.

Блюк ЗО (фиг. 1) выделения сигнапав наличия данных включает сдвиговой регистр на триггерах 130 (фиг. 8) и дешифратор 131.

Блок 3 (фиг. 9) содержит регистр вывода адресов, выполненный на триггеpax 132, элементы И-НЕ 133 и 134, афесные регистра 135, а также включает лоразрядные элементы И, выполненные на эдаментах НЕ 136, ИЛИ-ИН 137 многювходовой элемент И 138, регист ры ввода адресов, выполненные на триггерах 139, и элемент ИЛИ-НЕ 140.

Система, реалигг ющая предлагаемый способ для обмена данными между центральной и периферийными станциями, работает следующим образом.

На центральной станции генератор 21 («г, 1) вырабатывает сетку регулярных импульсов, синхронизирующих работу всех блоков центральной станции.

Используя указанные синхронизирующие генератора 21, а также сигналы, поступающие в формирователь 2 с блоков 3, 17 и ЗО, которые указывают нео&содимость выделенна отрезков )«|енв для приема/передачи данных и дтшу этих отрезксш, формирователь 22 вырабатывает последовательность синхронизирующих импульсов адреса и сшхрсжизируюших импульсовданных.

Используя указанные синхронизирующие импульсы адреса, в блоке 1 генерируется агдресный сигнал в виде адресной посяедстательности, элементы которой уд(ЖЛ9Творнют заданной рекуррентной за симости и которая охватывает некоторое число М частично пересекающихся неповагорякяцихся последоватешзностей, обоавачающих адреса выбранных перифертОоолл сфанхщй.

Далее в передатчике 11 формируются с ясдользсяоанием для этого одного из м еvoflpB модуляции из выработанных генератор Яи 1 соответствующих элементов адресжой последовательности элементарные сигналы адреса, соответствующие непересекающейся части последовательности.

Одновременно, используя указанные свнхрсжизирующие импульсы данных, вырботанные формирователем 22, и данные в регистре 6, в блоке 9 ;«нерируется последовательность элементов данных. Далее в передатчике 11 формируются

с использованием для этого одного из методов модуляции из выработанных блоком 9 соответствующих Цементов данные которые передаются в канал при обращении к выфанной периферийной сташши.

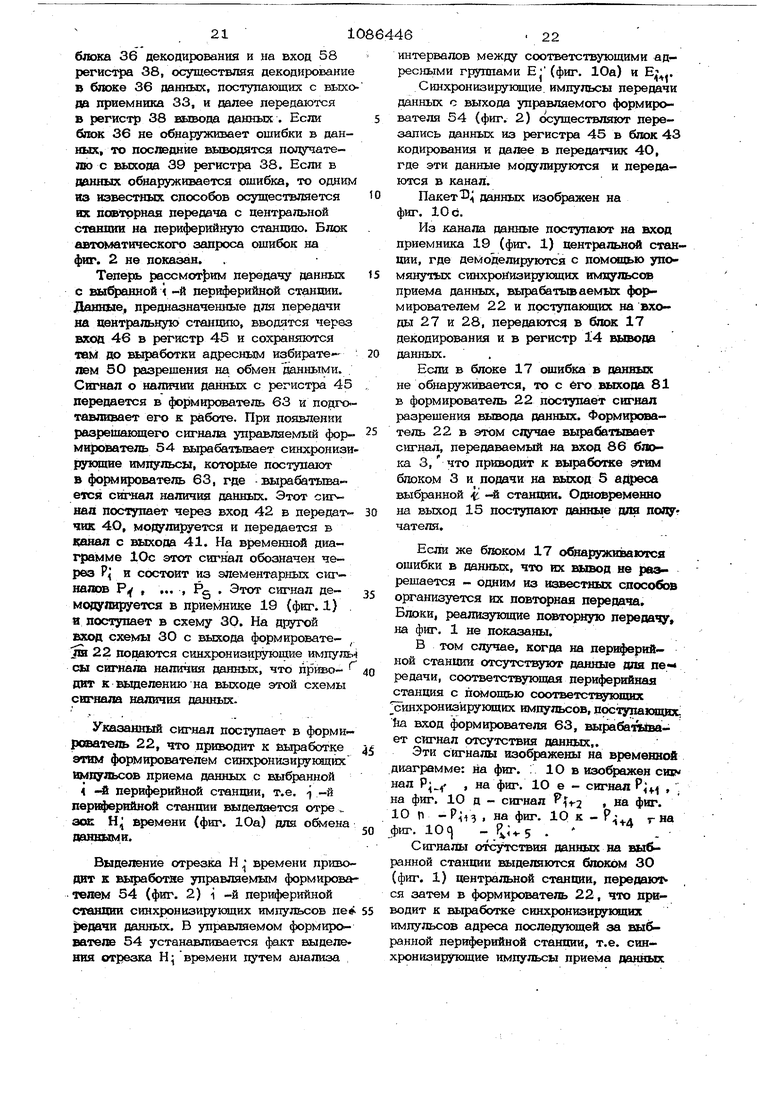

При этом для формирования элементарных сигналов данных и элементарных сигналов адреса используются различающие законы или параметры модуляции, причем элементарные сигналы адреса и элементарные сигналы данних выбранной периферийной станции передают последовательно во времени (фиг. Ю) .

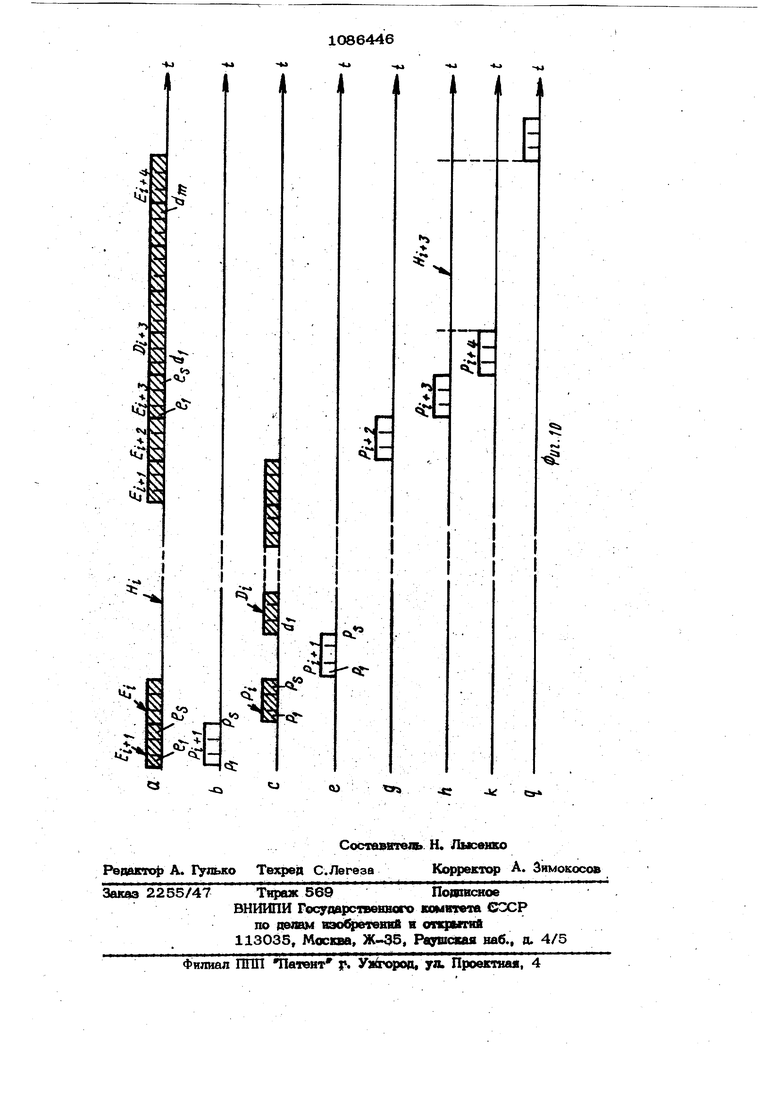

На временной диаграмме Хфиг. 1Оа) через обозначены группы элементарных сигналов адреса ( - х периферийных станций, соответствующие HenepeceKiaioщейся части адресной последовательности, где 4 - номер адреса выбранной периферийной станции

-ч в 1,2 ...., М.

Группы включают адреса элементарных сигналов е, 62, ... ,6s, Е, где S 1, в данном примере реализа ции 3i

На временной диаграмме чеааюв ,пок&зан пакет, например, элементарных сигналов {, ... ,ijp, данных, переда ваемых на | + 3-ю периферийную станцию, где гп - число элементарных .сигнатюв «1 .

На фиг. 1О а показан также отрезок Н времени между сигналами адресов Е;( и , выделенной цля передачи паке таданных (18 с) е 4 -Л периферийной станции на центральную станцию. Отрезок Н,; может заполняться элемента;)ми сигналами проверочных тестев, в сяучае отсутствия данных для передачи на

выбранную станцию. I

Таким образом, на обмен данными между центральной станцией и многими периферийными станциями по мнагоауик- товому, т.е. общему для многих пе жферийных станций, каналу затрачивается лишь время на передачу меилых адресшык групп Е , т.д. и на передачу только имеющихся пакетов данных Di, Р и т.д. В результате затрачивает Ъя лишь минимально необходимое время, так как периферийным станциям, не имеющим данных длш обмена, соответствующие отрезки Н времени не шлделяются.. Следовательно, доля временного ресур са многотунктового канала, затрачиваемая на передачу адаесных групп , , достаточно мала по сравнению с долей временного ресурса, затрачиваемойна передачу данньгх, а распределяемый меж ду периферийными станциями временной ресурс многопунктового канала адаптируется к случайным потокам данных. Доля временного ресурса, затрачиваемая на передачу адресных групп Е, уменьшается с повышением активности периферийных станций до величшпы, равнoй5|| ля рассматриваемого варианта исполнения. В результате достигается повышение пропускной способности много пунктового канала, увеличение числа обслогживаемых периферийных станций, , уменьшение времени доставки данных. и, следовательно, снижение затрат на передачу данных. Элементарные сигналы поступают из канала в приемник 33 (фиг. 2) одновременно на все периферийные станции, где указанные сигналы демодулируются и из них выделяются синхронизирующие импульсы. Выделенные синхронизирующие импульсы поступают в генератор 47 который осуществляет автоматическую подстройку времени задержки (фазы) и частоты следования синхронизирующих импульсов, компенсируя тем самым воздействия помех в канале и нестаСлшьнос ти узлов системы. Генератор 47, таким образом, вырабатывает синхронно и сйнфазно {с точностью до времени распространения сигналов) с генератором 21 (фиг. 1) центральной станции сетку регулярных имх льсов, которые синхронизируют, работу всех блоков каждой периферийной станции. Демодулированные приемншсом 33 си налы адреса поступают на вход 53 (фиг. 2) активного фильтра 49 рекуррентной последовательности, в котором накапливаются элементы адресной после довательности. При запуске системы, а также при расфазировании адресной последовательности фильтр 49 автоматиче ки фазируется по принимаемой из канала адресной последовательности, после чего синфааность адресной последовательности непрерывно контролируется путем ана лиза на соответствие принимаемых из канала элементов адресных сигналов заданной рекуррентной зависимости. Работа фильтра 49 синхронизируется импульсами, выработанными схемой 52, которая выделяет синхронизирующие импульсы адреса из поступающих на ее вход 61 последовательности регулярньк синхронизирующих импульсов и на вход 62 элементарных сигналов адреса. Таким образом, фильтры 49 всех пе-г риферийных станций воспроизводят адресные последовательности синхронно и сйнфазно с генератором 1 (фиг. 1) цэнтраль ной станции. Накопленные в фильтрах 49 (фиг, 2) элементы адресной подпоследовательности сравниваются в адресном избирателе 5О с адресом соответствующей периферийной станции, и обмен данными разрешается при совпадении наксш- лвнной адресной подпоследстательности элементов с адресом соответствующей периферийной станции, а также при наличии разрешающих сигналов на входах 68 и 69.. На центральной станции обмен данными с выбранной периферийной станцией разрешается блоком 3 (фиг. 1) кощавой адресации при совпадении адресной последовательности выбранной периферийной станции, хранящейся в блоке 3, с адресной последовательностью, выработанной в данный момент генератором 1. Рассмотрим далее передачу деишых с центральной станции на выбранную, например, 1 +3 - ю периферийную станцию, Данные, предназначенные для передачи на -i +3 - ю периферийную станцию, вводятся через вход 7 в свободную ячейку регистра 6, а адрес i +3 -и периферийной станции вводится через вход 4 в соответствующий свободный регистр блока 3 кодовой адресации. При этом каждой ячейке регистра 6 соответствуез единственный регистр блока 3. При наличии разрешения на обмен данными с i +3-Й периферийной станцией, поступающего на вход 23 формирователи 22; , последний вырабатывает синхронизирующие импульсы данных, которые поступают на входы 25 и 26 соответственно регистра 6 и блока 9 кодирования, осуществляя передачу данных из регистра 6 в блок 9 кодирования и далее в передат чик 11, где формируются элементарные сигналы данных, которые, в свою очередь передаются в канал. При выработке адресным избирателем 50 (фиг. 2) выбранной i +3-й периферийной станции сигнала разрешения обмена данными с центральной станцией, поступающего на вход 56 управлемого формирователя 54, последний вырабатывает синхронизируюш.ие импульсы пр1шимаемых данных. Указа1шые синхронизиру ющие импуш сы поступают на вход 57 блока 36 декодирования и на вход 58 регистра 38, осуществляя декодирование в блоке 36 данных, поступающих с вых да приемника 33, и далее передаются в регистр 38 вывода данных . Если блок 36 не обнаруживает ошибки в данных, то последние вьшодятся получателю с выхода 39 регистра 38. Если в данных обнаруживается ошибка, то одним из известных способов осуществляется их повторная передача с центральной станшга на периферийную станюию. Блок автсжютического запроса ошибок на фиг. 2 не показан. Теперь рассмот|)им передачу данных с ч -и перЕн юрийной станини. Дашше, предназначенные для передачи на центральную станцию, вводятся через вход 46 в регистр 45 и сохраняются там до млработки адресным избирателем 50 разрешения на обмен данными. Сигнал о наличии данных с регистра 45 передается в фо1 /1иро ватепь 63 и подго тавливает его к работе. При появлении разрешакздего сигнала управляемый фор мирователь 54 вырабатывает синхронизи рующие импульсы, которые поступают в формирователь 63, где -вырабатывается сигнал наличия данных. Этот сигнад поступает через вход 42 в передат чик 4О, модулируется и передается в №Яйп с выхода 41. На временной диа Юс этот сигнал обозначен через Р и состоит из элементарных сигналов Р , ,., , PQ . Этот сигнал демодугааруется в приемнике 19 (фиг. 1) и поступает в схему 3Q. На другой вход схемы 30 с выхода формироватепя 22 подаются синхронизирующие импуя сы сигнала наличия данных, что приводит к выделению на выходе этой схемы сигнала наличия данных. Указанный сигнал поступает в формирователь 22, что приводит к выработке этим формирователем синхронизирующих вмцуяьсов приема данных с выбранной i -и периферийной станции, т.е. -j -и периферийной станции выделяется отре ЗОЕ Н времени (фиг. 10а) для данными. Выделение отрезка н времени приво дит к выработке управляемым формирова телем 54 (фиг. 2) i -и периферийной станции синхронизирующих импульсов пе редачи данных. В управляемом формирователе 54 устанавливается факт выделе ния отрезка Н времени путем анализа интервалов между соответствующими адресными группами (фиг. 1Оа) и Е.. Синхронизирующие импульсы передачи данных с выхода управляемого формирователя 54 (фиг. 2) осуществляют перезапись данных из регистра 45 в блок 43 кодирования и далее в передатчик 40, где эти данные модулируются и передаются в канал. Пакет 13 данных изображен на фиг. 10 d. Из канала данные поступают на вход приемника 19 (фиг. 1) централы станции, где деМоДелирутотся с помсяцью упомянуоых синхроИизирукнцих импульсов приема данных, вырабатываемых формирователем 22 и прступакяцих на входы 27 и 28, передаются в блок 17 декодирования и в регистр 14 вывода данных. Если в блоке 17 ошибка в данных не обнаруживается, то с его выхода 81 в формирователь 22 поступает сигнал разрешения вывода данных. Формирователь 22 в этом случае вырабатывает сигнал, передаваемый на вход 86 блока 3, что приводит к выработке этим блоком 3 и подачи на выход 5 адреса выбранной 4 - станции. Одновременно на выход 15 поступают данные для попуг чателя. Если же блоком 17 о&шружквакхгся ошибки в данных, что их вывод не разрешается - одним из известных способов организуется их повторная передача, Блоки, реализующие повторную передачу, на фиг. 1 не показаны. В том слртЕае, когда на периферий.ной станшга отсутстщгюг данные для пе«редачи, соответствующая периферийная станция с псшощью соответствующих инхронизирующих импульсов, поступаюащх, ha вход формирователя 63, вырабатлйвает сигнал отсутствия данных,. Эти сигналы изображены на временной иаграмме: на фиг. : 10 в изображен CHIN ал , на фиг. 1О е - сигнал , а фиг. 1О д - сигнал 2 . на фиг. 1О п - на фиг. 10 к - Р д г на иг. ЮС) -. . . Сигналы отсутствия данных на вы анной станции выделяются блоком 30 (фиг. 1) центральной станции, передаю1 я затем в формирователь 22, что приодит к выработке синхронизирукицих мпульсов адреса последующей за выбанной периферийной станции, т.е. синронизирующие импульсы приема данных с выбранной периферийной станции не вырабатываются а, следовательно, ей не выделяется отрезок времени даю обмена паяными, В этом случае, когда имеются данные и на выбранной периферийной станции и на центральной станпии для этой выбранной периферийной станции, указан ные данные передаются дуялексно. Процессы передачи данных в к&жщам налрав лении независимы и аналогичны описанным. Рассмотрим подробнее вопросы обеспечения высокой верности при передаче цанкьщ в системе по предлагаемому способу. Прежде всего необходимо обеспечить высол то верность передачи адресных си налов, так как на каждый адрес приходится малое количество элементарных адресных сиг1юлов е,, ,е(фиг.1.0 Это достигается тем, что на станциях, с которых передаются данные, помимо элементарных сигналов адреса информация об адресе выбранной периферийной станции вводится в блоках 9 (фиг. 1) или 43 (фиг. 2) допол1ительно в пакеты D данных путем соответствующего кодир жания, не изменяя содержания данных и длины пакета D . На станции на которой принимаются эти данные, путем соответствуклдего де кодирования в блоках 17 (фиг. 1) и 36 (фиг. 2) разделяются данные и адрес периферийной станции. Указанный адрес сравнивается с адресом выбрашоЙ периферийной станции в блоках 17 , (фиг.1) или 36 (фиг. 2) декодирования которые вырабатывают сигнал разрешения вывода данных только в случае совпадения адресов. При этом указанная информация об адресе может подвергать ся помехоустойчивому кодированию в блоках 9 (фиг.1) или 43 (фиг.2), что дополнительно увеличивает верность пеpeasnf адресных сигналов. Высокая верность передачи адресных сигналов достигается также тем, что в качестве фильтра периферийных станШШ использован активней фильтр рекуррентной последовательности, в котором гене рируется адресный сигнал в виде последовательности, аналогичной последовате .ности, генерируемой генератором 1 (фиг.1) Центральной станции, Дале в блоке 49 (фиг. 2) перемножается этот адресный сигнал на выделенный приемни ком 33 адресный сигнал центральной станции, а результат перемножения используется для синфазирования и cmixpo-« нирования активного фильтра 49. При этом в адресном избирателе 5О вырабатывается разрешение на данными только при наличии поступакхцего на вход 69 сигнала в синхронном и синфазном режиме активного фильтра 49. Высокая верность передачи адресных сигналов достигается дополнительно тем, что количество элементов в адресных последовательност51х, накапливаемых в фильтре 49 периферийных станций k обозначакицих адреса периферийных станций, принимаются больше минимального чис ла N элементов непсеторякяцихся последовательностей, а количество элементов в адресных группах Е (фиг.Юа), здесь ,2, М, принимают равным или большем единицы. Благодаря описанному, последовательности, обоЖ1ачаюшие адреса периферийных станций, избыточное помехоустойчивое кодовое множество. Высокая верность передачи адресных сигналов достигается еще и тем, что на каждой периферийной станции в управляемом фо|Ж1ирователе 54 (фиг.2) вырабатывается разрешенная последовательность синхронизирующих импульсов адреса, соответствующая используемым в системе форматам адресных групп Е (фиг. 10а) н пакетов D . Эта разрешенная последовательность в схеме 65 (фиг.2) сравнивается с выде юнным блоком 53 последовательностью синхронизирующих импульсов адреса,и схема 65 формирует разрешакяций сигнал, который поступает на вход 68 адресного избирате- -ля 5О. Адресный избиратель разрешает обмен данными только при наличии тако го разрешающего сигнала, тем самым до стигается з ицита от ошибок THtia вставок и выпаданий элементов. Сл&довател|ьно, по предлагаемому способу наряду с достижением высокой пропускной способности многопунктового канала обеспечивается высокая верность передачи данных, конкретнее - передачи адресных сигналов. Рассмотрим далее работу отдельных блоков системы. Работа формирователя 22 (фиг.З) основана на управлении распределителем 31, вырабатъюаюшим С1шхронизирующие импульсы адреса и синхронизирующие импульсы наличия данных, и распределителем 76, вырабатывакицем синхронвзи-. 251 рующие импульсы приема/передачи данны с помощью блока задания режима 71 и 78. Блок 71 обеспечивает путем яод клкяения выхода триггера 31 на вход тргапгера 77 выделение отрезка времени для приема/передачи данных, если на входы элемента ИЛИ-41Е 32 поступают соответствующие сигналы с выхода блока 3 (наличие данных от центральной . станции) и/или с выхода блока ЗО выоелвнкя. сигнала налич данных. Блок 7 (фиг.З) обеспечивает по связи между элементами И-НЕ 72,ИЛИ-НЕ 75 выработку синхрсшизирутащих импульсов посавауютего адреса, если на входы схемы ИЛИ-НЕ 32 не поступают соответст вуюшие сигналы. Блок 78 обеспечивает по связи между элементами И-ИЕ 79 и ИЛИ-НЕ 75 выработку синхронизирующих импульсов последующего адреса, если на вход элемента И-НЕ 80 поступает разрешающий сигнал с блока 17 (фиг.1) декодировани и повторную выработку через связь между элементами И-НЕ 80 и ИЛИ-НЕ 83 синхронизирующих импульсов данных если на вход э;юменга И-НЕ 80 сиптл jHe поступает. С выхода элемента И-НЕ 79 пос1рта ет сигнал на вход 86 блока 3(фнг.1) коскжой адресашга, разрещающий считывание адреса. Работа управляемого формирователя 5 (фиг. 4) основана на управлении распределителем 66, вырабатывающим синхронизируюпше импульсы наличия данных, : распределителем 67, выраба-пьшающим ;им1гуяьоы-, Приема/передачи данных с поплатью управляемых блоков задания ре тла 89 и96 и с помсншью управляющих сигналиж, поступающих на установочные входы триггеров 8Q, .... 8851 95й, с блока 52 (фиг. 2). Блок 89 (фиг.4) обеспечивает путем подключения выхода триггера 88 к входу триггера 95/(f выработку синхронизирукяцнх импульсов приема/передачи данвых, если на вход его схемы И-НЕ 91 поступает выделенный блоком 52 (фиг.2 сиюфсжвзирующий импульс адреса, и вы работку с использованием связи между элементами И-НЕ 9О и ИЛИ-НЕ 94 синхронизирующих импульсов наличия ПВШШХ для последующей станции, если Еаыяеоенный синхронизирующий импульс адреса поступает на вход элемента И-4Ш 91 (фиг. 4) 46 Блок 96 обеспечивает с использованием связи между элементами И-НЕ 97 и ИЛИ-НЕ 100 повторную выработку синхронизирующих импульсов приема/передачи данных, если на вход элемента И-НЕ 98 He поступает выделенный синхронизируйщий импульс адреса. Если такой синхронизирующий импульс поступает, то с использованием связи между элементом И-НЕ 97 и ИЛИ-НЕ 94 блок 96 обеспечивает выработку синхронизирующих импульсов наличия данных для последующей станции. Соответствующие синхронизирующие импульсы, обеспечивающие обмен данными для выделенной периферийной станции, формируются только при условии наличия разрешающего сигнала на входе Б6, что обеспечивается с помощью элементов И-НЕ 645-, -. 6%. 103, . 103. С выходов триггеров 88/5, ... , 8&с, и с выходов некоторых триггеров 95(,,и ..., 95fY, снимается также разрещенная последовательность синхронизирующих импульсов адреса и синхронизирующих импульсов данных, которая поступает на элемент 65 (фиг.2). Указанные некоторые триггеры 95,,, ... , задаются в аавнсимости от используемых в системе форматов адресных групп и форматов пшштов данных. Особенностью варианта блока 9 (43) (фиг. 5) кодирования является то, что в нем последовательность данных с выхода кодера данных (элемента ИЛИ-НЕ 114 ) суммируется по модулю два в сумматоре 116 с информацией об адресе выфанной периферийной станаии, закодированной кодером адреса. Таким образом, поступающие на входы 10 (42) передатчиков элементарные сигналы представляют сумму по модулю два соответствующих элементарных сигнашэв данных и элементов информации об адресе.. На фиг. 6 представлен вариант выпоп нения блока 17 (43) декодирования, работающий при обмене данными между станциями с блоком 9 (43) кодирования (ф№.5) . Особенностью блока 17 (36) являет ся то, что поступающие на его вход 18 (44) элементарные сигналы подаются на вход сумматора 121, на второй вход которого поступает информация об адресе выбранной периферийной станции, закодированная кодером адреса, выполненным на триггерах 120, В результате на выходе сумматора 12 1 восстанавливается исходная лоследовательность закодированных элементарных сигналов данных, которая пойгупает на вход декодера (сумматор 123) в котором эта последовательность декодируется обычным офазс. Одновременно с выхода сумматора 121 элементарные сигналы данных поступают в регистр 14 (4О). В дешифраторе 125 ЕЫрабатываеох я сигнал разрешения только в том случае, когда информация об адресе выбранной периферийной станции, поступившая с триггеров 12О, совпадает с информацией, пос1у1гавшей с тригге роь 117 (фиг. 5), а в данных отсутствует о шруживаемая сяиибка. В качестве кодера адреса используются регистры на триггерах 117 и 12 О (фиг.6), так как подпоследовательности, обо шчаюшие адреса периферийных станШ1Й, представляют собой избыточное помехоустойчивое кодсФое множество. В качестве кодера адреса можно использовать и другие схемные решения кодеров. Далее рассмотрим пример преобразования ийфсфмаоии в блоке 9 (43) кодирования и в бпсже 17 (36) декодирования. G регистра 6 (45) (фиг. 5) на вход кодера данных элементов И-НЕ 1О8 и 110 поступают элементы данньк ь-.-ЛЬ-Л ; На выходе кодера (элемент ИЛИ 114 o6f aaiyeTcfl последовательность ) + 5 где J 1,2, ...,т, дополненная офазо ванными кодером проверочными элемента ми. Эта последовательность поступает на один вход сумматора 116, на другой шсод которогр .подается с выхода кодера афеса последовательность Ге:;,......, ,...,6 ,...,е,,,..,6, обозначающая адрес выбранной периферий ной станции и содержащая число элементарных сигналов адреса, равное L -tV-O. 2 2 . В шином примере примем Ит 2. На выходе сумматора 116 обра ется последовательность элементарных сигналов j( , о.-,3,...,сЗ,(г) элементы которой являются суммой по модулю два соответствующих элзментов последовательностей (1) и (2) , т.е. (3j vj®ej Эта последовательность (3) подастся ъ передатчик 11 (фиг. 1) или 40 (фиг.2), а затем в канал. Выделенная приемником 33 шш при емником 19 Хфиг. 1) последовательность элементарных сигналов : d,,..,,d-,,..(5) поступает на один вход сумматора 121 (фиг. 6), на второй вход которого подается с кодера адреса, выполненного на триггерах 120, пошоследовательность, которая совпадает с подпоследовательностью (2) только в TxiM случае, когда в адресе нет ошибки. На выходе сумматора 12 1 обра; ется последоватедьноста, v;,..,v,...,: А(,...,т, (6) которая совладает с исходной посяедовательностью (1) только в том случав, , когда ни в адресе, ни в данных нет ошибок, так как ее элементы ©e,(,v, vj-.aJ + ejHviSeJ ee-j.vj(г) NWw--d;,®e;H-/rt,ee;)® e.w Если же либо в адресе, либо в данных, либо в адресе и в данных имеются оши&ки, то выполняются не все равенства (7), а декодер в этом случае обнаруживает ошибку, и дешифратор 125 не вырабатывает разрешающий сигнал. Элемент 65 контроля синхронизиру- ющюс импульсов адреса разрешает выработку адресным избирателем БО (фиг.2) сигнала только после того, как совалпо по времени не менее установленного числа импульсов нерегулярных последовательностей, поступающих ва ее входы, а не сошшло по времени не более другого устан(№ленного числа импуль сов. В формирователь 63 (фиг.7) с регистра 45 (фиг.2) вводятся через клютчевые схемы элементарные сигналы налнчня данных. При поступлении с формирователя 54 синхроимпульсов наличия информации указанные элементарные сигналы личия информации поступают на вход 42 передатчика 4О. Блок ЗО (фиг. 8) выделяет с ис-, пользованием поступающих с формиропва 2910 теля 22 синхронизирующих импульсов наличия flftHPiJ значения передаваемых с выбранной периферийной станции элеме терных сигналов наличия данных, которые затем дешифрируются дешифрато-ром 131. Работа генератора 1 ясна из предыдущего описания рабоил системы. В адресном избирателе 50 (фиг. 2) вырабетьюается разрешающий сигнал при выполнении трех условий: при совпадении текущего адреса, наксяшенного в фильтре 49 (фиг. 2) с присвоенным выделенной периферийной станяии адресом j при наличии разрешения с фильтра 49 (фиг. 2) на входе 69; при наличии разрешения с элемента 65. В блоке 52 (фиг. 2) из поступающих с выхода приемника 33 элементарных сигкалга адреса выделяются синхронизируюпще импульсы . В блоке 3 (фиг. 0) кодовой адресашш адреса деишых, предназначенных для передачи на определенные пёриферий 6 ные станции, записьтаются в регистры 135. Затем указанные адреса срав.ниваются в соответствующие моменты вгюмёни с адресом выбранной периферийней стангщи. Совпадение адресов фиксируется поразрядными элементами И 137 « многовыходного элемента И 138, лосйе чего на выходе элемента ИЛИ-НЕ 14D появляется разрешакхций сигнал. Одновременно из регистра 6 (фиг. 1) начшшется передача соответствукндих данных на выделенную периферийную станцию. В блоке 3 (фиг. 9) кодовой адресапнн производится также с использованием регистра на триггерах 132 формнрованне адреса выбранной периферийней стшпган, с которой получены данные по сигна Чг, поступающему на вход 86. Изобретение позволяет увеличии чноло обсдуживаемых периферийных станшй уменьшить время доставки данных по многопункговому кашлу, обеспечить высокую вераостъ передачи данных и снизить затраты на передачу данных.

Фиг.2

r-CD- JO

12J К

т ш

ttff

ш

ш

123

63 fui7

22

Фиг,8

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ ТЕЛЕУПРАВЛЕНИЯ РАСПРЕДЕЛЕННЫМИ ПРОМЫШЛЕННЫМИ ОБЪЕКТАМИ | 1967 |

|

SU215294A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-04-15—Публикация

1978-06-28—Подача