(54). УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ РАЗНОСТИ ДВУХ п-РАЗРЯДНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления разностидВуХ -РАзРядНыХ чиСЕл | 1978 |

|

SU822182A2 |

| Число-импульсное арифметическое устройство | 1980 |

|

SU951303A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU942014A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Устройство для сжатия и восстановления информации | 1983 |

|

SU1149295A1 |

| Устройство для сортировки двоичных чисел | 1982 |

|

SU1049900A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Цифровой измеритель разности фаз радиосигналов за один их период | 1988 |

|

SU1506381A2 |

. Изобретение относится к области автсйнатики и цифровой вычислительной техники и может быть использовано в систетлах обработки информации и управления.

Известны устройства для определения разности двух чисел Я, 12, основанные на последовательном вычитании импульсов из двух счетчиков, в которых хранятся коды этих чисел, и со- держащие шины записи чисел, регистрысчетчики, генератор вычитающих импуль ов, перекл10чатель, триггеры и логические элаяенты И и ИЛИ. Данные устройства позволяют вычислять раз- tS нооть двух чисел с определением её знака и П1Ё ед ;тавленйем результата вычисления в последовательном число-Импульсном коде. Недостатком этйЗ устройств является низкое быстродей- 20 ствие, а также наличие вь1читактоих счетчиков. /

Известно усЬгройство для образования разности двух кодов 3, со- 25 держащее счетчики импульсов, врв енной селектор с пусковым устройством, источник импульсов переписи и триггер остановки. Счетчики данного устройства аботают в , режиме суммиро- JQ

вания. Операция вычитания производится в два этапа. На первом этапе вычисляется дополнительный код вычитаемого, а на в.тором - к дополнительному коду вычитаемого добавляется значение уменьшаемого. Результирующий код есть искомая разность.

Известно также устройство для определения разности двух, п-разрядных чисел 4, содержащее регистрысчетчики уменьшаемого и вычитаемого, генератор тактируквдих импульсов, выхрдяые триггеры, схемы И и ИЛИ,

Недостатком устройства 3 и 4 является низкое быстродействие.

Целью изобретения является повыяение быстродействия операции вычитания и обеспечения независимости времени вычитания от разрядности чисел.

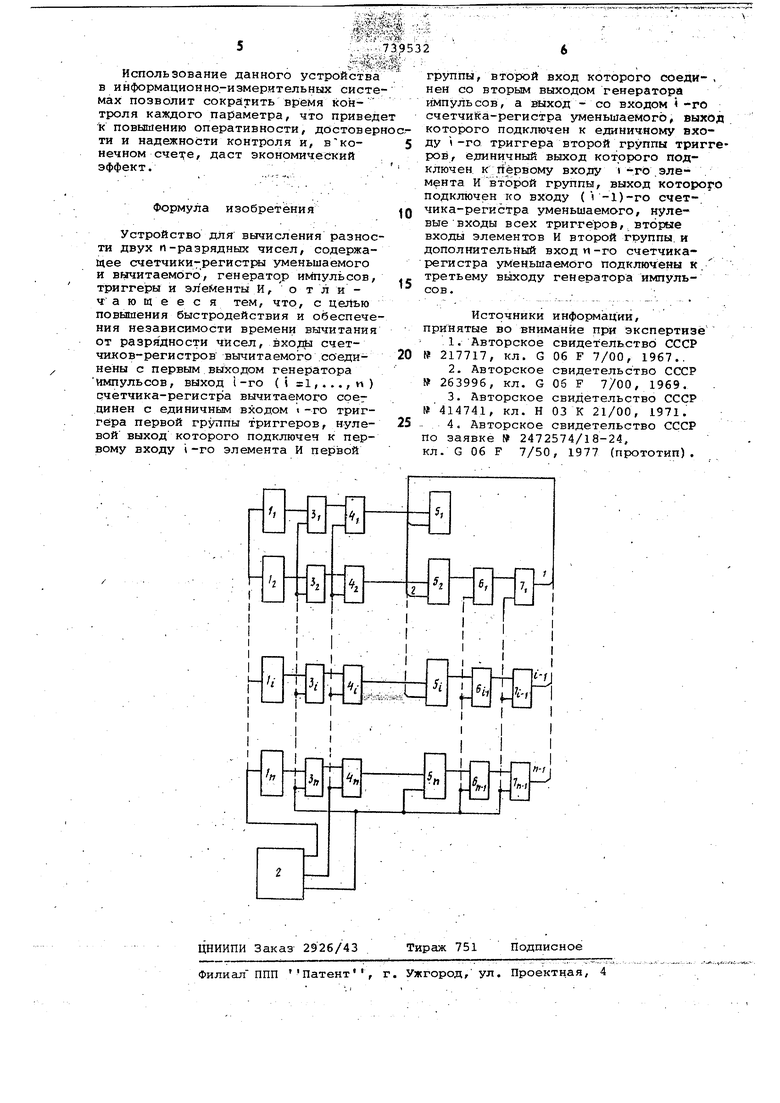

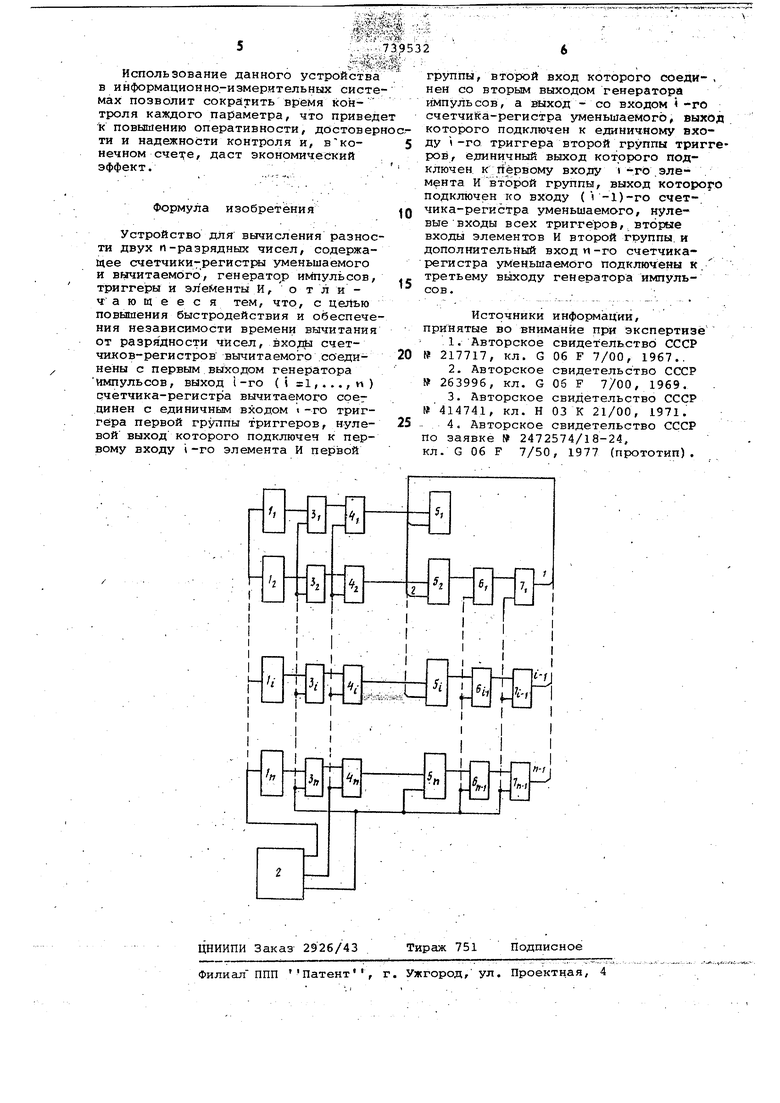

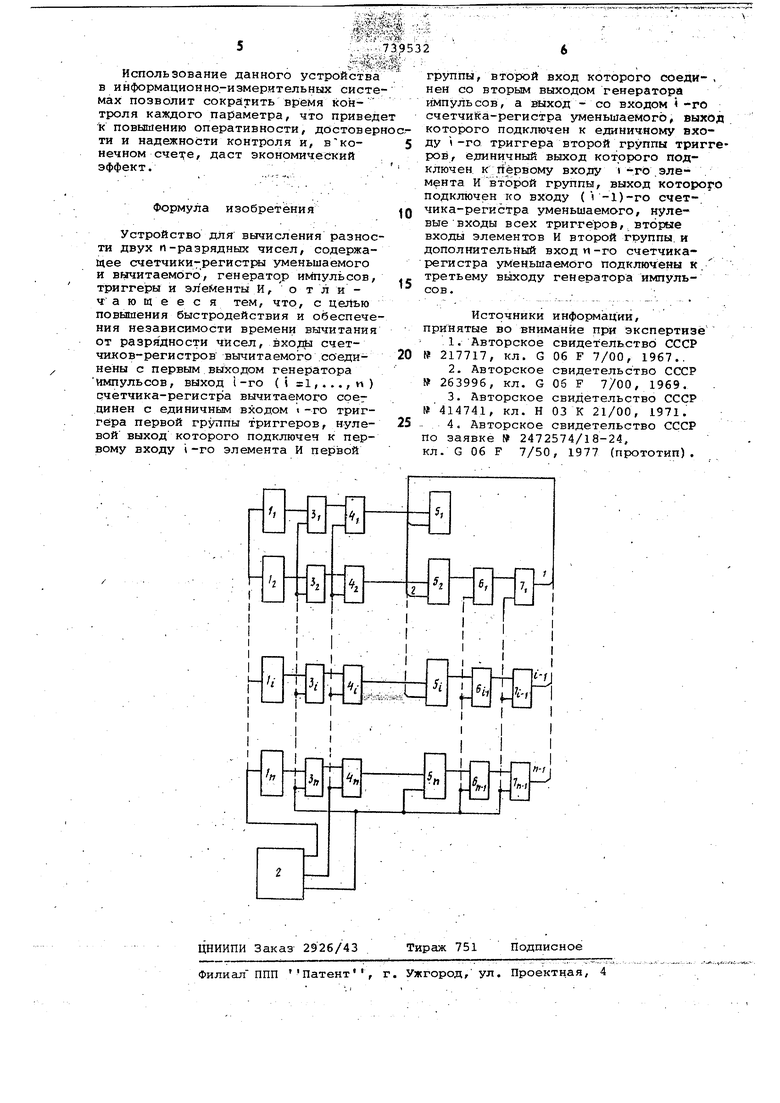

Эта цель достигается тем, что в устройстве для вычисления разности двух п-разрядных чисел, содержащем счетчики-регистры уменьшаемого и вычитаемого, генератор импульсов, триггер и элементы И, входы счетчиКов регистров вычитаемого соединены с первым выходом генератора импульсов, выход 5-го ( х1, ...,п) счетчика739532регистра вычитаемого соединен с еди ннчньам . входом i-го триггера первой группы /триггеров, нулевой выход ко торого подключен к первому входу элемента И первой группы, второй вх которого соединен со вторым выходом генератора импульсов, а выход - со входом 1-го счетчика-регистра умень шаемого, выход которого подключен к единичному входу i -го второй группы триггеров, единичный выход которого подключен к первому входу I-го элемента И второй группы выход которого .подключен ко входу ( i -1)-го счетчика-регистра 5 1ёньша мого. Нулевые йходы всех триггеров ;BTot ie входы элементов И второй гру ййй дополнительный вход i-ro счетчика-регистра уменьшаемого подключе на к третьему выходугенератора импульсов . Такое выполнение устройства ,позволяет производить ВЕ читание двух Многоразрядных чисел в обратном коде. Время выполнения операции вычитания определяется основанием выбранной систеавл счисления .и не Г§ §Йдйт от разрядное™чйсёлГ Начертеже изображена схема тррйства для вычисления разности двух и-разрядных чисел, . .Устройство содержит и счетчикрвгрегистров 1 вычитаетюго, входы которых соединены с первым выходом гё нёрат6 ра 2 импуль сов. Вых од i - г о (lel-n) счетчика-регистра 1 соединен ст -первьм входом -го ( « 1-п) ТЕдаггёра 3, выход которого соединен с первьам входом i-го ( 1-г ) элемента И 4 первой группы. Второй вход -го { J ) элемента И 4 соеди:неи со вторвдй вЫХодЬМ гёйератора 2/ а выход т с первым входом (- -го (. « 1,..., и ) счётчика-регй ipa 5 уменьшаемого. Выход i-го ( i 2,...,п ) счетчика-регистра 5 соединен с первым входом (i -1)-го {« а2,...,11 ) триггера 6, выход которого соединен с первым входом . (V -1)-го ( 9 2,. ..,п ) элёК ёнта И 7 второй группы. Выход (t -1)-го ,{ s2f...r п ) элемента И 7 соедине со втдрь входом 1 -го ( 1,...,п счетчика-регистра 5 уменьшаемого, а Третий вЕЛсдд тенератора 2 соединен вторыми входами триггеров, со вторы входом и-гр счетчика 5 и со вт015Ш -го ( al,..., ) элемента И 7. Количество состояний счетчиковрегйстрбр 1 и 5 равно основанию выб раннрЙ системы й исленйя. . .Устройство работает следующим об разом. В исходном состоянии в счётчиках регистрах 1 поразрядно записано зна чение вычитаемого, а в счетчикахрегистрах 5 - значение уменьшаемого б. разряди записаны собтзвётст|венно в счетчиках-регистрах i-j и 5«i На выходах триггеров 6 находятся . запрещающие потенциалы, а на. выходах триггеров 3 - разрешающие. Для осуществления операции вычитания генёратбр 2 вырабатывает пачки HMnyjibcoB. Количество импуйьсо.в на первом.выходе- генератора 2 равно основанию выбранно.й системы счисления. Пачка импульсов на втором выходе енератора 2 формируется путем поглощения первого импульса в первой пач.ке. С выхода генератора 2 снимается один импульс после окончания абеих пачек с первых выходов. . Для определенности примем, что состояние счетчика-регистра 1 - равно А ( , состояние счетчика-регистра 5 - равно Bi , а основание . выбранной системы счисления равноQ . импульсы генератора 2 начинают поступать на вход счетчика 1 - i и через элемент-И 4-i на вход счетчика-регистра 5 -i . ЧерезQ-А; импуйьс.рв на выходе счетчика 1-( появитсяимпульс переполнения, переводящий триггер 3-1 в .запрещающее состояние. К-этому МРменту времени на вход счетчика 5-i через .элемент И 4-t поступит Q-(А i + 1) имг ульсов, так как во второй пачКе импульсов отсутствует первый импульс. Состояние счетчика 5-i станет равным Bi + Q -(А +1) В5 + Q.- 1 - А . После окончания последнего импульса.в пачках с выхода генератора 2 добавляе.тся рдин импульс в младший разряд уменьшаемого. При Переполнении счетчик.а 5-д в процеёсё вычитания соответствующий триггер б- (i -1) переводится началом импульса переполнения в разрешающее состояние и разрешает прохождение импульса с третьего выхода . . генератора 2 через элемент И 7 - на вход счетчика 5-i . Своим окончанием импульс с третьего выхода генератора 2 переводит триггеры в исходнЬе состояние, подготавливая устройство к нрвому вычитанию. Данное устройство позволяет прой водить вычитание двуЗс многоразрядных ;чисел за01+1 тактов генератора. Быстродействие данного устройства Шйчйтёйьно вйше, чем у известного, и не зависит от разрядности чисел. Данное устройство пэ-быстродействию S большей степени приближается к известным устройствам вычитания чисел, представленных параллельным двоичным кодом, но позволяет, не меняя структуры схемы, использовать любую систему счисления.. Эти осо. бенности предлагаемого устройства Ртёе аюттребованиям, предъявляемым к цифровым приборам и системам управления. . ,. : Использование данного устройства в информационно-измерительных системах позволит сократить время контроля каждого параметра, что приведет к повышению оперативности, достове ти и надежности контроля и, вконечном счете, даст экономический эффект. Формула изобретения Устройство для вычисления разнос ти двух п-разрядных чисел, содержащее счетчики-регистгал уменьшаемого и вычитаемого, генератор импульсов триггеры и элеМенты И, о т л и чающееся тем, что, с целью повышения быстродействия и обеспече ния независимости времени вычитания от разрядности чисел, входа счетчиков-регистров вычитаемого соединены с первым выходом генератора импульсов, выход i-го (i 1,. ..,м) счетчика-регистра вычитаемого срег цинен с единичным входом i -го триггера первой груттпы триггеров, нулевой выход которого подключен к первому входу (-го элемента И первой 73,95 2 группы, второй вход которого соеди- , ней со вторым выходом генератора импульсов, а выход - со входом -го счетчика-регистра уменьшаемого, выход которого подключен к единичному входу (-го триггера второй группы триггеров, едшничный выход которого подключен к Первому входу )-го,эле- . мента И второй группы, выход которого подключен ко входу ( i -1)-го счет-. чика-регистра уменьшаемого, нулевые входы всех триггеров, вторые входы элементов И второй группы, и дополнительный вход и-го счетчикарегистра уменьшаемого подключаемы к. третьему выходу генератора импульсов.. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 217717, кл. G 06 F 7/00, 1967.. 2.Авторское свидетельство СССР 263996, кл. G Об F 7/00, 1969. 3.Авторское свидетельство СССР №414741, кл. Н 03 К 21/00, 1971. 4. Авторское свидетельство СССР по заявке 2472574/18-24, кл. G 06 F 7/50, 1977 (прототип).

Авторы

Даты

1980-06-05—Публикация

1977-11-22—Подача