(54) ЦИФРОВОЙ КОРРЕЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой многоканальный коррелятор периодических фазоманипулированных сигналов | 1978 |

|

SU734716A1 |

| Цифровой корреляционный фильтр | 1978 |

|

SU792559A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Цифровой коррелятор | 1990 |

|

SU1824642A1 |

| Устройство для стабилизации средней частоты шумовых выбросов над пороговым уровнем | 1980 |

|

SU902269A1 |

| Устройство для автоматического контроля главных каналов радиоприемных устройств | 1977 |

|

SU663118A1 |

| Система связи | 1989 |

|

SU1815802A1 |

| Цифровой коррелятор | 1979 |

|

SU851412A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для определения корреляционных функций различ .ных процессов, а также в системах и устройствах, основанных на-корреляционных методах обработки сигналов, в частности, в системах радиолокации и радионавигации. Известен цифровой коррелятор, содержащий, четыре блока динамическо памяти, два блока умножения, два макопителя и регистр 1. Это одноканальное устройство обладает недостаточным быстродействием при относительной сложности. Н личие в корреляторах перемножителей обычно является причиной их сравнительно визкого. быстродействия. Пр менениё в качестве перемножителей быстродействующих запоминающих устройств не всегда возможно, поскольку число уровней квантования си налов может достигать значительной величины,и требуемый объем памяти в этом случае становится непомерно большим. Известен также цифровой коррелято состояЬшй из аналого-цифровых преобразователей входного и опорного сигналов, выходы которых через перемножитель подк.точены к сумматору, выполняющему функции интегратора. Сигнал на выходе сумматора определяет величину корреляции опорного и входного сигналов 2. Недостатком этого коррелятора является низкое быстродействие. Это связано с тем, что для увеличения точности коррелятора или для устранения подавления слабых сигналов в нем требуется увеличивать число . уровней квантования входного сигнала. При этом увеличивается время умножения, которое пропорционально числу разрядов сомножителей, что в свою очередь увеличивает минимально допуститиый дискрет квантования по времени входных процессов, т. е. снижает быстрбдействие коррелятора. Целью изобретения является повышение быстродействия цифровбго коррелятора. Поставленная цель достигается тем, что в коррелятор, содержащий . первый и второй аналого-цифровой преобразователи, входы которых являют ся входами ;коррелятора, блоки умножения, накапливающие сумматоры и

усреднитель, введен коммутатор с числом выход зв, равным числу уровней квантования опорного сигнала, входы коммутатора соединены с выходами соответствующих аналого-цифро. вых преобразователей, а вйходы соединены с входами соответствующих накапливающих сумматоров, выход каждго из которых соединен с входом блока умножения, выход каждого из которых подключен к соответствующему входу усреднителя. Это позволяет во .время действия входного сигнала производить только суммирование его квантованных выборочных значений, каждое из которых соответствует определенному уровню квантования опорного сигнала, а более медленную операцию умножения, ограничивающую быст родействие, выполнять после окончания действия входного сигнала.

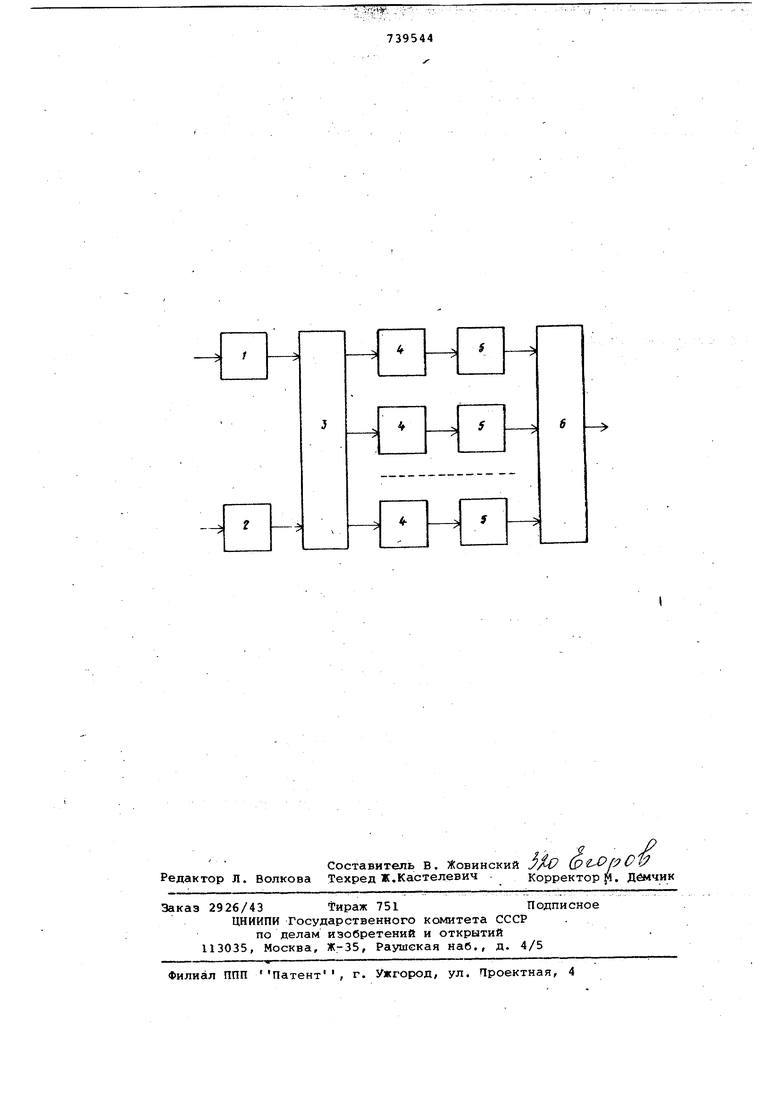

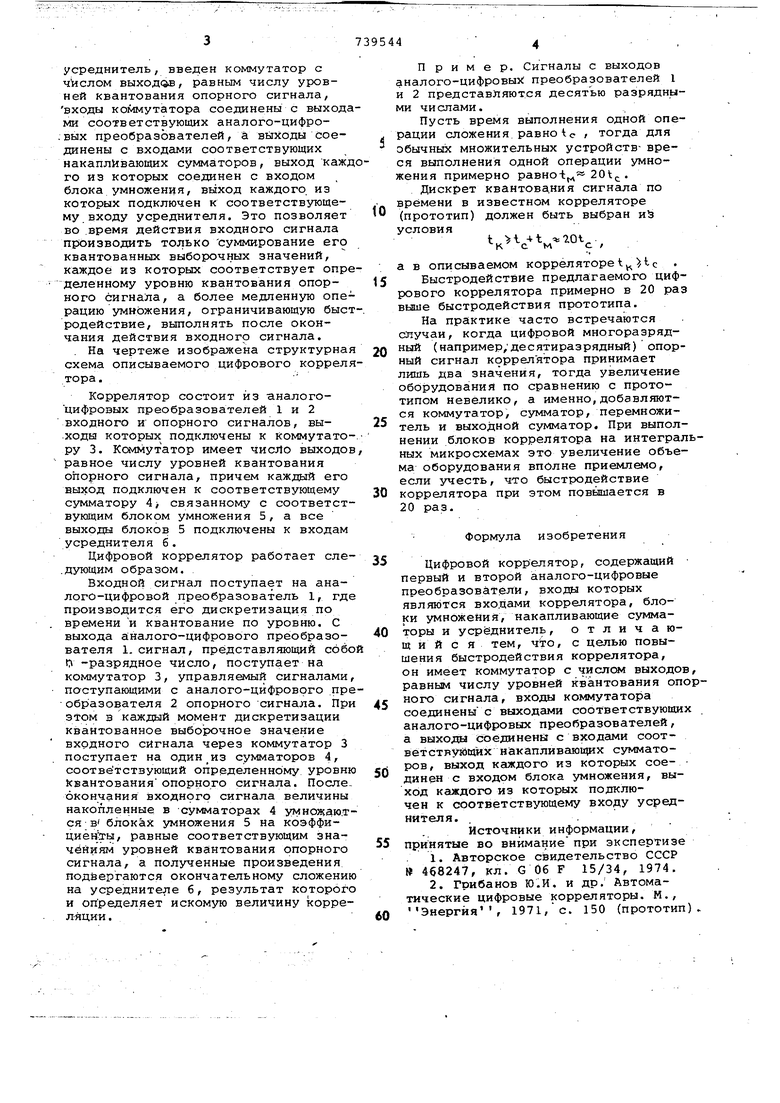

. На чертеже изображена структурная схема описываемого цифрового коррелятора.

Коррелятор состоит из нналогоцифровых преобразователей 1 и 2 входного и опорного сигналов, выходы которых подключены к коммутатору 3. Ко1мутатор имеет число выходов равное числу уровней квантования опорного сигнала, причем каждый его выход подключен к соответствующему сумматору 4 связанному с соответствующим блоком умножения 5, а все выходы блоков 5 подключены к входам

усреднителя 6.

Цифровой коррелятор работает еле.дующим образом.

Входной сигнал поступает на аналого-цифровой преобразователь 1, где производится его дискретизация по времени и квантование по уровню. С выхода аналого-цифрового преобразователя 1. сигнал, представляющий собо О -разрядное число, поступает на коммутатор 3, управляемый сигналами, поступающими с аналого-цифрового преобразователя 2 опорного сигнала. При этом в каждый момент дискретизации квантованное выборочное значение входного сигнала через коммутатор 3 поступает на сумматоров 4, соответствующий определенному уровню Квантования опорного сигнала. Послеокончания входного сигнала величины накопленные в -сумматорах 4 умножаю.тся в блоках умножения 5 на коэффициёнРты, равные соответствующим значёниям уровней квантования опорного сигнала, а полученные произведения подйергаются окончательному сложению на усреднителе б, результат которого и определяет искомую величину корреляции.

П р и м е р. Сигналы с выходов аналого-цифровых преобразователей 1 и 2 представляются десятью разрядными числами.

Пусть время выполнения одной операции сложения равного , тогда для обычных множительных устройств- вреся выполнения одной операции умножения примерно paBHOi 20,. .

Дискрет квантования сигнала по времени в известном корреляторе (прототип) должен быть выбран иЗ условия

,

а в описываемом корреляторе t Не

Быстродействие предлагаемого цифрового коррелятора примерно в 20 раз выше быстродействия прототипа.

На практике часто встречаются случаи, когда цифровой многоразрядный (например;десятиразрядный) опорный сигнал коррелятора принимает лишь два значения, тогда увеличение оборудования по сравнению с прототипом невелико, а именно,добавляются коммутатор, сумматор, перемножитель и выходной сумматор. При выполнении блоков коррелятора на интегралных микросхемах это увеличение объема оборудования вполне приемлемо, если учесть, что быстродействие коррелятора при этом повьшается в 20 раз.

Формула изобретения

Цифровой коррелятор, содержащий первый и второй аналого-цифровые преобразователи, входы которых являются вхо.цами коррелятора, блоки умножения, накапливающие сумматоры и усреднитель, отличающийся тем, что, с целью повышения быстродействия коррелятора, он имеет коммутатор с числом выходов равным числу уровней квантования опоного сигнала, входы коммутатора соединены с выходами соответствующи аналого-цифровых преобразователей, а выходаа соединены с входами соответствующих накапливающих сумматоров, выход каждого из которых соединен с входом блока умножения, выход каждого из которых подключен к соответствующему входу усреднителя. ..

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-06-05—Публикация

1977-12-26—Подача