тор 1, если запоминающий конденсатор 2 заряжен (ячейка памяти хранит логическую единицу), и далее через открытый транзистор 3 считывания заряжает паразитный конденсатор 8. В течение тактового импульса Ф2 через открытый транзистор 4 записи подзаряжается конденсатор 2 путем перераспределения заряда между параллельно включенными конденсаторами 8 и 2.

Если запоминающий конденсатор 2 разряжен (ячейка памяти хранит логический нуль), то тактовый импульс Ф1 не проходит через запертый запоминающий транзистор 1. В итоге не происходит подзаряда конденсатора 2.

Режим записи. Адресный импульс на шине 9 отпирает адресный транзистор 5 одновременно с поступлением тактового импульса 02 на шину 6 импульсного питания. Через открытые транзисторы 5 и 4 обкладка конденсатора 2, соединенная с затвором запоминающего транзистора, подключается к числовой щине 10. Если записывается логическая единица, то цепь заряда конденсатора 2 замыкается через открытый запоминающий транзистор 1. При записи нуля заряда конденсатора 2 не происходит либо он разряжается через транзисторы 5, 4 и 1, если ранее был заряжен.

Режим считывания. Числовая щина 10 предварительно разряжается. Адресный импульс на шине 9 отпирает адресный транзистор 5 одновременно с поступлением тактового импульса Ф: на шину 7 импульсного питания. Когда ячейка памяти хранит логическую единицу (конденсатор 2 заряжен), то тактовый импульс Ф через транзисторы 1, 3 и 5 вызывает увеличение (по абсолютной величине) потенциала числовой шины 10. Если ячейка памяти хранит логический нуль (конденсатор 2 разряжен), то запоминающий транзистор 1 заперт и изменения потенциала числовой шины 10 не происходит.

Так как нет необходимости длительного хранения заряда на запоминающем конденсаторе 2, величина его емкости, а следовательно, и размеры могут быть выбраны небольшими. Важно лишь, чтобы его емкость была существенно больще паразитной емкости конденсатора 11, включенного между затвором транзистора 1 и землей. В ОЗУ, построенном на предлагаемых ячейках памяти, регенерация осуществляется в каждом цикле тактовых импульсов одновременно во всех невыбранных ячейках памяти параллельно с записью или считыванием в выбранный элемент. Поскольку частота регенерации в этом случае велика, величина паразитной емкости конденсатора 8 может быть значительно меньше емкости запоминающего конденсатора 2.

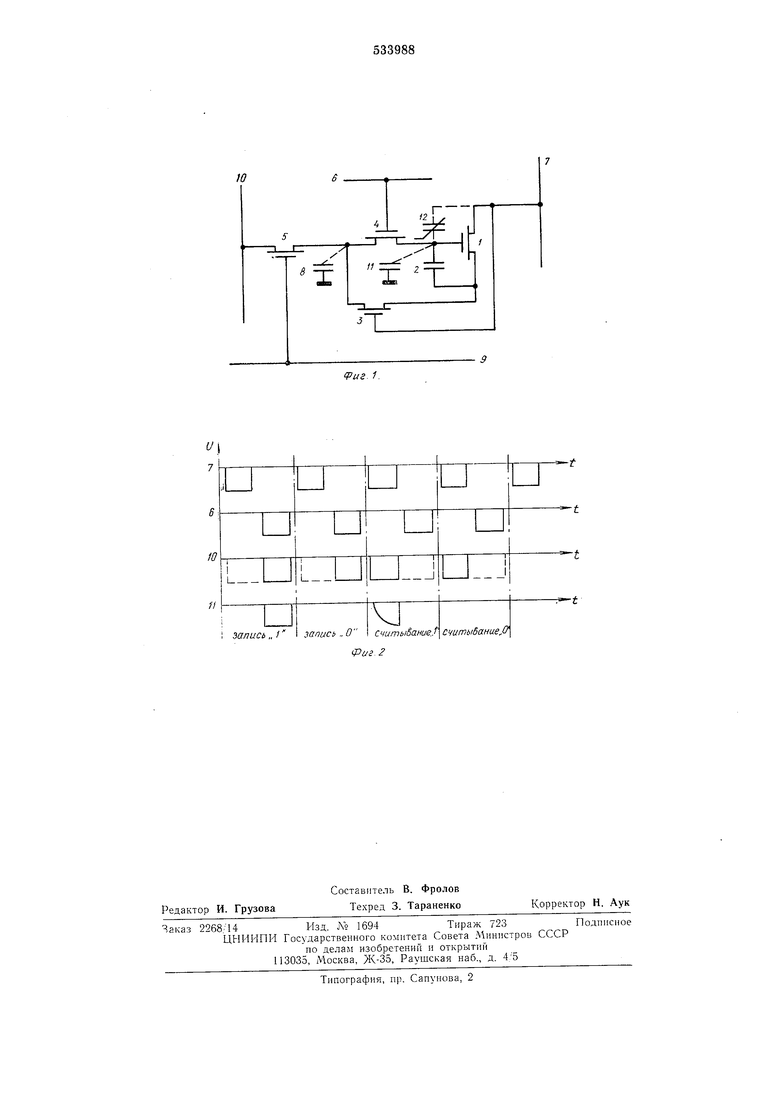

Дополнительное повыщение быстродействия в предлагаемой ячейке за счет некоторого увеличения ее площади достигается путем использования конденсатора 12 «бикап в качестве запоминающего конденсатора. Включение конденсатора 12 показано на фиг. 1, затворный электрод конденсатора 12 должен

подключаться к затвору информационного транзистора 1. Величина емкости конденсатора 12 при хранении логической единицы должна существенно превосходить емкость паразитного конденсатора 11, а

при хранении логического нуля - намного меньше емкости конденсатора 11 во избежание ложного отпирания запоминающего транзистора 1 при считывании логического нуля. Использование предлагаемой ячейки памяти на МДП-транзисторах позволяет повысить быстродействие и снизить потребляемую мощность ОЗУ, построенных на этих ячейках.

Формула изобретения

Ячейка памяти на МДП-транзисторах, содержащая запоминающий транзистор, затвор которого соединен с одной обкладкой конденсатора, адресный транзистор, затвор которого

подключен к адресной шине, а исток - к числовой шине, и шины импульсного питания, отличающаяся тем, что, с целью снижения потребляемой мощности и повышения быстродействия, она содержит транзисторы считывания и записи, причем исток транзистора считывания соединен с истоком транзистора записи н со стоком адресного транзистора, затвор транзистора считывания соединен со стоком запоминающего транзистора и с первой

шиной импульсного питания, сток - с истоком запоминающего транзистора, другая обкладка конденсатора подключена к истоку запоминающего транзистора, а затвор транзистора записи соединен с второй щиной импульсного литания, сток - с затвором запоминающего транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Запоминающий элемент на мдп транзисторах | 1973 |

|

SU450230A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Накопитель для запоминающего устройства | 1980 |

|

SU940238A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Элемент памяти | 1979 |

|

SU788175A1 |

| Динамическая ячейка памяти | 1974 |

|

SU523454A1 |

| Ассоциативная ячейка памяти | 1976 |

|

SU605268A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

Авторы

Даты

1976-10-30—Публикация

1975-04-08—Подача