Изобретение относится к вычислительной технике и может быть исполь зовано в арифметических устройствах цифровых вычислительных машин. Известно устройство для умножения, содержащее сумматор, регистр множителя,блоки произведения множимэго на константы, блоки выдачи про ведения множимого на константы со сдвигом и без сдвига 1. Недостатком такого устройства является его сложность и низкое быстродействие . Наиболее близким к изобретению является устройство для умножения на h разрядов множителя, содержащее сумматор, блок управления, .соединенный с п разрядами регистра мно жителя, q блоков умножения множим го на константы (2р„+1), где q max (2V2 ), п 1 . .-vX.+-i,,,i,...,c(v-i выходы которых соединены с информационными входами блоков элементов И управляющие входы блоков элементов соединены с соответствующими выхода ми блока управления, а выходы соеди нены с входами коммутатора, выходы которого соединены ср входами сумма тора, управляющие входы коммутатора соединены с соответствующими выходами блока управления 2. Недостатком известного устройства является егосложность. Цель изобретения - упрощение устройства. Цель достигается тем, что устройство для умножения на п разрядов множителя, содержащее накапливающий сумматор, регистр 1 иожителя, g блоков умножения на константы (2р +1)/ где q max ( , ), п ,с + .ек,Ьк-л + .Рт-О- -.М-Р (q-1, блоки элементов И, блок управления и коммутатор, причем выходы регистра множителя подключены ко входам блока управления, выход блоков умножения соединены со входаиии соответствующих блоков элементов И,выходы коммутатора подключены ко входам накапливающего сумматора, управляющие входы блоков элементов И, коммутатора и накапливающего сумматора подключены к соответствующим выходам блока управления, содержит первый и второй блоки сдвига, причем выходы первого блока сдвига подключены ко входам коммутатора, а входы - к выходам второго блока сдвига, входы

которого подключены к выходам блоков элементов И.

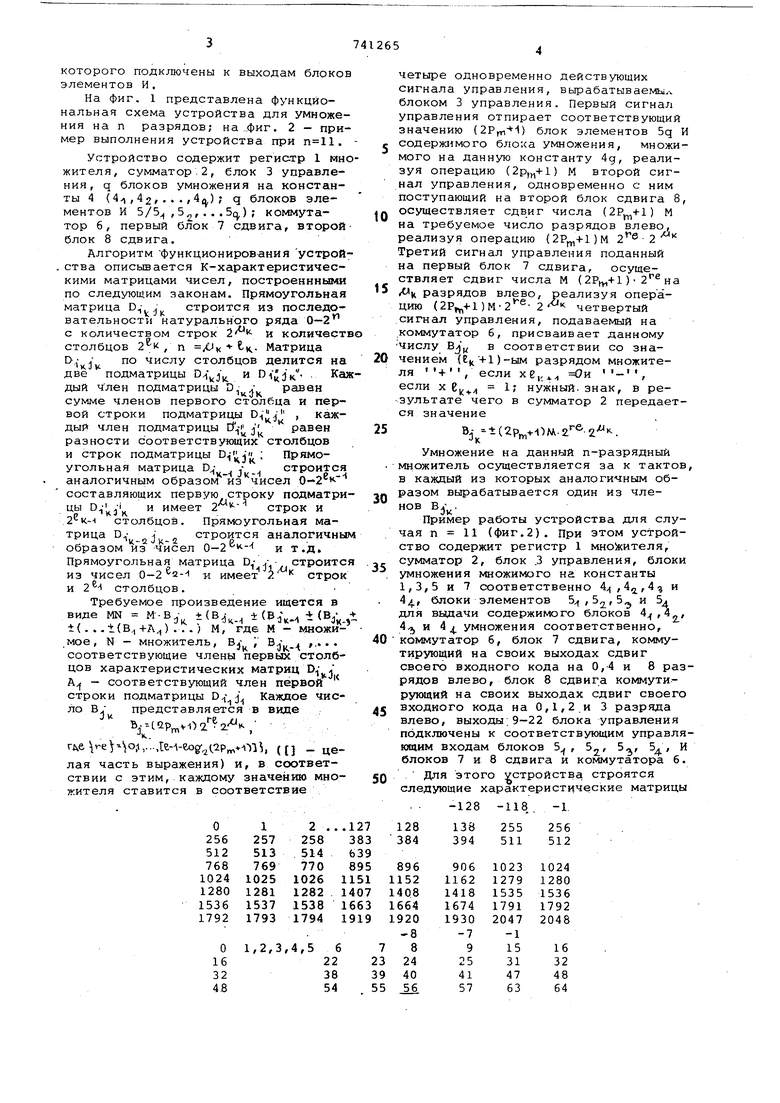

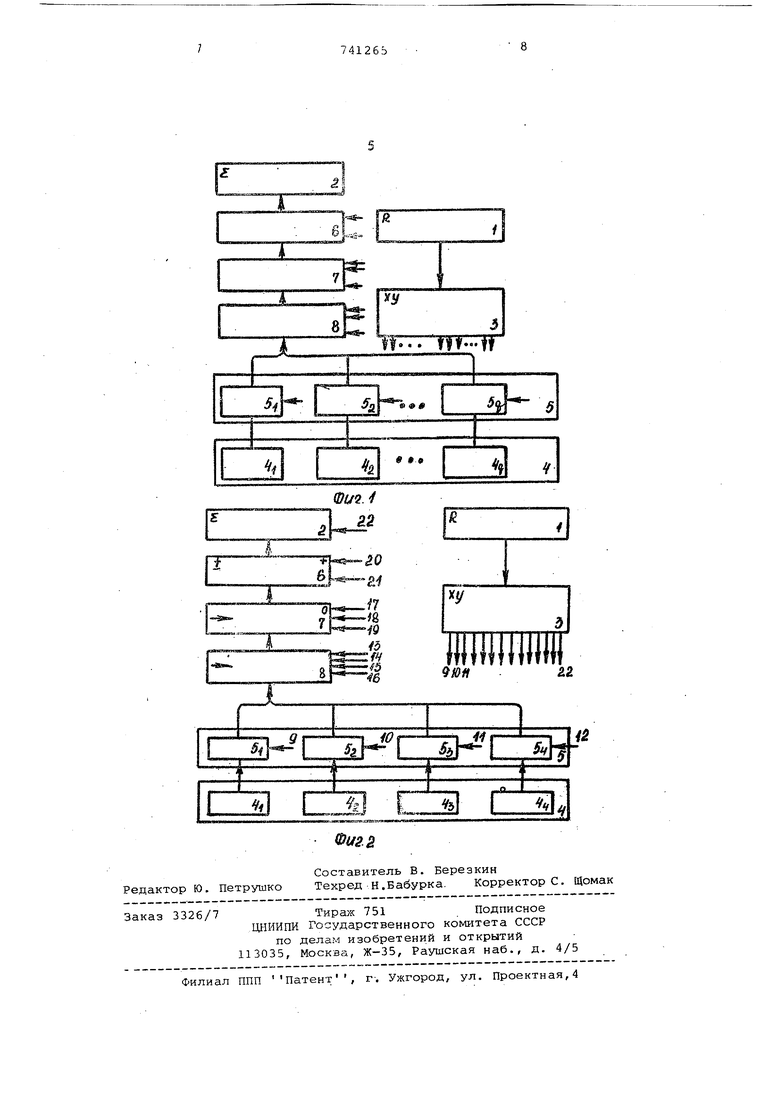

На фиг. 1 представлена функциональная схема устройства для умножения на п разрядов; )иг. 2 - пример выполнения устройства при . Устройство содержит регис-тр 1 множителя, сумматор.2, блок 3 управления, q блоков умножения на константы 4 (4,,42,.../4q,); q блоков элементов И 5/5 , 5, . . . Sq.) ; коммутатор 6, первый блок 7 сдвига, второйблок 8 сдвига.

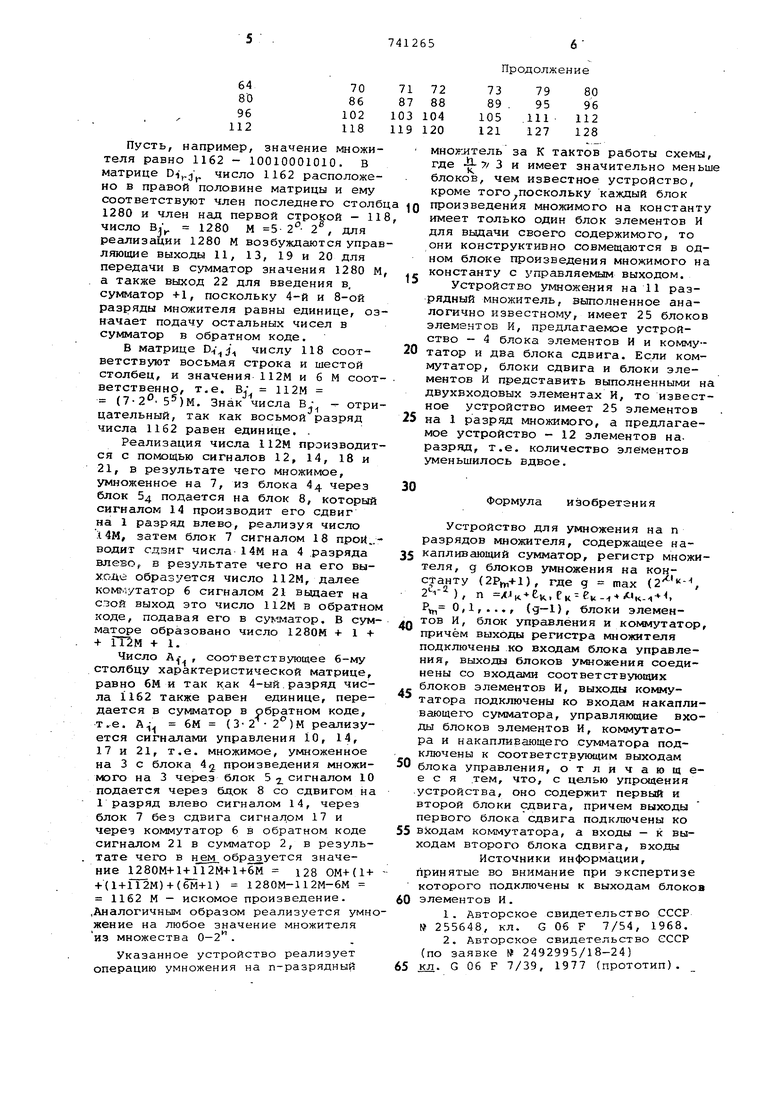

Алгоритм функционирования устрой. ства описывается К-характеристическими матрицами чисел, построеннными по следующим законам. Прямоугольная матрица строится из последовательности натурального ряда 0-2 с количеством строк и количеств столбцов , п к,- Матрица D., V по числу столбцов делится на две подматрицы и . . Каждый член подматрицы равен сумме членов первого столбца и перстроки подматрицы

вой

каждый член подматрицы Cf-fJ j равен

Unpitl ТТОГТМД ТПМ1ТМ л разности соответствукицих столбцов и строк подматрицы , i Прямоугольная матрица у строится аналогичным образом из чисел составляющих первую строку подматриць1 и имеет 2 строк и

столбцов. Прямоугольная матрица j строится аналогичн образом Vs чисел и т.д.

- р - - i-iJlx(

Прямоугольная матрица D,, , строитс из чисел чисел к имеет 2 строк и 2 -1 столбцов .

Требуемое произведение ищется в виде Ш М--В.,- ±(В.|. ±(Вз. JUi(...±()./.) М, где М - множимое, N - множитель, 1 Ок- соответствующие члены первьос столбцов характеристических матриц h - соответствующий член первой строки подматрицы и Каждое Зч представляется в виде

ь..--1ар„л-02 2..,А

,-i,...,i:e- -eog,(,):i, (fj „целая часть выражения) и, в соответствии с этим, каждому значению множителя ставится в соответствие

четыре одновременно действующих сигнала управления, вырабатываемы.х блоком 3 управления. Первый сигнал управления отпирает соответствующий значению (() блок элементов 5q И содержимого блока умножения, множимого на данную константу 4д, реализуя операцию () М второй сигнал управления, одновременно с ним поступающий на второй блок сдвига 8, осуществляет сдвиг числа () М на требуемое число разрядов влево, реализуя операцию ()М 2 2 Третий сигнал управления поданный на первый блок 7 сдвига, осуществляет сдвиг числа М ( 2Pty,+ l) - 2 на разрядов влево, реализуя операцию () 2 « четвертый сигнал управления, подаваемый на коммутатор 6, присваивает данному Числу Bj, в соответствии со значением )-ым разрядом множителя +, если хЕ,, 0и -, если X Bj, 1; нужный, знак, в результате чего в сумматор 2 передается значение

B,,(..

Умножение на данный п-разрядный множитель осуществляется за к тактов, в каждый из которых аналогичным образом вырабатывается один из членов Вд.

Пример работы устройства для случая п 11 (фиг.2). При этом устройство содержит регистр 1 мно5кителя, сумматор 2, блок .3 управления, блоки умножения множимого на константы 1,3,5 и 7 соответственно 4,4,2,4 и 4, блоки элементов 5,52.,5„, и 5д для выдачи содержимого блоков 4 . 4 и 4 умножения соответственно, коммутатор б, блок 7 сдвига, коммутирующий на своих выходах сдвиг своего входного кода на О,-4 и 8 разрядов влево, блок 8 сдвига коммутирующий на своих выходах сдвиг своего входного кода на 0,1,2 и 3 разряда влево, выходы;9-22 блока управления подключены к соответствующим управля5., И ющим входам блоков 5

Jxf 2 Э блоков 7 и 8 сдвига и коммутатора 6.

Q Для этого устройства строятся

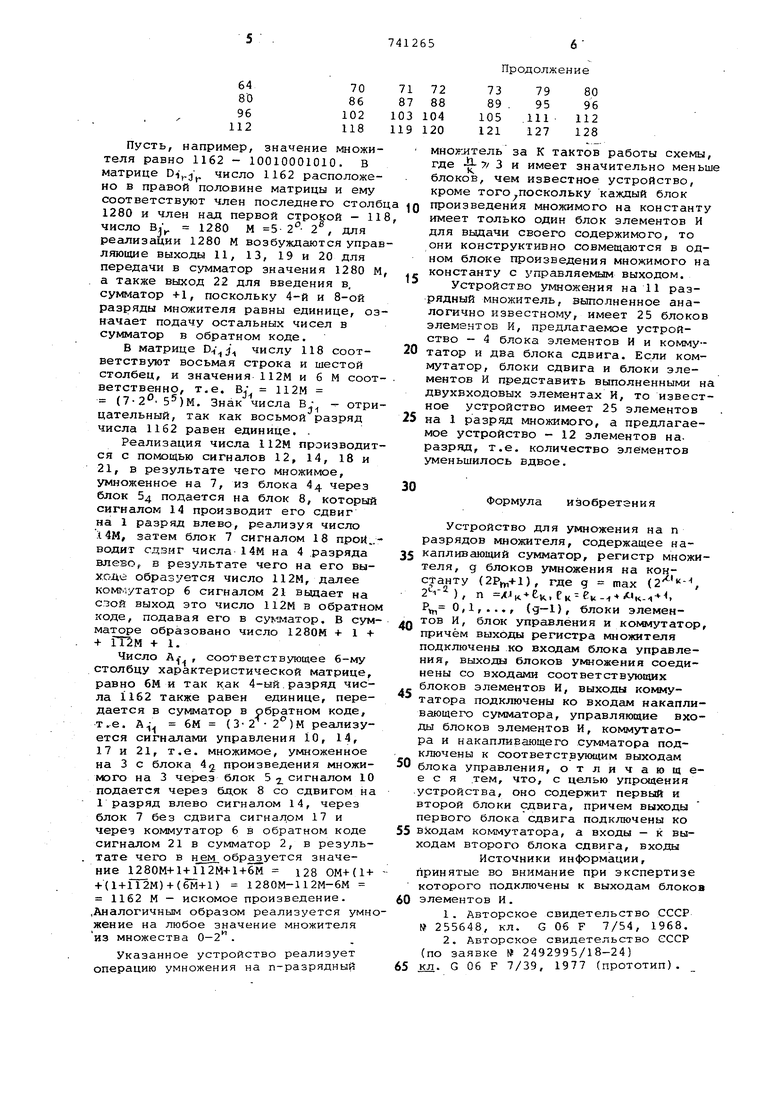

следующие характеристические матрицы

-128 -118 -1. Пусть, например, значение множи теля равно 1162 - 10010001010. В матрице DiYj число 1162 расположе но в правой половине матрицы и ему соответствуют член последнего стол 1280 и член над первой строкой - 1 число Bj 1280 М 2, для реализации 1280 М возбуждаются упра ляющие выходы 11, 13, 19 и 20 для передачи в сумматор значения 1280 М а также выход 22 для введения в, сумматор +1, поскольку 4-й и 8-ой разряды множителя равны единице, о начает подачу остальных чисел в сумматор в обратном коде. В матрице числу 118 соответствуют восьмая строка и шестой столбец, и значения 112М и 6 М соот ветственно, т.е. Ву 112М ( 5)М. Знак числа - отри цательный, так как восьмой разряд числа 1162 равен единице. . Реализация числа 112М производит ся с помощью сигналов 12, 14, 18 и 21, в результате чего множимое, умноженное на 7, из блока 44 че{)ез блок 54 подается на блок 8, который сигналом 14 производит его сдвиг на 1 разряд влево, реализуя число Х4М, затем блок 7 сигналом 18 прой. водит сдвиг числа 14м на 4 .разряда влево, в результате чего на его выходе образуется число 112М, далее кoм.iyтaтop 6 сигналом 21 выдает на сзой выход это число 112м в обратно коде, подавая его в сук-зчатор. В сум маторе образовано число 1280М + 1 + + ГГ2М +1. Число , соответствующее 6-му столбцу характеристической матрице, равно бМ и так к.ак 4-ый разряд числа 1162 также равен единице, передается в сумматор в обратном коде, т.е. 6М (3-2 2°) М реализуется сигналами управления 10, 14, 17 и 21, т.е. множимое, умноженное на 3 с блока 4 произведения множимого на 3 через блок 5 j сигналом 1 подается через бл,ок 8 со сдвигом н 1 разряд влево сигналом 14, через блок 7 без сдвига сигналом 17 и через коммутатор 6 в обратном коде сигналом 21 в сумматор 2, в результате чего в н.ем обра уется значение 1280М+И-112М+И-6М 128 ОМ+(1+ +()+(6М+1) 1280М-112М-6М 1162 М - искомое произведение. ,Аналогичным образом реализуется умн жение на любое значение множителя из множества 0-2 . Указанное устройство реализует операцию умножения на п-разрядный

Продолжение множлтель за К тактов работы схемы, где - 7/ 3 и имеет значительно меньше блоков, чем известное устройство, кроме того поскольку каждый блок произведения множимого на константу имеет только один блок элементов И для выдачи своего содержимого, то они конструктивно совмещаются в одном блоке щэоизведения множимого на константу с управляемым выходом. Устройство улвдожения на 11 разрядный множитель, выполненное аналогично известному, имеет 25 блоков элементов И, предлагаемое устройство - 4 блока элементов И и коммутатор и два блока сдвига. Если коммутатор, блоки сдвига и блоки элементов И представить выполненными на двухвходовых элементах И, то известное устройство имеет 25 элементов на 1 разряд множимого, а предлагаемое устройство - 12 элементов наразряд, т.е. количество элементов уменьшилось вдвое. Формула изобретения Устройство для умножения на п разрядов множителя, содержащее накапливающий сумматор, регистр множителя, g блоков умножения на константу (), где g max ( i ) , n . . 0,1,..., (g-1), блоки элементов и, блок управления и коммутатор, причём выходы регистра множителя подключены ко входам блока управления, выходы блоков уивюжения соединены со входами соответствующих блоков элементов И, выходы коммутатора подключены ко входам накапливающего сумматора, управляющие входы блоков элементов И, коммутатора и накапливающего сумматора подключены к соответствующим выходам блока управления, отличающееся тем, что, с целью упрощения устройства, оно содержит первый и второй блоки сдвига, причем выходы первого блока сдвига подключены ко входам KONiMyTaTopa, а входы - к выходам второго блока сдвига, входы Источники информации, принятые во внимание при экспертизе которого подключены к выходам блоков элементов И. 1.Авторское свидетельство СССР 255648, к-л. G 06 F 7/54, 1968. 2.Авторское свидетельство СССР (по заявке № 2492995/18-24) кл. G 06 F 7/39, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения на п-разрядов множителя | 1977 |

|

SU717764A1 |

| Устройство для умножения | 1977 |

|

SU662940A1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Устройство для умножения двух N-разрядных чисел | 1979 |

|

SU920711A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Устройство для умножения на -разрядов множителя | 1977 |

|

SU750487A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

Авторы

Даты

1980-06-15—Публикация

1978-02-28—Подача