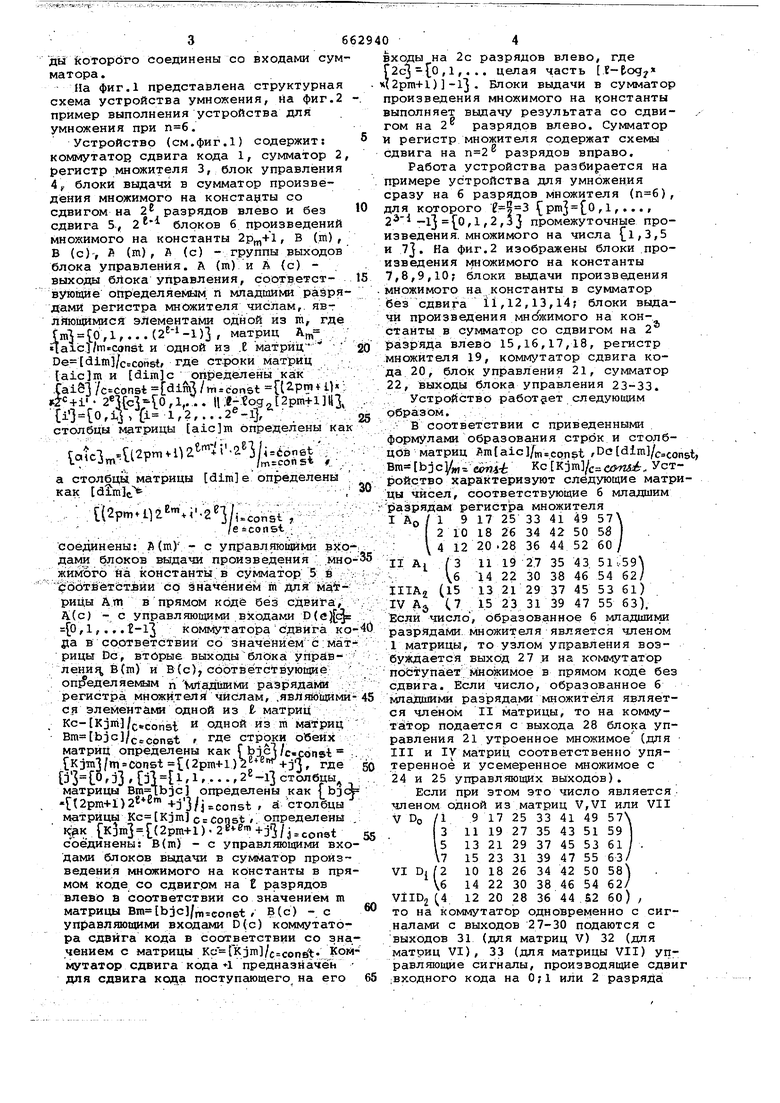

Изобретение относится к вычислительной технике и может быть применено в арифметических устройствах цифровых вычислительных машин, особенно в случаях повышенных требований по быстродействию. Известно устройство, состоящее из сдвиговых регистров множителя.и сумматора, в которых операция умножения регшизуется путем сдвига реги ров множимого и множителя и многокр ,ных сложений в сумматоре множимого, сдвинутого на определенное число ра рядов, определяемое положением единиц в разрядах множителя, с частными произведениями, хранящимися в сумма торе 1 . Недостатком известного устройства является низкое быстродействие. Наиболее близким по технической сущности к. данному изобретению является устройство, содержащее блок управления, регистр множителя, сумматор, блоки произведений множимого на константы, блоки выдачи в сумматор произведения множимого на константы со сдвигом влево и без сдвига, причё выходы регистра множителя соединены со входами блока управления 2, Недостатком известного устройства является; низкое быстродействие. Целью изобретения является поэ.ьпдение быстродействия. С этойцелью в устройство введены блоков выдачи в сумматор произведения множимого на константы, (&3) блоков произведений множимого на онстанты 2 (Pm (2 -1), комл татор сдвига кода, (2 -1) выходов первой и второй групп выходов блока управления соединены со входалш управления блоков выдачи в сумматор произведения множимого на константы со сдвигом на 2 разрядов влево и без сдвига соответственно, информационные входы которых соединены с выходами блока произведейия множимого на константу (), выходы блоков Ёыдачи в сумматор произведения множимого на константы со сдвигом на 2 }азрядов влево и без сдвига соединены с информационными входалет коммутатора сдвига кода, (-1)е выходы третьей и четвертой групп выходов блока управления соединены соответственно с (Е-1)-ми входа-. ми первой и второй групп управляющих входов коммутатора сдвига кода, выходы которого Соединены со входами сумматора. На фиг,1 представлена структурная схема устройства умножения, На фиг.2 пример выполнения устройства для умножения при . Устройство (см.фиг.1) содержит: коммутатор сдвига кода 1, сумматор 2 регистр множителя 3, блок управления 4, блоки выдачи в сумматор произведения множимого на констауты со сдвигом на 2 разрядов влево и без сдвига 5, блоков 6 произведений множимого на константы , В (т), В (с), Р (т), и (с) - группы выходов блока управления. А (т) и А (с) - , выходы блока управления, соответствуюй1ие определяемым, и младшими разрядамй регистра множителя числам,, яв-г ляющимися элементами одной из т, где т} {О,,...( -1)3, матриц Ат , aicl/m«const и одной из .Е матриц De diin /ccconsb где строки матриц . / и определены как столбцы матрицы определены : tatc3 i2pm.iU - 3|i;|gn|t.:а столбцы матрицы определены как . , () const 7 . соединены: А (m)- - с управляющими вхо дами блоков выдачи произведения .мно жимого на константы, в сумматор 5 ё ; .ёбЪтёётЬт йи сС5 3на 1ёнием in для MasриЦы Am впрямом коде без сдвига, д:(с) - с управляющими входами р( {0,1, .,. t-l коммутатора сдвига ко да в соответствии со значением 6: мат рицы Вс; втбрые выходы бл(3ка: уйравлениу, В (т) и В (с )у сботвётствующне; оп1 еделнемым п йадйшми раэряДаШ : регистра мнсжителя числам, .являющими ся элементаю одной из матриц . и одной из ш ,.epnst г где строки оВейх матриц определены как Г bjc c-const Kjm3/m COnst {2pm+l), где Э5 СО33 ..., столбцы матрицы определен матрицы .mj c const , определен) K3in (2pra+l). ..gt соединены: B(m) - с управляющими вхо дами блоков выдачи в сумматор произведения мнсякимого на константы в пря мом коде со сдвиг.ом на разрядов влево в соответствии со значением m матрицы Bin bjc /mrconet В(с) -с управляющими входами D(c) коммутатора сдвига кода в соответствии со зна чением с матрицы Ka rKjm /c conBt- мутатор сдвига кода 1 предназначен для сдвига кода поступающего на его входы на 2с разрядов влево, где Г2сЗ ,1,. .. целая часть (2рга+1) -1 . Блоки выдачи в сумматор произведения множимого на константы выполняет выдачу результата со сдвигом на 2 разрядов влево. Сумматор и регистр множителя содержат схемы сдвига на разрядов вправо. Работа устройства разбирается на примере устройства для умножения сразу на б разрядов множителя (), для которого 2 Co f 1 f f -l} 0,1,2 ,33 промежуточные произведения, множимого на числа l,3,5 и 7j. На фиг.2 изображены блоки .произведения множимого на константы 7,8,9,10; блоки выдачи произведения множимого на константы в сумматор без сдвига 11,12,13,14 блоки выдачи произведения мнбжимого на константы в сумматор со сдвигом на 2 р азряда влево 15,16,17,18, регистр .множителя 19, коммутатор сдвига кода 20, блок управления 21, сумматор 22, выходы блока управления 23-33. .; Устройство работает следующим образом. .. , .В соответствии с приведенными формулами образования строк и столбцов матриц ra aicl/n,cpnst /DC dlmj/c const, ,. с. Устройство Jt арак т ери 3 уют следующие матрицы чисел, соответствующие 6 младшим разрядам регистра множителя I АО / 1 9 17 25 33 41 49 57 2 10 18 26 34 42 50 58 4 12 20 .28 36 44 52 60 / /3 11 19 2.7 35 43 5lv59 6 14 22 30 38 46 54 62/ (15 13 21 29 37 45 53 61) (7 1.5 23 31 39 47 55 63). Если число , образованное 6 младшими разрядами, множителя является членом .1 Матрицы, то узлом управления возе5уясдается выход 27 .и на коммутатор поступает Шожимое в прямом коде без сдвига. Если число, образованное 6 младшими разрядами множителя является членом 11 матрицы, то на коммуTaiTop подается с выхода 28 блока управления 21 утроенное множимое (для III и ly матриц соответственно упятеренное и усемеренное множимое с 24 и 25 управляющих выходов). Если при зтом это число является, членом одной из матриц V,VI или VII 9 17 25 33 41 49 57 11 19 27 35 43 51 59 1321 29 37 45 53 61 15 23 31 39 47 55 6310 18 26 34 42 50 5В 1422 30 38 46 54 62/ V1ID2 (,4 12 20 28 36 44 S2 60) , то на коммутатор одновременно с сигналами с выходов 27-30 подаются с выходов 31 (для матриц V) 32 (для матриц VI), 33 (для матрицы VII) управляющие сигналы, производящие сдвиг :входного кода на 0;1 или 2 разряда

влево, в результате чего на сумматор подается одно из чисел 1,2,...,7,

Если затем это число является членом одной из матриц Вт VIII,IX,X или XI, где VIII BO/ 8....

В. /24,2531

48,4955;

16. ...23 32....39J

X 82 (40.,41. .. .47) XIВд (56,57... .63), то вырабатывается соответственно на выходах 23-25, 19,20 или 26 управляю щий сигн.ал и на коммутатор подается множимое, умноженное на 8, 24,40 или 56, Если при этом это число является членом одной из матриц К,. XII,XIII, XIV Ко /8,9...15 XII24,25...31 40,41... 47 56,57...63 KI 16,17,...23 ,4955/ Ki f-зт VTV - то одновременно.С выходами 23-25 воз буждаются выходы 31,32,33, производящие сдвиг поданных на входы коммутатора сдвинутых кодов числа на 0; или 2 разрядка влево, передавая в сум матор промежуточное произведение, t aBHpe множимому, умноженному йа числа (1,2,.. .7) X 8, в результате чего в, сумматоре релазйруется искомо прои36едение. Например, пусть 6 млад ших разрядов 1 1ожителя составляет чис ло 28, это число является членом II, VII,IX и KII матриц, т.е. будут выра ботаны сигналы (на выходах) 27,33, 24 и 31, в результате.чего на коммутатор ,20 сигналрм е вьохода 27 подается множимое с блока вьвдачи 11 в прямом коде без сдвига, управляющим сигналом с выхода 33, оно, сдвинется на 2 разряда влево в коммутаторе 20 и на сумматор 22 будет передано число ,4. Затем сигналом с выхода 24 с блока управления 21 через блок выдачи 16 на коммутатор 20 поступит утроенное множимое с блока -8 со сдвигом на 3 разряда влево, т,е, множимое, умноженное йа число 24, так как при этом сигнал управления с выхода 31 производит через коммутатор 20 его передачу в сумматор 22 без сдвига, то в сумматоре к числу 4М прибавится число 24М,

где М - множимое, образуя искомое произведение 28М. нaлoгичным образом .реализуется умножение и на любое другое число от О до 2.

Предлагаемое устройство практически на таком же количестве оборудования, что и прототип, реализует

операцию умножения в два раза быстрее. Формула изобретения Устройство для умножения, содержащее блок управления, регистр множителя, сумматор, блоки . произведения множимого на константы, блоки выдачи в сумматор произведения множимого на константы со сдвигом влево и без сдвига, причем выходы регистра множителя соединены со входами блока управления, отличаю ще ее я тем, что, с , целью повышения быстродействия, в устройство введены блоков ввдачи в сумматор произведения множимого На,константы, 2 () блоков произведений множимого на константы 2 рт+1 (,1,..., (), коммутатор сдвига.кода, () выходов первой и второй rpyrifi выходов блока Управления соединены со Ёходами управления блоков выдачи в сумм.атор произведения множимого на константы со сдвигом на 2 разрядов влево и без сдвига соответственно, информационные входы .которых соединен.ы с выходами блока произведения множимого на константу (2рт+1), выходы блоков выдачи в сумматор произведения множимого на константы со сдвигом ча 2 разрядов влево и без сдвига соединены с. информационными входами коммутатора сдвига кода, (Е-1)-е выходы третьей и четвертой групп .выходов блока управления соединены соответственно с (-1)-ми входами первой и второй группы управляющих вхЬдовкомйутатора сдвига ода, выходы которого соединены со хоДами сумматора. Источники информации, принятые во нимание при экспертизе1. Субье-Ками А, Двоичная тех- . ика и обработка информации, М., Мир., 1964, 2. вторское свидетельство СССР 255648, кл. ССГб. F 7/54, 1968.

662940

fl(m) В(С

Л{т

П

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения на п-разрядов множителя | 1977 |

|

SU717764A1 |

| Устройство для умножения на разрядов множителя | 1978 |

|

SU741265A1 |

| Устройство для умножения на -разрядов множителя | 1977 |

|

SU750487A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Устройство для умножения | 1977 |

|

SU675422A1 |

| Устройство для вычисления элементарных функций | 1974 |

|

SU560229A1 |

| Множительно-сдвиговое устройство | 1982 |

|

SU1013951A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для умножения | 1986 |

|

SU1339551A1 |

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

Авторы

Даты

1979-05-15—Публикация

1977-07-04—Подача