I

Изобретение относится к вычислителЫ ной технике и .может быть иснользоаано в арифметических устройствах цифровых вычислительных машин.

Известно устройство для умножения, содержащее сумматор, регистр множителя блоки произведешш маожи1 « го на константы, блоки выдачи произведения MBD-, жнмого на константы со .сдвигом и без, сдвига l .

Однако это устройство отличается сложностью и низким быстродействием.

Наиболее близким по технической сущности к изобретению является устройство, содержащее сумматор, блок управления,

регистр множителя

(

(гдек&1, ,е е„ ч-л«кн )

блоков произведения множимого на константы (2pi { ) , (где р.; - 0,1,2..., ( «у -1), выходы которых соединены с информйоионными входами соответствующих блоков выдачи в сумматор произведения

множимого на константу со Сдвигом на Щ. где (0.i.,re -eosf2(2piH)),

. ,,..,e,t -eoif,())},

целая часть разрядов влево, управляющие входы которых соединены в соответствующими выходами первой группы выходов блока управления, первый выход второй группы выходов которого соединен со входом младщего разряда сумматора, выходы М разрядов регистра множителя соединены со входами блока управления i2j

Недостатком данного устройства является сложность.

Цель изобретения - упрощение устройства.

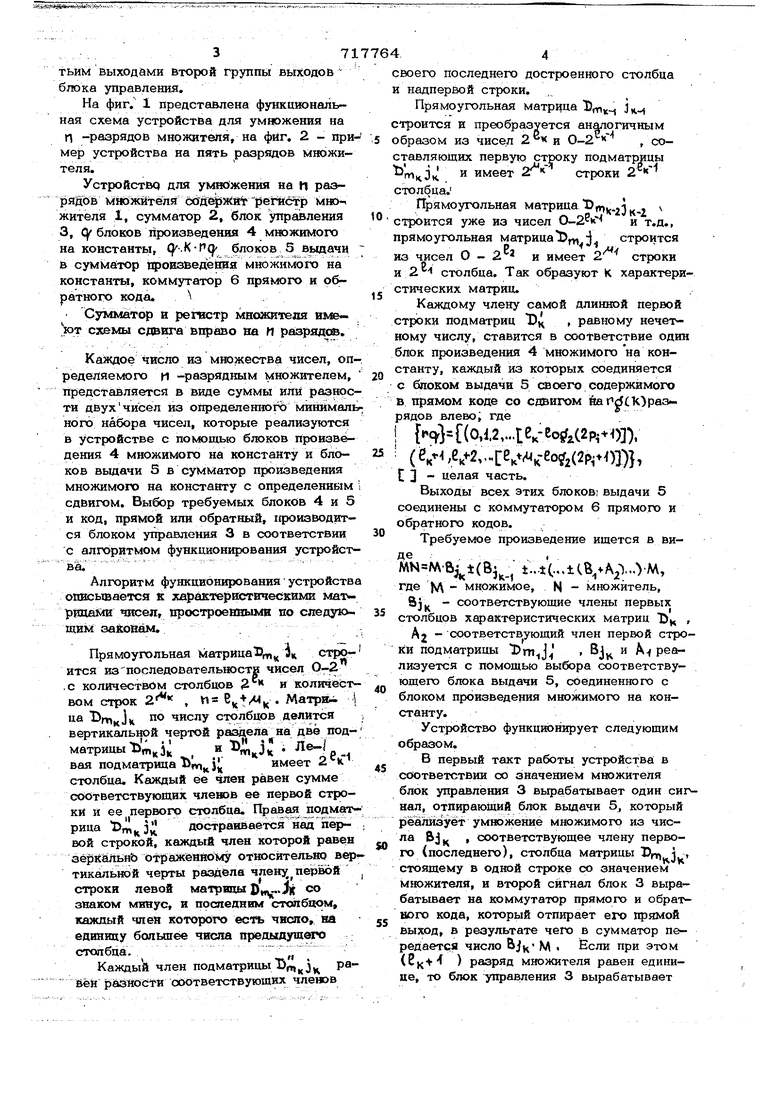

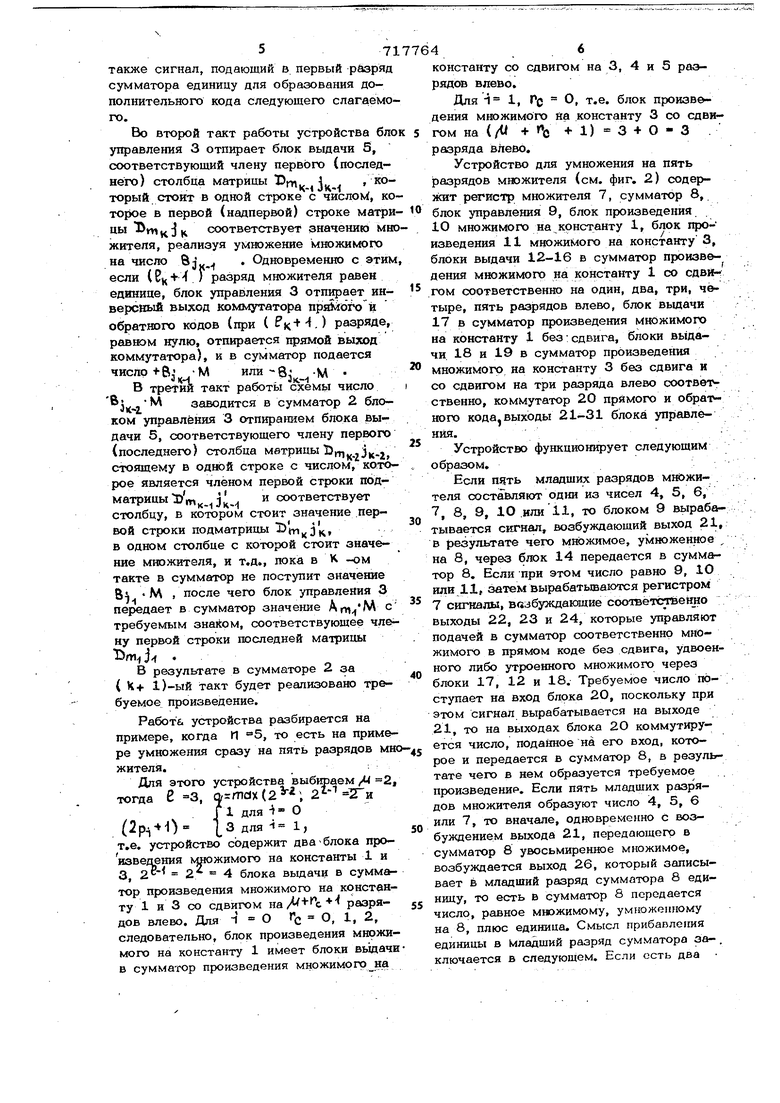

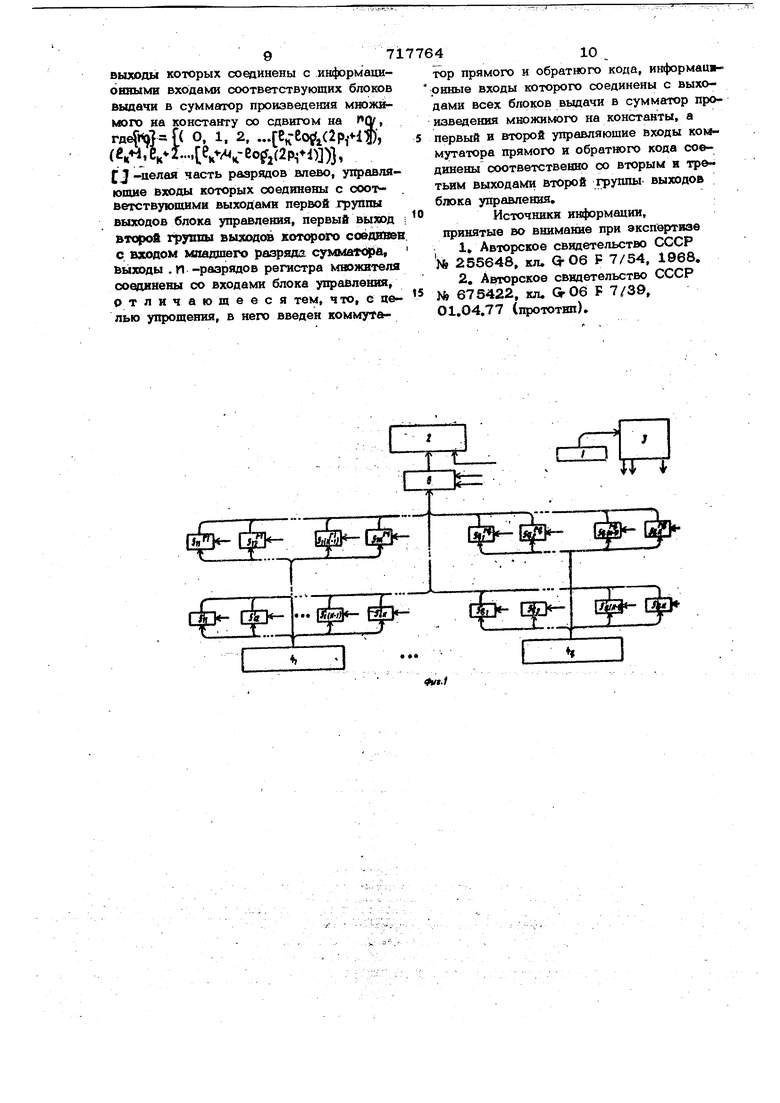

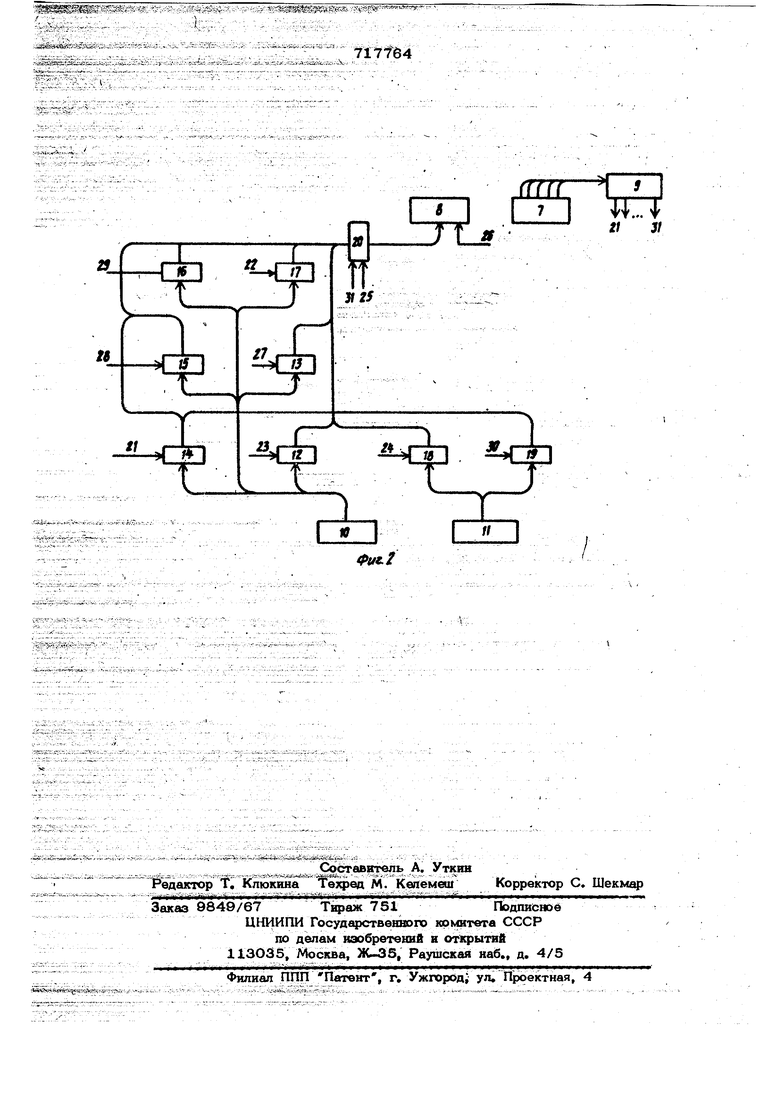

Для этого в него введен коммутатор прямого и обратного кода, информационные входы которого соединены с выходами всех блоков выдачи в коммутатор произведения множимого на константы, а первый и второй управляющие входы коммутатора прямого и обрат1юго кода соединены соответственно со вторым и тротьим выходами второй группы выходовблока управления. На фиг. 1 представлена функаж нальная схема устройства для умножения на П -разрядов множителя, на фиг. 2 - при мер устройства на пять разрядов множителя. Устройства для умножения на ц разрядов множйтгёля со дбрясйг periHCTjp мно-ч жителя 1, сумматор 2, блок управления 3, су блоков произведения 4 множимого на константы, (J-.K-fC блоков 5 выдачи в суммйтор тфоЕЗБедения множимого на константы, коммутатор 6 прямого и обратного кода. . Сумматор Е регистр множттгеля вмв- Ът схемы сдвига вправо на И разрядов. Каждое число из множества чисел, оп ределяемого ц -разрядным множителем, представляется в виде суммы или разнос ти двухчисел из определенного минималь ного набора чисел, которые реализуются в устройстве с помощью блоков произведения 4 множимого на константу и блоков вьщачи 5 в сумматор произведения множимого на константу с определеннБтм сдвигом. Выбор требуемых блоков 4 и 5 и код, прямой или обратный, 1фоизводится блоком управления 3 в соответствии с алгоритмом функционирования устройст ва. . Алгоритм функционирования устройств описывается к характеристическими матр|ща$«1 чисел, простроеиными по следующи за&оВам. Прямоугольная матрица Km к к строится изпоследовательност;р чисел Р-2 . с количеством столбцов 2 и количест вом строк , П + /M . Матрви ца по числу столбцов делится вертикальной чертой раздела на две подматрицы 1),, j Леимеет...Рч--. вая подматрица т У столбца. Каждый ее член равен сумме соответствующих члеюэв ее первой строки и ее первого столбца. Правая подмат рица достраивается над niipвой строкой, каждый член которой равен зёркаль.нЬ отррйжёНйбму относительно вер тикальной черты член пер1Ёюй строки левой матрицы )н.К со зваком минус, и последним столбцом, каждый член которого есть число, на единицу большее числа предыдущетю столбца. Каждыми член подматрицы 13n,jj раВён разности соответствующих членов воего последнего достроенного столбца надпервой строки. Прямоугольная матрцца im троится и преобразуется аналогичным бразом из чисел 2 я 0-2 , сотавляющих первую ст; о строку подматрицы 2 СТРОКИ И имеет толбца. Прямоугольная матрица D..,А троится уже из чисел О-2 и т.д., рямоугольная матрица j строится з чисел 0-2 и имеет 2 строки столбца. Так образуют К характеритических матриц. Каждому члену самой длинной первой троки подматриц D , равному нечетному числу, ставится в соответствие один блок произведения 4 множимого на константу, каждый из которых соединяется с блоком выдачи 5 своего содеряшмого в прямом коде со сдвигом fendtX) разрядов влевоi где K}(Oti2,...(), (,2,.()}, С 3 целая часть. Выходы всех этих блоков выдачи 5 соединены с коммутатором 6 прямого и обратного кодов. Требуемое произведение ищется в виде, MN AAaj ±(B t...tc...±ce/Ap,..) м, где }V - множимое, М - множитель. - соответствующие члены первых Чк- . столбцов характеристических матриц Оц , А2 - соответствующий член первой строки подматрицы . Bj и Л реализуется с помощью выбора соответствующего блока выдачи 5, соединенного с блоком произведения множимого на константу. Устройство функционирует следующим образом. В первый такт работы устройства; в соответствии со значением множителя блок управления 3 вьфабатывает один сипнал, отпирающий блок выдачи 5, который рёайИзуёт умножение множимого из числа Bj ц , соответствующее члену первого (последнего), столбца матрицы 75, j , стоящему в одной строке со значением множителя, и второй сигнал блок 3 вырабатывает на коммутатор прямого и обратиого кода, который отпирает его прямой выход, в результате чего в сумматор передается число BjKМ Если при этом ( ( ) разряд множителя равен единице, то блок управления 3 вырабатывает также сигнал, подающий в первый разря сумматора единицу для образования дополнительного кода следующего слагаемо го. Во второй такт работы устройства бл управления 3 отпирает блок выдачи 5, соответствующий члену первого (последнего) столбца матрицы Ю. .ко торый стоит в одной строке с чйслок, к - Topoe в первой (надпервой) строке матр цы j j ц соответствует значению мн жителя, реализуя умножение множимого на число SJM. . Одновременно с эти если ( BX + Ч Г разряд множителя равен единице, блок управления 3 отпирает инверсвый выход коммутатора прШоЛ)и обратного кодов (при ( ) разряде, peiBHOM нулю, отпирается прямой выход коммутатора), и в сумматор подается число -В М или -вз -М В третий такт работы схемы число 3, заводится в сумматор 2 блоком управления 3 отпира}шем блока выдачи 5, соответствующего члену первого (последнего) столбца матрицы Ьт.,.3к.2 стоящему в одной строке с числом, кото рое является членом первой строки подматрицы и соответствует столбцу, в котором стоит значение первой строки подматрицы , в одном столбце с которой стоит значение множителя, и т.д., пока в К -ом такте в сумматор не поступит значет1е В 4 М , после чего блок управления 3 передает в сумматор значение Лп.М с требуемым знаком, соответствующее члену первой строки последней матрицы Ът J4 . В результате в сумматоре 2 за ( K-f 1)-ый такт будет реализовано требуемое произведение. Работй устройства разбирается на примере, когда П 5, то есть на примере умножения сразу на пять разрядов мн жителя. Для этого устройства выбтэаем / 2, тогда 6 3, ( 2 2 и Г для О () |3 для- 1, т.е. устройство содержит два-блока произвепения шюжимого на константы 1 и 3, 2 2 4 блока выдачи в сумматор произведения множимого на константу 1 и 3 со сдвигом разрядов влево. Для 1 О Гс О, 1, 2, следовательно, блок произведения множимого на константу 1 имеет блоки вьщачи в сумматор произведения множимого на константу со сдвигом на 3, 4 и 5 разрядов влево. Для , PC О| т.е. блок проиэве дения множимого йа константу 3 со сдвигом на ( -f + 1) 3 4 О - 3 разряда влево. Устройство для умножения на пять разрядов множителя (см. фиг. 2) содержит регистр множителя 7, сумматор 8, лд,ъс& я. я дх,/ л. ivi|« Jiixi. JL f J It I r блок управления 9, блок произведения. 10 МНОЖИМОГО на константу 1, блок произведения 11 множимого на константу 3, блоки выдачи 12-16 в сумматор произведения множимого на константу 1 со сдвигом соответственно на один, два, три, четыре, пять разрядов влево, блок вьщачи 17 в сумматор произведения множимого на константу 1 без: сдвига, блоки вьщачи 18 и 19 в сумматор произведения множимого на константу 3 без сдвига и со сдвигом на три разряда влево соответственно, коммутатор 20 прямого и обрат ного кода, выходы 21-31 блока управления.. Устройство функционирует следующим образом. ЕСЛИ пять младщих разрядов множителя составляют одни из чисел 4, 5, 6, 7, 8, 9, 10 .или 11, то блоком 9 вырабатывается сигнал, возбуждающий выход 21, в результате чего множимое, умноженное / на 8, через блок 14 передается в сумматор 8. Если при этом число равно 9, 10 или 11, затем вырабатываются регистром 7 сигналы, возбуждающие соответстаенно выходы 22, 23 и 24, которые управляют подачей в сумматор соответственно множимого в прямом коде без сдвига, удвоенного либо утроенного множимого через блоки 17, 12 и 18. Требуемое число по- ступает на вход блока 20, поскольку при Этом сигнал Вырабатывается на выходе 21, то на выходах блока 2О коммутируется число, поданное на его вход, которое и передается в сумматор В, в результате чего в нем образуется требуемое произведенир. Если пять младщих разрядов множителя образуют число 4, 5, 6 или 7, то вначале, одновременно с возбуждением выхода 21, передающего в сумматор 8 увосьмиренное множимое, возбуждается выход 26, который записывает 6 младший разряд сумматора 8 единицу, то есть в сумматор 8 передается число, равное множимому, умноженному на 8, плюс единица. Смысл прибавления единицы в Младщий разряд сумматора за-, ключается в следующем. Если есть два ( -i a s sOiBfep - - -,- jJSJS C -- „ ---- -,it - - 77 .числа в двоичном коде АИ С , то, чтобы :вычесть из А число С , надб образо. вать дйшэлнгтёпьный код числа С и при- ть его к числу А. Допрййительный kbfl - это обратный код числ1айлюс единица в младшем разряде Например, C«OOi1O , обратный код ilOOi , дополнительный код 140iO, f. е., чтобы раэрадюсть А и С надо Вьшбл нить Ач-С + 1 , где с - обрат1яь1й код; чис Ла« Раэяюсть может быть Получена как ( )+6 , что и реализуется устройством при получении произведенияпутем радности двух П1Ш1Ш тйГ1 Ш1едёний. Затем, в зависимости 6т Значения множителя 4, 5, в или 7, возбуждакугся выходы 21, 30, 29 или 22 блока 9. Пр этом на вход блока 2О поступает черей блоки 13, 18, 12 или 17 соотбетственно либо прямой код учетверенного множимогр (блок 13, уп|равлЯ1бщий для числа 4), либо тфямой код зйгроенно го множимого (блок 18, управляюишй вход 24 для числа,5), либо удвоенное множимое в прямом коде (блок: 12, управляющий вход 23 для числа 6), либо ШОЖимое в прямом коде без сдвига (блок 17,,угфавляквций вход 22 для чи)о ла 7), Так как нри Этом возбуйсйён вход 25 блока 2О, то на его выходах I коммутфуется обратный код числа, поga ipro на его входы, которое, пер едаваярь в сумматор 8, вычитаете, из йафвксироБавврго там рвзупьтвта 8/И-4М, 8AW3AV. ИЛИ 8AWM для числа 4,5,6 и 7 соолсвё стветвво, М - мвож&. мое), Если пять младших раз)ядов множителя составляют одно из чисел 12 - 19 28 - 31, 20 - 27, то аналогичным об1ШЗОКГ сй11ааМШ уп1:ШдёШя с 1 блока б на входы 28, 29 и 30 через блоки 16, 15 9 19 йёрЩШ Ш ШШШ&ё умноженное на 16, 32 или 24 оооТЬёт стщнно. Если эти пять разрядов маожи„ Шя ставляют число 17 или 25, то затем возбуждаются выходы 25 и 22 бхюка 9, и через блоки 17 и 20 йаржиМое прибавляется К содержимому суммам тора 4, реализуя умножение ва TpeQre.; КЮе число. - ; --. - : --,. ;--; -;:- Если пять младших разрядов множшге J ля . или 26, то воэ буждаются выходы 25 и 23 блока 9 и через блок 12, через блок 20, коммутирутрший на своих выходах прямой код входящей величины, удвоёшюе ,-i-.-V . ---. - -- -- - . Г-.--..-.--Ъ--- - --:- - -.:.- ,-4,-.-:;i ; ; v:ii; -i. В прямомкоде передается в сумматор 4 4 ЕСЛИ множитель равен 19 или 27,, то возбуждаются управляющие выходы 24, 25, утроенное Множимое в прямом коде через блок 18 и блок 2О, коммутирующий на своих выходах прямой код своей вход-, ной величины, передается в сумматор 8, в результате чего в сумматоре 4 реализуется требуемое произведение; Если пять младших разрядов множителя составляют число 12 - 15, 28 - 31, 20 23, то одновременно с выдачей в сумматор 8 множимого, умноженного соответственно на 16, 32, 24, в младший разряд сумматора 4 сигналом с выхода 26 заводится единица, то есть в сумматор передается число , 32М+1, 24М+1), где М мноЖЕмое. Прибавление; этой единицы не увеличивает Времени суммирования В сумматоре, так как млад-, ший разряд чисел 16M, 32М и 24М всегда равен нулю. Затем, если множитель равен 12, 28 ЗО, возбуждаются выходы 21, 15 и 31 блока 9j в результате чего через б.лок 13 на выходы блока 20 поступает учетверенное мрожимое, которое блоком 20 инвертируется и уже в обратном коде поступает в сумматор, вычитаясь из зафиксированного там числа, реализуя в результате1 умножение множ його на числа 12, 28 или 2О, Если пять млйдших р рядрв множителя равны 13, 29, 21 или 14, 30, 2.2 шл 15, .31, 23, то умножение на эти. числа провзводнтс:я аналогичным образом с помощью сигналов управдёнияс выходов 23, 22., к 21соответственно (блоками ссютветственио 18, 12 и 17 с последующим инвертированием в 1блс)1се 20 л подачей в сумматор в обратном иоде. Умножение на множитель, равный 1,2 или 3, осуществляется подачей соответствующих произведений в сумматор 8 сигналами с выходов 21, 22 и 23, Первые выходы его при этом не возбуждаются. Благодаря данному техническому рещению предложенное устройство примерно в два раза проще известного. Формула изобретени я Л Устройство для умножения на и -разрядов мв|Ь жнтеля, содержащее сумматор, блок управле1шя, регистр множителя qrmox (2, 2, ), , . блоков П{)рвзведенвя множимого на константы (aPi + 1); где Pi « 0,1..., (| -1), выходы которых соединены с информаии-онвыми входами соответствующих блоков выдачи в сумматор произведения множкмого на константу со сдвигом на , гдЦНй и О, 1. 2, ...енео(2р..Ч1), (6,4,6, l...e v -eogfj())}, fJ -целая часть разрядов влево, управляющие входы которых соединены с соответствующими выходами первой группы выходов блока управления, первый выход второй грунта выходов соёдивев с входом мпадаюго разр5ада сумма1 д{)1, Выходы .п -разрядов регистра множителя соединены со входами блока управления, отличающееся тем, что, с целью упрощения, в него введен коммутатор прямого и обратного кода, информацирнные входы которого соединены с выходами всех блоков выдачи в сумматор произведения множимого на константы, а первый и второй управляющие входы коммутатора прямого и обратного кода соединены соответственно со вторым и тре тьим выходами второй rpymibr выходов блока управления. Источники информации, принятые во внимание при экспертизе 1 Авторское свидетельство СССР № 255648, кл, т06 F 7/54, 1968. 2, Авторское свидетельство СССР N 675422, кл. СзгОб F 7/39, 01,04.77 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения на разрядов множителя | 1978 |

|

SU741265A1 |

| Устройство для умножения | 1977 |

|

SU662940A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

J3

I

Т4Г

, -7l7fe4гптг Ф1... г г / п у J/

Авторы

Даты

1980-02-25—Публикация

1977-06-09—Подача