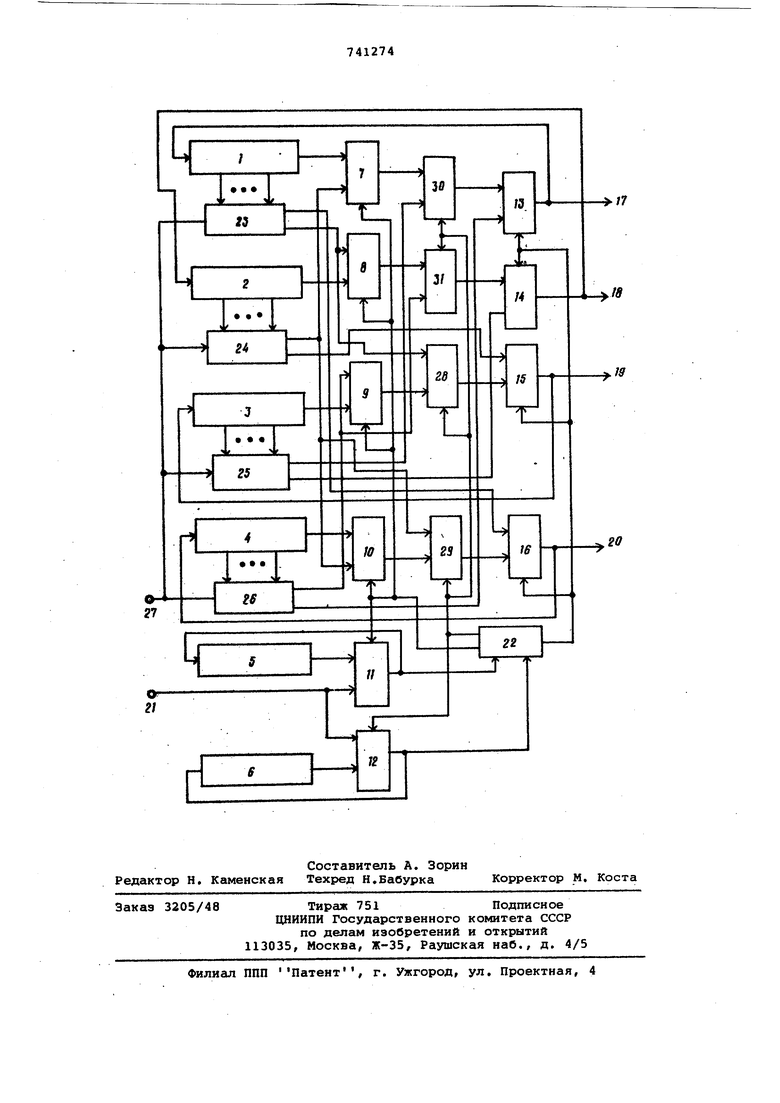

Цель достигается тем, что предлагаемое устройство дополнительно содержит три регистра, два коммутатора и одинадцать сумматоров, причем выходы разрядов четвертого и пятого регистров соединены с соответствующими входами третьего и четвертого коммутаторов, первые входы четвертого, пятого и шестого сумматоров соединены с выходами соответственно чет вертого, пятого и шестого регистров первые выхады первого, второго, Третьего и четвертого коммутаторов соединены соответственно с первыми входами седьмого, восьмого, девятого и десятого сумматоров и со вторыми входами третьего, второго, пятого и четвертого сумматоров, а их вторые выходы - соответственно с первыми входами одиннадцатого, двенадцатого, тринадцатого и четырнадцатого сумматоров, выходы второго, третьего, чет вертого и пятого сумматоров соединены соответственно со вторыми входами девятого, десятого, седьмого и восьмого сумматоров, а выхода седьмого, восьмого, девятого и десятого сумматоров соединены соответственно со вторыми входами двенадцатого, одиннадцатого, четырнадцатого и тринадцатого сумматоров, выходы которых являются выходами устройства, причем выходы одиннадцатого и двенадцатого сумматоров соединены соответственно со входами пятого и четвертого регистров , второй вход шестого сумматора соединен со вторым входом устройства, а его выход - со вторым вко дом блока управления и входом шестого регистра, управляющие входы четвертого, пятого и шестого сумматоров соединены с первым выходом блока управления, соединенного вторым выходом с управляющими, входами первого, седьмого, восьмого, девятого и десятого сумматоров, а третьим - с упг равляющими входами одиннадцатого, двенадцатого, тринадцатого и четырнадцатого сумматоров. Вычисление синусно-косинусных произведений выполняется по алгоритму. . . . . a i e H ®i-5ii fi Cti QA-fe,, signe - ,2i-sign qi,.(., p., , A В С 0, i - номер итерации, Vi - угловая достоянная, равная arc t 2 На чертеже представлена блок-схема предлагаемого устройства. Она включает регистры 1-6, сумма торы 7-16, выход 17 (первый выход), выход 18 (второй выход), выход 19 (третий выход), выход 20 (четвертый выход), вход 21 угловой постоянной (второй вход),: блок 22 управления, коммутаторы 23-26, вход 27 управляющего сигнала (-первый вход), сумматоры 28-31. Устройство работает следующим о6разом. Операнды А, , , , , q хранятся в регистрах 1-6; по команде .1-й итерации из блока управления по входу 27 все коммутаторы соединяют, свои первые выходы с выходами соответствующих разрядов регистров таким образом, что на входы блоков 7-10, 2831 поступают операнды, умноженные на величину 2 , а свои вторые выходы таким образом, чтобы на входы блоков 13-16 поступили, операнды, умноженные на величину 2 . С выходов младших разрядов регистров 1-6 олеранды поступают на входы сумматоров 7-12, где в соответствии со значениями и 2-1 суммируются (вычитаются) с величкцамк, которые поступают с выходов блоков 23-26 и из запоминающего устройства по входу 21 соответственно. С выходов сумматоров 7-10 результаты поступают на входы блоков 28-31, где суммируются (вычитаются) в соответствии с 2- одерандами, умноженными на величину 2 С выходов блоков 2831 результаты поступают на входы блоков 13-16, где в соответствии с сигналом () суммируются (вычитаются) с операндами, умноженными на величину 2 . Результаты операций А, , С Ч- /Dl4 /®-iM Q-fM записываются в регистры 1-6 соответственно. Константы Ч поступают из запоминающего устройства по входу 21, значения &-1Ч-1 и Q-i. подаются на входы блока управления 22, где используются дли определения значений (), 2. и-и) и произведения t. . (-tH- f) которые будут выдаваться на соответствующие выходы блока на (1+1)-й итерации. Процесс повторяется до выполнения заданного количества итераций. В конце операции результаты образуются на выходах 17-20. Эффективность предлагаемого изо- бретения заключается в сокращении времени вычислений в три раза при увеличении объема оборудования примерно в два раза. Формула изобретения Устройство для вычисления синуснокосинусных произведений, содержащее три сумматора, три регистра, два коммутатора, блок управления, при этом выходы разрядов первого и второго регистров соединены с соответствующими входами первого и второго коммутаторов , управляющие входы которых соединены с первым входом устройства, входа .первого и второго регистров

соединены с первым и вторым выходами устройства, а третьего регистра - с первым входсм блока управления и выходсм первого сумматора, первый вход которого соединен с выходом третьего регистра, а второй - со вторым вхо-: дом устройства, первые входы второго и третьего сумматоров соединены соответственно с выходами первого и второго регистров, а их управляющие входы - с первым выходом блока управ ления, отличающее с/я тем, что, с целью повышения быстродействия, устройство дополнительно содержит три регистра, два коммутатора и одиннадцать сумматоров, причем выходы разрядов четвертого и пятого регистров соединены с соответствующими входами третьего и четвертого коммутаторов, первые входы четвертого, пятого и шестого сумматоров соединены с выходами соответственно четвертого, пятого и шестого регистров, первые выходы первого, второго, третьего и четвертого коммутаторов соединены соответственно с первыми входами седьмого, восьмого, девятого, десятого сумматоров, и со вторыми входами третьего, второго, пятого и четвертого сумматоров, а их вторые выходы с первыми входами соответственно одиннадцатого, двенадцатого, тринадцатого и четырнадцатого сумматоров, выходы второго, третьего, четвертого и пятого сумматоров соединены соответственно со вторыми входами девятого, десятого, седьмого и восьмого сумматоров, а выходы седьмого, восьмого, девятого и десятого сумматоров соединены соответственно со вторыми входами двенадцатого, одиннадцатого, четырнадцатого и тринадцатого сумматоров, выходы которых являются соответственно -первым, вторым, третьим и четвертым выходами устройства, причем выходы одиннадцатого и двенадцатого сумматоров соединены со входами соответственно пятого и четвертого регистров, второй вход шестого сумматора соединен со вторым входом; устройства, его выход - со вторым входом блокауправления и входом шестого регистра, управляющие входы четвертого, пятого и шестого сумматоров соединены с первым выходом блока управления, соединенного вторым выходо с управляющими входами первого, седьмого, восьмого, девятого и десятого сумматоров, а третьим - с управляющими входами одиннадцатого, двенадцатого, тринадцатого и четьфнадцатого сумматоров.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 445042, кл. G Об F 7/38.

, 2. СистемаДИВИК для реиения сложных навигационных задач Электроника, 18, 1966, с. 3038 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1262483A1 |

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1280613A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU911519A1 |

| Арифметическое устройство | 1981 |

|

SU1012240A1 |

| Устройство для умножения элементов поля Галуа GF(2 @ ) при образующем полиноме F(х)=х @ +Х @ +х @ +х @ +1 | 1989 |

|

SU1716504A1 |

| Процессор | 1981 |

|

SU962964A1 |

| Устройство для вычисления полинома | 1980 |

|

SU885997A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Арифметическое устройство в системе остаточных классов | 1983 |

|

SU1107122A1 |

Авторы

Даты

1980-06-15—Публикация

1978-01-23—Подача