54) УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

1

Изобретение относится к импульсной технике, а более конкретно к делителям частоты, предназначено для автоматического деления частоты импульсов на переменный коэффициент деления и может найти применение в системах управления шаговым приводом, в системах фазовой автоподстройки, в -автоматических стабилизаторах частоты, в цифровых вычислительных устройствах автоматических регуляторов,, в коммутирующих устройствах телеметрической аппаратуры, в устройствах с программным управлением и т. д.

Известны управляемые делителичастоты, обеспечивающие программное изменение коэффициента деления.

Наиболее близким по технической сущности является управляемый делитель частоты, содержащий шину источника входного сигнала, соединенную со входом блока разрешения деления,. и вторую входную шину, соединенную со входом вентиля, управляющий вход которого связан с первым выходом блока разрешения деления, выход же вентиля соединен со счетным- входом пересчетного блока, разрядные

входы которого подключены к выходу устройства записи кода, а второй выход блока разрешения деления подведен к первому входу логического элемента ИЛИ I. Недостатками описанного делителя являются: во-первых, занйженность быстродействия из-за того, что при.завершении цикла деления делитель лишь подготавливается к

10 приему кода сле.дующего коэффициента деления Кд, для чего устройство о записи кода сбрасывается на О, при этом увели 1ивается время ввода следующего Кд и уменьшается скорость

5 деления; выходной сигнал появляется с задержкой во времени по отношению к моменту прихода команды на разрешение деления, и устройство предназначено для приема обратного кода;

20 и во-вторых, ограниченность функциональных возможностей и области применения малым диапазоном изменения коэффициента деления, поскольку максимальное его значение Кд,,

25 1, где ti- число разрядов пересчетного блока, совпадение состояний которых выявляется, а также тем, что он не предусматривает ввода последовательного кода коэффициента

30 деления.

Целью изобретения является повышение быстродействия при одновременном расширении функциональных возможностей.

С этой целью в управляе1иый делитель частоты, содержащий устройство записи кода, на вход которого подан сигнал ввода коэффициента деления, а выход соединен с разрядными входами пересчетного блока, блок разрешения деления, на вход которого подан сигнал разрешения, вентил Первый вход которого соединен с первым выходом блока разрешения деления, второй - с шиной источника входного сигнала, а выход - с счетным входом пересчетного блока и элемент ИЛИ, первый вход которого подключен ко второму выходу блока разрегиения деления, введен формирователь импульсов, включенный между выходом пересчетного блока и вторым входом элемента ИЛИ, и блок вентилей, включенный между выходом элемента ИЛИ и входами устройства записи кода коэффициента деления, первый дополнительный вход которого подключен к шине ввода последовательного кода коэффициента деления, а второй соединен с выходом пересчетного блока, вход сброса которого подключен ко второму выходу блока разрешения деления, при этом сигнальный вход блока вентилей соединен с шиной ввода прямого параллельного кода коэффициента деления,

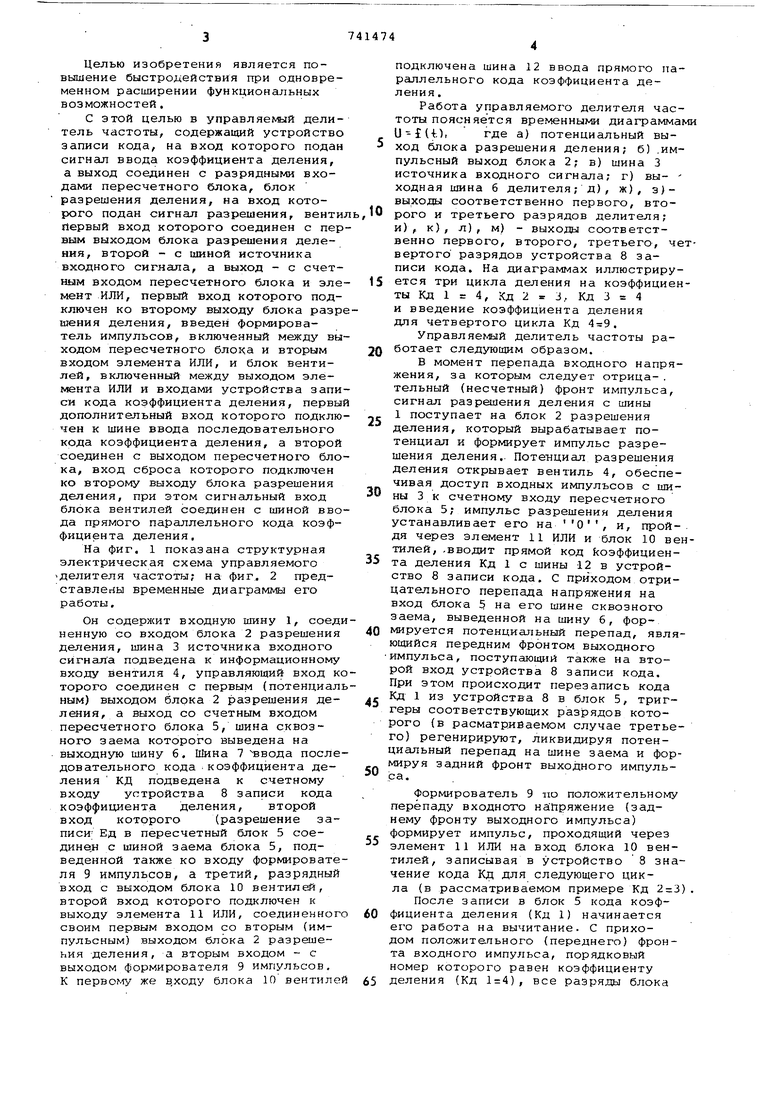

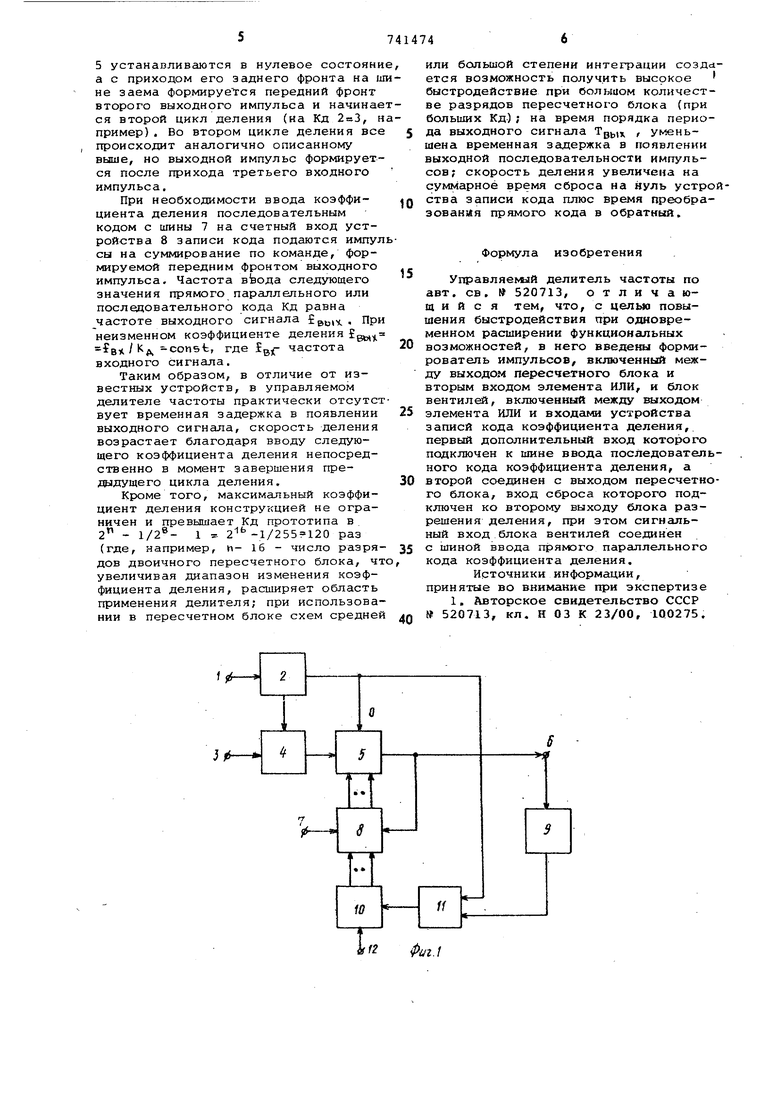

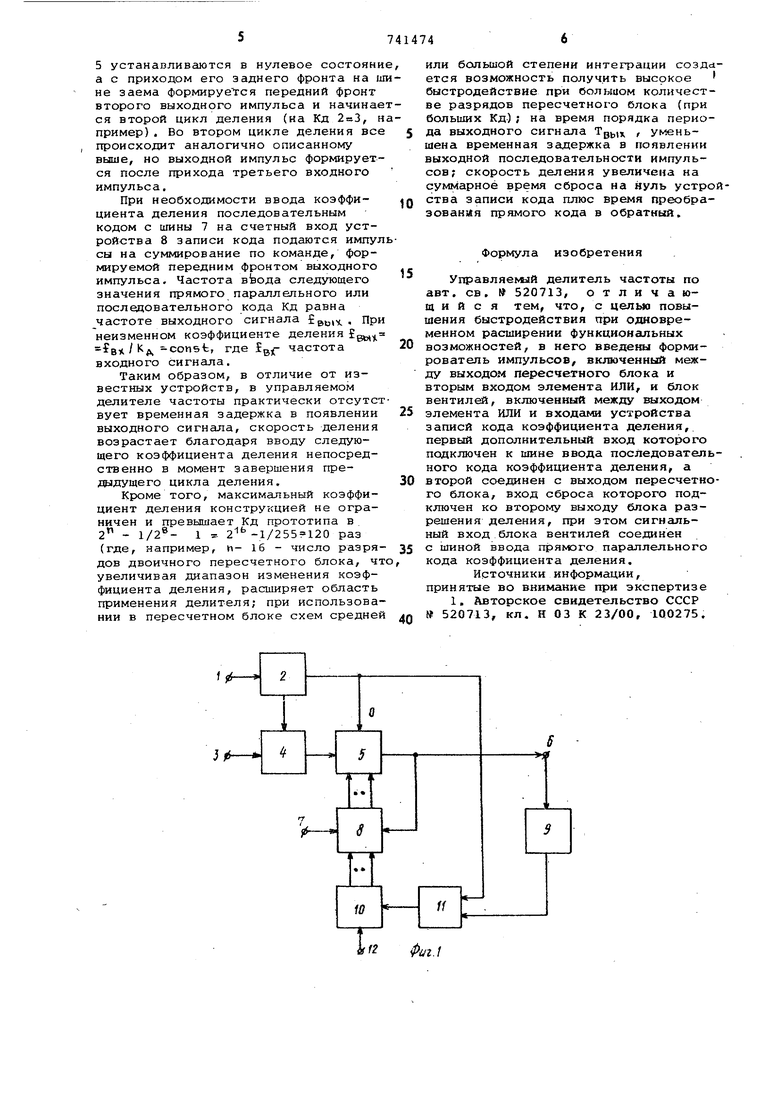

На фиг, 1 показана структурная электрическая схема управляемого - делителя частоты; на фиг. 2 представлены временные диаграммы его работы.

Он содержит входную шину 1, соединенную со входом блока 2 разрешения деления, шина 3 источника входного сйгнала подведена к информационному входу вентиля 4, управляющий вход которого соединен с первым (потенциальным) выходом блока 2 разрешения деления, а выход со счетным входом пересчетного блока 5, шина сквозного эаема которого выведена на выходную шину 6, Шина 7 ввода последовательного кода коэффициента деления КД подведена к счетному входу устройства 8 записи кода коэффициента деления, второй вход которого (разрешение записи- Ед в пересчетный блок 5 соедине.н с шиной заема блока 5, подведенной также ко входу формирователя 9 импульсов, а третий, разрядный вход с выходом блока 10 вентилей, второй вход которого подключен к выходу элемента 11 ИЛИ, соединенного своим первым входом со вторым (импульсным) выходом блока 2 разрешения деления, а вторым входом - с выходом формирователя 9 импульсов, К nepBOf-iy же в.ходу блока 10 вентилей

подключена шина 12 ввода прямого параллельного кода коэффициента деления.

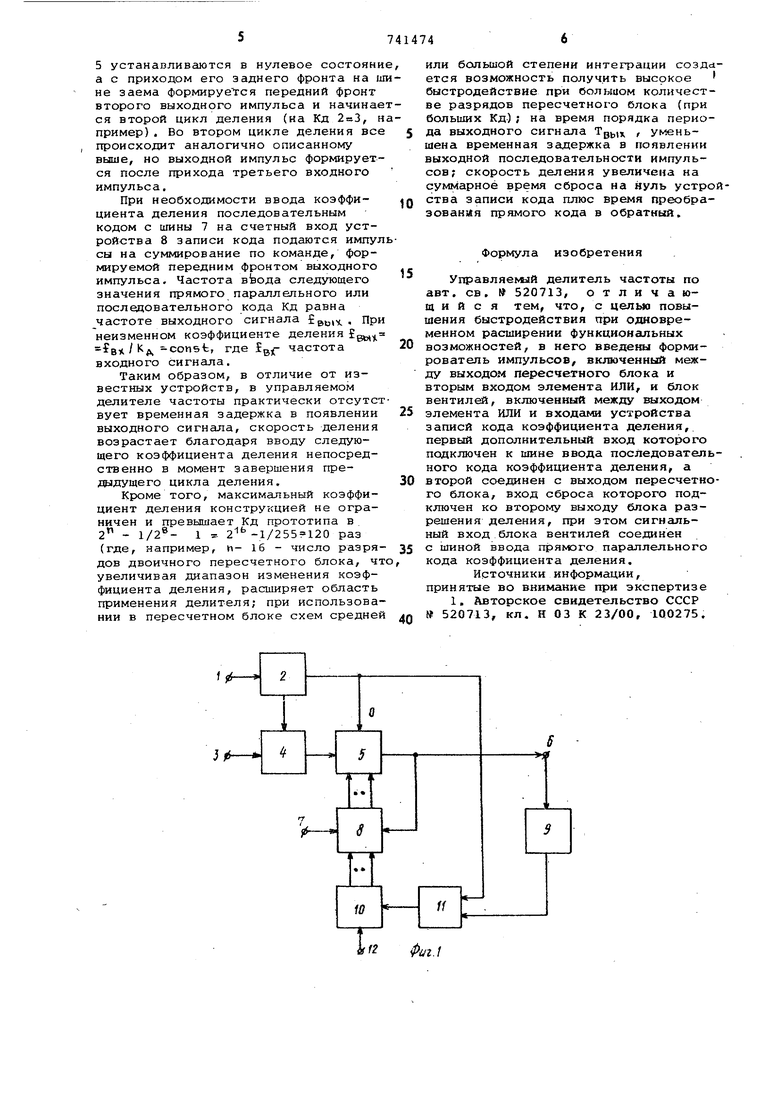

Работа управляемого делителя частоты поясняется временными диаграмма U-f(i)r где а) потенциальный выход блока разрешения деления; б) .импульсный выход блока 2; в) шина 3 источника входного сигнала; г) вы- ходная шина б делителя; д), ж), з)выходы соответственно первого, второго и третьего разрядов делителя; и), к), л), м) - выходы соответственно первого, второго, третьего, чевертого разрядов устройства 8 записи кода. На диаграммах иллюстрируется три цикла деления на коэффициенты , Кд , Кд и введение коэффициента деления для четвертого цикла Кд .

Упpaвляe Ый делитель частоты работает следующим образом.

В момент перепада входного напряжения, за которым следует отрица- . тельный (несчетный) фронт импульса, сигнал разрешения деления с шины 1 поступает на блок 2 разрешения деления, который вырабатывает потенциал и формирует импульс разрешения деления,. Потенциал разрешения деления открывает вентиль 4, обеспечивая доступ входных импульсов с шины 3 к счетному входу пересчетного блока 5; импульс разрешения деления устанавливает его на О, и, пройдя через элемент 11 ИЛИ и блок 10 ветилей, -вводит прямой код koэффициeнта деления Кд 1 с шины 12 в устройство 8 записи кода. С приходом отрицательного перепада напряжения на вход блока 5 на его шине сквозного заема, выведенной на шину 6, формируется потенциальный перепад, являющийся передним фронтом выходного импульса, поступающий также на второй вход устройства 8 записи кода. При этом происходит перезапись кода Кд 1 из устройства 8 в блок 5, триггеры соответствующих разрядов которого (в расматр 1йаемом случае третьего) регенирируют, ликвидируя потенциальный перепад на шине заема и формируя задний фронт выходного импульса.

Формирователь 9 ио положительному перепаду входного нййряжение (заднему фронту выходного импульса) формирует импульс, проходящий через элемент 11 ИЛИ на вход блока 10 вентилей, записывая в устройство 8 значение кода Кд для следующего цикла (в рассматриваемом примере Кд

После записи в блок 5 кода коэффициента деления (Кд 1) начинается его работа на вычитание. С приходом положит&пьного (переднего) фронта входного импульса, порядковый номер которого равен коэффициенту деления (Кд ), все разряды блока 5 устанавливаются в нулевое состояни а с приходом его заднего фронта на 1я не заема формируемся передний фронт второго выходного импульса и начинае ся второй цикл деления (на Кд , н пример) . Во втором цикле деления все происходит аналогично описанному выше, но выходной импульс формируется после прихода третьего входного импульса. При необходимости ввода коэффициента деления последовательным кодом с шины 7 на счетный вход устройства 8 записи кода подаются импул сы на суммирование по команде, формируемой передним фронтом выходного импульса. Частота вЬода следующего значения прямого параллельного или последовательного кода Кд равна частоте выходного сигнала . При неизменном коэффициенте деления gt -const, где fg частота входного сигнала. Таким образом, в отличие от известных устройств, в управляемом делителе частоты практически отсутст вует временная задержка в появлении выходного сигнала, скорость деления возрастает благодаря вводу следующего коэффициента деления непосредственно в момент завершения предыдущего цикла деления. Кроме того, максимальный коэффициент деления конструкцией не ограничен и превышает Кд прототипа в -1/255 120 раз - 1/2«(где, например, и- 16 - число разря доз двоичного пересчетного блока, ч увеличивая диапазон изменения коэффициента деления, расширяет область применения делителя; при использова нии в пересчетном блоке схем средне

Фш. или большой степени интеграции создйется возможность получить высокое быстродействие при большом количестве разрядов пересчетного блока (при больших Кд); на время порядка периода выходного сигнала уменьшена временная задержка в появлении выходной последовательности импульсов; скорость деления увеличена на суммарное время сброса на нуль устройства записи кода плюс время преобраэован« я прямого кода в обратный. Формула изобретения Управляемой делитель частоты по авт. св. 520713, отличающийся тем, что, с цель повышения быстродействия при одновременном расширении функциональных возможностей, в него введены формирователь импульсов включенный между выходом пересчетного блока и вторым входом элемента ИЛИ, и блок вентилей, включенный между выходом элемента ИЛИ и входами устройства записи кода коэффициента деления, первый дополнительный вход которого подключен к шине ввода последовательного кода коэффициента деления, а второй соединен с выходом пересчетного блока, вход сброса которого подключен ко второму выходу блока разрешения деления, при этом сигнальный вход блока вентилей соединен с шиной ввода прямого паргшлельного кода коэффициента деления. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 520713, кл. Н 03 К 23/00, 100275.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1669079A1 |

| Управляемый делитель частоты | 1978 |

|

SU809578A2 |

| Управляемый делитель частоты | 1982 |

|

SU1046936A1 |

| Управляемый делитель частоты | 1987 |

|

SU1471309A2 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU668094A1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

| Делитель частоты с дробным переменным коэффициентом деления | 1987 |

|

SU1589386A1 |

| Делитель частоты следования импульсов с регулируемой длительностью импульсов | 1987 |

|

SU1444937A1 |

| Устройство для преобразования средней частоты пачки импульсов | 1980 |

|

SU906000A1 |

Авторы

Даты

1980-06-15—Публикация

1978-04-07—Подача