Изобретение относится к вычислительной технике и предназначено для воспроизведения функции одного аргу мента, представленного или числоимпульсным (унитарным) , или пара.плель ным кодом. Известно устройство, содержащее дешифратор, сумматор, блок памяти (БП), умножитель 1 . Однако при увеличении точности воспроизведения функций увеличиваетс емкость БП, что вызьюает определенн трудности при построении на основа этого преобразователя устройства дл воспроизведения многоразрядной функ ции. - , - Наиболее близким по технической сущности к изобретению является устройство, содержащее генератор импульсов, двоичный умножитель, пер вые входы которого соединены с выходами блока задания коэффициентов и счетчик функции 2. Однако устройство имеет низкие функциональные возможности из-за того, что переключение участков аппроксимации организовано по числоимпульсному коду модуля функции /у(х)/ и параллельный код аргумента в преобразователе не вырабатывается, что создает определенные трудности при его настройке и контроле или требует усложнения его схемЫ, Цель изобретения - расширение . функциональных возможностей, для обеспечения работы как с числоимпульсным, так и параллельным кодами аргумента без увеличения объема оборудования. Поставленная цель достигается тем, что в устройство, содержащее генератор импульсов, блок задания коэффициентов, счетчик функции и двоичный умножитель, первая группа входов которого соединена с выходами блока задания коэффициентов, дополнительно введены счетчик участков аппроксимации и блок управления, первый вход которого соединен с выходом генератора импульсов, второй - является входом запуска преобразователя, третий - входом числоимпульсного кода аргумента преобразователя, четвертый - входом признака режима работы преобразователя, пятый вход соединен с первыми выходом двоичного умножителя, шестой - с выходом счетчика участков аппроксимации, седьмой с выходом блока задания коэффициентов/ а первый выход блока управления - с тактовыг-т входом двоичного умножителя, второй - с первыми управляющими входом двоичного умножителя, счетчика участков аппроксимации и счетчика функции, третий -. с вторыми (управляющими входами соответственно двоичного умножителя и счетчика участков аппроксимации, четвертый и пятый - соответственно со вторым и третьим входами счетчика функции, четвертый вход которого соединен 50 вторым выходом двоичного умножит ля, а выходы счетчика функции являются выходами кода функции преобразователя, вторая группа входов дбоичного умножителя является входфми кода младших разрядов аргумент4,выходами старших разрядов которого являются входы счетчика участкфв аппроксимации, входы блока задания коэффициентов соединены с выходами счетчика участков аппроксимации и являются выходами старших разрядов аргумента, выходами младших разрядов которого являются выходы двоичного умножителя, третий выхфд которого соединен с третьим sxoдс{)М счетчика участков аппроксимации Кфоме того, блок управления содерж Т элементы И, ИЛИ, НЕ, 2И-ИЛИ и триггер, причем первый вход блока ут равления соединен с первым входом пфрвого элемента И, второй вход кфторого соединен с выходом триггера а : выход - с первьл л в лходом блока управления, второй вход блока управления соединен с первыми входами второго и третьего элементов И,тре тйй и пятый входы блока управления сфединены с первыми входами соотв тственно четвертого элемента И и первого элемента , четвертый вход блока управления подключен к первому входу пятого элемента И и через первый элемент НЕ - с первым входом второго элемента 2И-ИЛИ и втрыми входами второго и четвертого элементов И и первого элемента 2И-ИЛИ, кроме того, четвертый вход блока управления подключен к третьему входу первого элемента 2И-ИЛИ и вторым входам третьего элемента И и второго элемента 2И-ИЛИ, шестой вход блока управления соединен с четвертым входом первого элемента 2И-ИЛИ и вторым входом пятого элемента И, седьмой вход блока управления соединен с третьим и через втоРОА элемент НЕ - с четвертым входом второго элемента 2И-ИЛИ, выход которого соединен с пятым выходом блока управления, выход первого элемента 2И-ИЛИ соединен со входом триггера, нулевой вход которого соедине с выходом второго элемента И и вторкы выходом блока управления, а единичный - с выходом первого элемента ИЛИ, первый вход которого сое

динен с выходом третьего элемента И, первым входом второго элемента ИЛИ и четвертым выходом блока управления, а второй - с выходом четвертого элемента И, выход пятого элемента И соединен со вторым входом втоt oro элемента ИЛИ, выход которого соединен с третьим выходом блока управления.

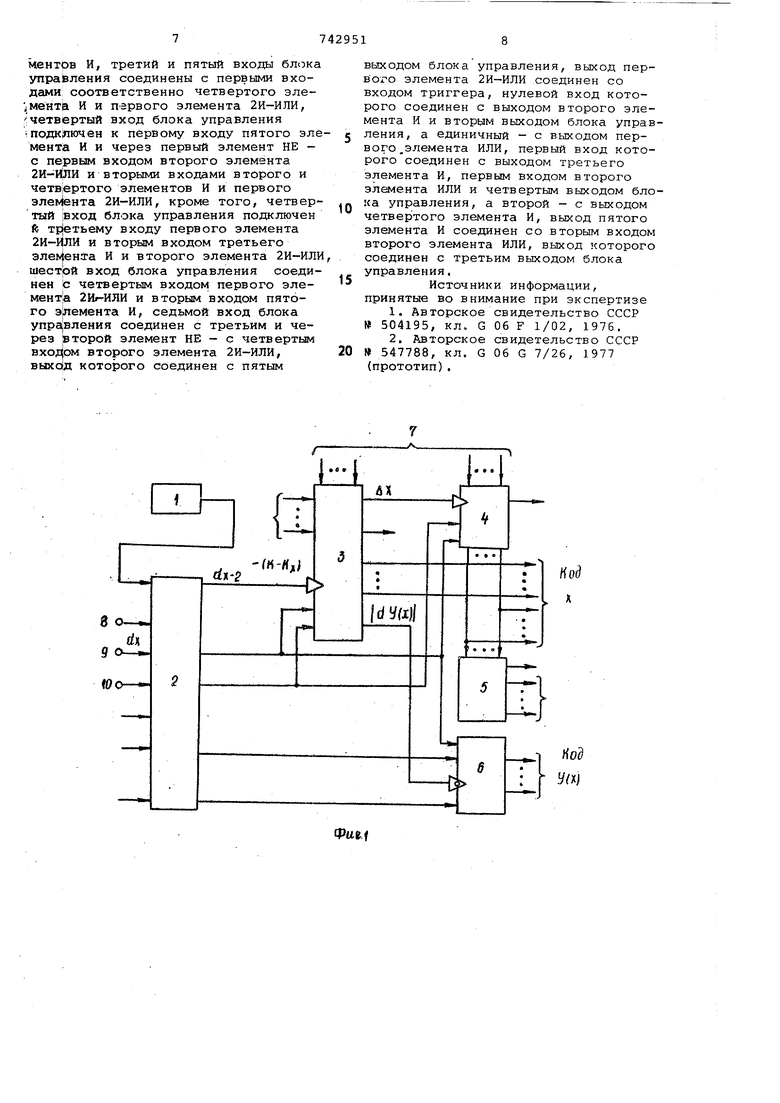

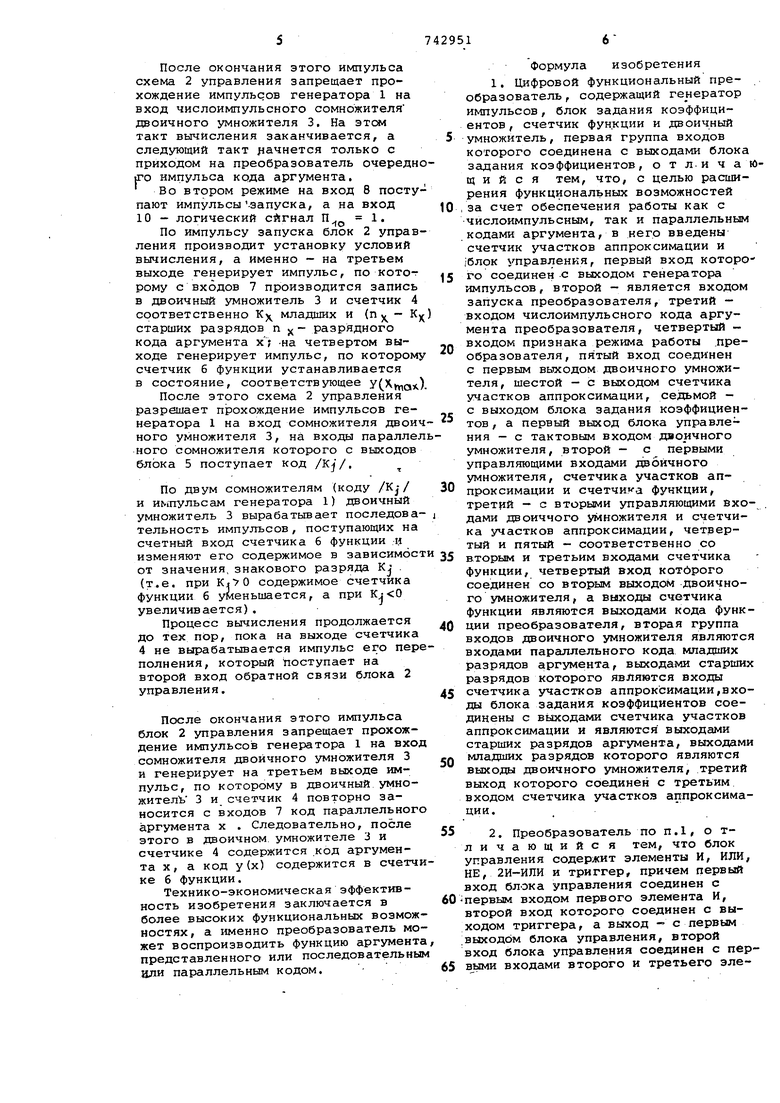

На .фиг. 1 представлена структурная схема предложенного преобразователя; на фиг.2 - схема блока управления.

Схема содержит генератор 1 импульсов, блок 2 управления, к - разрядный двоичный, умножитель 3, счетчик 5 4 участков аппроксимации, блок 5 задания коэффициентов, счетчик 6 функции, входы 7( - разрядного параллельного кода аргумента, вход 8 - запуска, вход 9 - числоимпульсного кода аргумента и вход признака режима 10,элементы 11-15 И, триггер 16, .элементы 17 и 18 2И-ИЛИ, элементы 19-20 ИЛИ, элементы 21,22 НЕ, входы 23-25, выходы 26-28.

Преобразователь работает в режиме вычисления функции по числоимпульсному коду аргумента и в режиме вычисления функции по параллельному коду аргумента.

В первом режиме на вход 8 поступает импульс зпуска Х, , на вход 9 - ммпульс последовательного кода аргумента, а на вход 10 - логический сигнал П.,(-,О.

По импульсу X Q блок 2 управления производит установку начальных условий вычисления, т.е. на втором выходе генерирует импульс, по которому двоичный умножитель 3 и счетчик 4

О

а счетчик

устанавливаются в

функции б - в состояние,соответствующее у (0) .

По каждому импульсу последовательного кода аргумента X в устройстве осуществляется такт вычислений.

Это происходит следующим образом.

По каждому импульсу блок 2 управлния разрешает прохождение импульсов генератора 1 на вход сомножителя двоичного умножителя 3, на входы параллельного сомножителя которого с выаг ходов блока «5 поступает код /Kj/.

По двум сомножителям (коду /Kj/ и импульсам генератора 1) двоичный умножитель 3 на выходе вырабатывает последовательность импульсов, поступакяцих на счетный вход счетчика б функции, и. изменяют его содержимое в зависимости от значения знакового разряда К у (т.е. при K. содержимое счетчика 6 функции увеличивается а при уменьшается). Это продолжается до тех пор, пока на первом выходе двоичного умножителя 3 не вырабатывается импульс переполнения, поступающий на первый вход обратной 04язи блока 2 управления. После окончания этого импульса схема 2 управления запрещает прохождение импульсов генератора 1 на вход числоимпульсного сомножителя двоичного умножителя 3, На этсм такт вычисления заканчивается, а следующий такт 1ачнется только с приходом на преобразователь очеред jro импульса кода аргумента. Во втором режиме на вход 8 посту пают импульсы-запуска, а на вход 10 - логический сигнал П 1. По импульсу запуска блок 2 управ ления производит установку условий вычисления, а именно - на третьем выходе генерирует импульс, по которому с входов 7 производится запись в двоичный умножитель 3 и счетчик 4 соответственно Ку младших и (п, - K старших разрядов п - разрядного кода аргумента х; -на четвертом выходе генерирует импульс, по котором счетчик 6 функции устанавливается в состояние, соответствующее У(ид После этого схема 2 управления разрешает прохождение импульсов генератора 1 на вход сомножителя двои ного умножителя 3, на входеи паралле ного сомножителя которого с выходов блока 5 поступает код /Kj/. По двум сомножителям (коду и импульсам генератора 1) двоичный умножитель 3 вырабатывает последов а тельность импульсов, поступающих на счетный вход счетчика 6 функции и изменяют его содержимое в зависимос от значения,знакового разряда Kj . (т.е. при К.0 содержимое счетчика функции б уменьшается, а при увеличивается). Процесс вычисления продолжается до тех пор, пока на выходе счетчика 4 не вырабатывается импульс его пер полнения, который поступает на второй вход обратной связи блока 2 управления. После окончания этого импульса блок 2 управления запрещает прохождение импульсов генератора 1 на вхо сомножителя двоичного умножителя 3 и генерирует на третьем выходе импульс, по которому в двоичный умножителЪ 3 и счетчик 4 повторно заносится с входов 7 код параллельног аргумента х . Следовательно, после этого в двоичном умножителе 3 и счетчике 4 содержится код аргумента х , а код у(х) содержится в счетч ке б функции. Технико-экономическая эффективность изобретения заключается в более высоких функциональных возмож ностях, а именно преобразователь мо жет воспроизводить функцию аргумент представленного или последовательны или параллельным кодом. Формула изобретения 1. Цифровой функциональный преобразователь , содержащий генератор импульсов, блок задания коэффициентов , счетчик функции и двоичный умножитель, первая группа входов которого соединена с выходами блока задания коэффициентов, о т л.и ч а ющ и и с я тем, что, с целью расширения функциональных возможностей ,за счет обеспечения работы как с числоимпульсным, так и параллельным кодами аргумента, в негр введены счетчик участков аппроксимации и (блок управления, первый вход которого соединен -с выходом генератора импульсов, второй - является входом запуска преобразователя, третий - входом числоимпульсного кода аргумента преобразователя, четвертый входом признака режима работы .преобразователя, пятый вход соединен с первым вьтходом двоичного умножителя, шестой - с выходом счетчика участков аппроксимации, седьмой с выходом блока задания коэффициентов , а первый выход блока управления - с тактовым входом двоичного умножителя, второй - с первыми управляющими входами двоичного умножителя, счетчика участков аппроксимации и счетчика функции, - с вторыми управляющими входами двоичного умножителя и счетчика участков аппроксимации, четвертый и пятый - соответственно со вторым и третьим входами счетчика функции, четвертый вход которого соединен со вторым выходом двоичного умножителя, а выходы счетчика функции являются выходами кода функции преобразователя, вторая группа входов двоичного умножителя являются входами параллельного кода младших разрядов аргумента, выходами старших разрядов которого являются входы счетчика участков аппроксимации,входы блока задания коэффициентов соединены с выходами счетчика участков аппроксимации и являются выходами старших разрядов аргумента, выходами младших разрядов которого являются выходы двоичного умножителя, третий выход которого соединен с третьим входом счетчика участков аппроксимации. 2. Преобразователь по п.1, о тичающийс я тем, что блок правления содержит элементы И, ИЛИ, Е, 2И-ИЛИ и триггер, причем первый ход блока управления соединен с ервым входом первого элемента И, торой вход которого соединен с выодом триггера, а выход - с первым ыходом блока управления, второй ход блока управления соединен с перыми входами второго и третьего элементов И, третий и пятый входы блока управления соединены с первыми входами соответственно четвертого эле;мента И и первого элемента 2И-ИЛИ, четвертый вход блока управления подключен к первому входу пятого эл мента И и через первый элемент НЕ с первым входом второго элемента 2И-ИЛИ и вторыми входами второго и четвертого элементов И и первого элефнта 2И-ИЛИ, кроме того, четвер тый 1вход блока управления подключен fc TFJeTbeMy входу первого элемента 2И-ИЛИ и вторым входом третьего элемента И и второго элемента 2И-ИЛ шестЬй вход блока управления соеди нен ;С четвертым входом первого элеменф 2Иг-ИЛИ и вторым входом пятого э1пемента И, седьмой вход блока упрфления соединен с третьим и через SB торой элемент НЕ - с четвертым BxofipM второго элемента 2И-ИЛИ, выхс|д которого соединен с пятым выходом блока управления, выход первого элемента 2И-ИЛИ соединен со входом триггера, нулевой вход которого соединен с выходом второго элемента И и вторым выходом блока управления, а единичный - с выходом первого .элемента ИЛИ, первый вход которого соединен с выходом третьего элемента И, первым входом второго элемента ИЛИ и четвертым ВЕЖОДОМ блока управления, а второй - с выходом четвертого элемента И, выход пятого элемента И соединен со вторым входом второго элемента ИЛИ, выход которого соединен с третьим выходом блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 504195, кл, G 06 F 1/02, 1976. 2.Авторское свидетельство СССР 547788, кл. G 06 G 7/26, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU928347A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Функциональный преобразователь кода угла и дальности | 1981 |

|

SU1008734A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Цифровой функциональный преобразователь | 1988 |

|

SU1543401A1 |

ы

Н

Г

.„rZl:..J

п

Фиа2

Авторы

Даты

1980-06-25—Публикация

1978-03-01—Подача