ческой единицы преобразователя, а вход второго слагаемого сумматора соединен с выходом инверсного кода формирователя кода, выходы соответствующих старших разрядов второго кодо вого выхода квадратора соединены через блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с адресными входами блока памяти, пр Э1ом выходы разрешения выдачи и выхо старшего знакового разряда блока управления, вход знакового разряда код второй прямоугольной координаты, вто рой кодовый выход квадратора и первый, второй, третий и шестой выходы синхроимпульсов блока синхронизации являются соответственно знаковым, информационным и тактирующими выхода ми преобразователя, причем блок управления содержит три триггера, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемен та 2-2-ЗИ-ЗИЛИ и два элемента 2И, выходы первого триггера, второго триггера, первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответственно первым и вторым выходами равенства кодов, выходом разрешения выдачи и выходом старшего разряда блока управ-, ления., первый вход которого подключе к входу сброса третьего триггера, второй вход которого соединен с первым входом, третьим и седьмым входами первого элемента 2-2-ЗИ-ЗИЛИ, тре тьим входом второго элемента 2-2-ЗИ- ЗИЛИ и первым входом второго элемента 2И, третий вход подключен к входам сброса первого и второго триггеров, четвеотьй вход соединен с четвертым и пятым входами первого элемента 2-2-ЗИ-ЗИЛИ и пятым входом второго элемента 2-2-ЗИ-ЗИЛИ, пятый вход подключен к второму входу первого элемента 2И, шестой вход соединен с вторым входом первого элемента 2.2ЗИ -ЗИЛИ и четвертым входом второго элемента 2-2-ЗИ-ЗИЛИ, седьмой вход подключен к первому и второму входам второго элемента 2-2-ЗИ-ЗИЛИ и первому входу первого элемента 2И, а восьмой и девятый входьг соединены с входами второго элемента ИСКгаОЧАНЩЕЕ ИЛИ, выход которого подключен к второму входу первого элемента ИСКПННАКШЩЕ гИЛИ, первый вход которого соединен с выходом третьего триггера, выход первого элемента 2И соединен с входом установки третьего триггера, выход второго 1 2 триггера подключен к второму входу второго элемента 2И, выход которого соединен с седьмым входом второго элемента 2-2-ЗИ-ЗИЛИ, выход первого триггера подключен к шестым входам первого и второго элементов 2-2-ЗИ-ЗИЛИ, выходы которых соединены со счетными входами первого и второго триггеров соответственно. 2. Преобразователь по п. 1, отличающийся тем, что, блок синхронизации содержит тринадцать элементов 2И, два элемента ЗИ, два триггера, регистр, элемент 3-2И-2ИПИ, элемент 2-2И-2ИЛИ, семь элементов 2Ш1И, элемент ЗИЛИ и элемент 8ИЛИ, причем второй вход шестого элемента 2И, первый вход первого элемента ЗИ, вход сброса первого триггера, первуй вход элемента 3-2И-2ИЛИ и третий вход элемента 2-2И-2ИЛИ являются инверсными, а выходы девятого элемента 2И, восьмого элемента 2И, элемента 3-2И-2ИЛИ, второго элемента ЗИ, пятого элемента 2ИЛИ, второго триггера, шестого элемента 2ИЛИ, элемента 2-2И-2ИЛИ, седьмого элемента 2ИЛИ, пятого элемента 2И, четвертого элемента 2ИПИ, элемента ЗИЛИ являются соответственно с первого по двенадцатый выходами синхроимпульсов блока,первый, второй и третий входы которого подключены к первому входу второго элемента 2И, второму входу второго элемента ЗИ и третьему входу элемента 8ИЛИ соответственно, четвертый вход блокаподключен к четвертому входу элемента 8ИЛИ, пятый вход блока соединен с первыми входами шестого и седьмого и вторым входом двенадцатого элементов 2И, шестой вход блока -соединен с входом записи регистра, входом установки в/орого триггера и первыми входами пятого и шестого элементов 2ИЛИ, седьмой вход блока подключен к пятому входу элемента 3-2И-2ИЛИ и первому входу первого элемента 2ИЛИ, восьмой вход блока соединен с вторым входом первого элемента 2Ш1И и вторым входом первого элемента ЗИ выход первого элемента 2И подключен к второму, входу пятого элемента 2И, выход второго элемента 2И соединен с первыми входами второго элемента 2ИЛИ и третьего элемента 2И, выход которого подключен к седьмому входу элемента

8ИЛИ, шестой вход которого подключен к выходу четвертого элемента 2И, Bbv ход пятого элемента 2И соединен с вторым входом четвертого элемента 2И счетным входом первого триггера и. вторым входом седьмого элемента 2ИЛИ выход шестого элемента 2И соединен с вторыми входами восьмого, одиннад цатого и тринадцатого элементов 2И и третьим входом первого элемента ЗИ, выход седьмого элемента 2И подключен к второму входу третьего и первым вх дам пятого и девятого элементов 2И и второму входу элемента 32И-2ИЛИ, выход восьмого элемента 2И подключен к третьему входу элемента Зй, второй вход которого соединен с вторым вхо дом шестого элемента 2ИЛИ, счетным входом ВТОРОГО триггера и выходом девятого элемента 2И, выход десятого элемента 2И подключен к входу последовательного кода регистра, выход одиннадцатого элемента. 2И соединен с вторым входом пятого элемента 2ИЖ и пятым входом элемента 8ИЛИ, восьмой вход которого соединен с выходом двенадцатого элемента 2И, четвертым входом элемента 2-2И2ИЛИ и вторым входом элемента ЗИЛИ, выход тринадцатого элемента 2И подключен к четвертому входу элемента 3-2И-2ИЛИ и первому входу седьмого элемента 2ИЛИ выход первого элемента ЗИ соединен с первым входом элемента 8ИЛИ, выход первого триггера подключен к второму входу второго элемента 2И и первому входу второго эпемента ЗИ, выход второго триггера соединен с тзторыми входами шестого и седьмого и первым входом восьмого элементов 2И и вторы и третьим входами элемента 2-2И-2ШШ выход первого разряда регистра подключен к первому входу восьмого и вторым входам девятого и десятого элементов 2И, выход второго разряда регистра соединен с входом сброса первого триггера и первыми входами тринадцатого элемента 2И, первого элемента ЗИ и третьего элемента 2ИЛИ второй вход которого соединен с вторым входом четвертого элемента 2ИЛИ, первыми входами четвертого и одиннадцатого элементов 2И и выходом третьего разряда регистра, выход четвертого разряда регистра подключен к первым входам двенадцатого элемента 2И и четвертого элемента2ИЛИ, выход элемента 3-2И-2ИЛИ соединен с третьим входом второго элемента ЗИ и первым входом элемента 2-2И-2Ш1И, выход которого подключен к первому входу элемента ЗИЛИ, выход первого элемента 2Шта соединен с первым входом первого элемента 2И и вторым входом второго . элемента 2Ш1И, выход которого подключен к первому входу элемента 3-2И-21ШИ, третий вход которого соединен с вторым входом первого элемента 2И и выходом третьего элемента 2ИЛИ, выход элемента ВИЛИ подключен к входу сдвига влево регистра разрядные входы которого соединены с входом константы 0001 блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Генератор концентрических окружностей для телевизионного индикатора | 1983 |

|

SU1124373A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Быстродействующий селективный измеритель амплитуды ВЧ-сигнала | 1990 |

|

SU1780029A1 |

| Квадратор | 1981 |

|

SU1010620A1 |

| Устройство для формирования пачек импульсов | 1991 |

|

SU1812617A1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| Устройство для сортировки информации | 1988 |

|

SU1501039A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

1. ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ КООРДИНАТ, содержащий два счетчика, блок памяти, число-импульсный умно- житель, кодовый вход которого сое- динен с выходом блока памяти, от-: лич ающийся тем, что, с целью повьшёния точности, он содержит блок элементов ИСКЛЮЧАЩЕЕ ИЛИ, сумматор, формирователь кода, элемент 2ИЛИ, квадратор, блок управления и блок синхронизации, .первый вход которого подключен к выходу переполнения сумматора, второй и третий входы соединены с выходом переполнения и импульсным выходом формирователя кода, четвертый вход соединен с импульсным выходом квадратора, пятый вход подключен к тактовому входу преобразователя, шестой вход соединен с первым входом блока управления и входом запуска преобразо- вателя, седьмой и восьмой входы подключены соответственно к первому и второму выходам равенства кодов блока управления, вькод разрешения вьг дачи которого соединен с управляющим входом блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и информационным входом квадратора, синхровходы управляющих импульсов которого с первого по шестой соединены соответственно с третьим, четвертым, пятым, шестым, седьмым и восьмым, вьЬсодами синхрр импульсов блока синхронизации, пятый выход синхроимпульсов которогоподт ключен к установочному входу формирователя кодов, шестой выход синхроимпульсов соединен с вторым входом блока управления и управляющими входами формирователя кода и число-импульсного умножителя, седьмой выход синхроимпульсов подключен к третьему входу блока управления и входам за писи счетчиков, девятый выход синхроимпульсов соединен с тактовым входом число-импульсного умножителя и четвертым входом блока управления, (Л десятый выход синхроимпульсов подключен к первому входу элемента 2Ш1И, одиннадцатый выход синхроимпульсов соединен с пятым сходом блока управления, а двенадцатый выход синхроимпульсов подключен к вычитающим входам счетчиков, выход число-импульо сного умножителя соединен с вторым входом элемента 2ИЛИ, выход которого 00 подключен к тактовому входу формировасо ю ю теля кода, выходы переполнения счетчиков подключены соответственно к седьмому и шестому входам блока уп- . равления, восьмой и девятый входы которого соединены соответственно с входами знаковых разрядов первой и второй прямоугольных координат, входы модулей которых подключены к разрядным входам соответствующих счетчиков, первый кодовый выход квадратора соедщен с входом слагаемого формирователя кода и входом первого слагаемого сумматора, вход переноса которого подключен к потенциалу логи-

Изобретение относится к вычислительной технике, предназначено для выполнения операции преобразования прямоугольных координат в полярные координаты и может быть, в частности, использовано при построении специализированного цифрового вычислителя (,СЦВ) и генератора видеоимпульсов окружностей телевизионного устройст на отображения информации (УОИ) ме- теорологической радиолокационной станции (МРЛ).

Цель изобретения - повышение точл ности преобразования в СЦВ двоичных

.кодов прямоугольных координат в ДВО

ичные и двоично-десятичные коды полярных координат за счет повышения точности выполнения операции преобразования координат и выработки кодов полярных координат как в числоимпульсных, так и параллельных двоичных кодах..

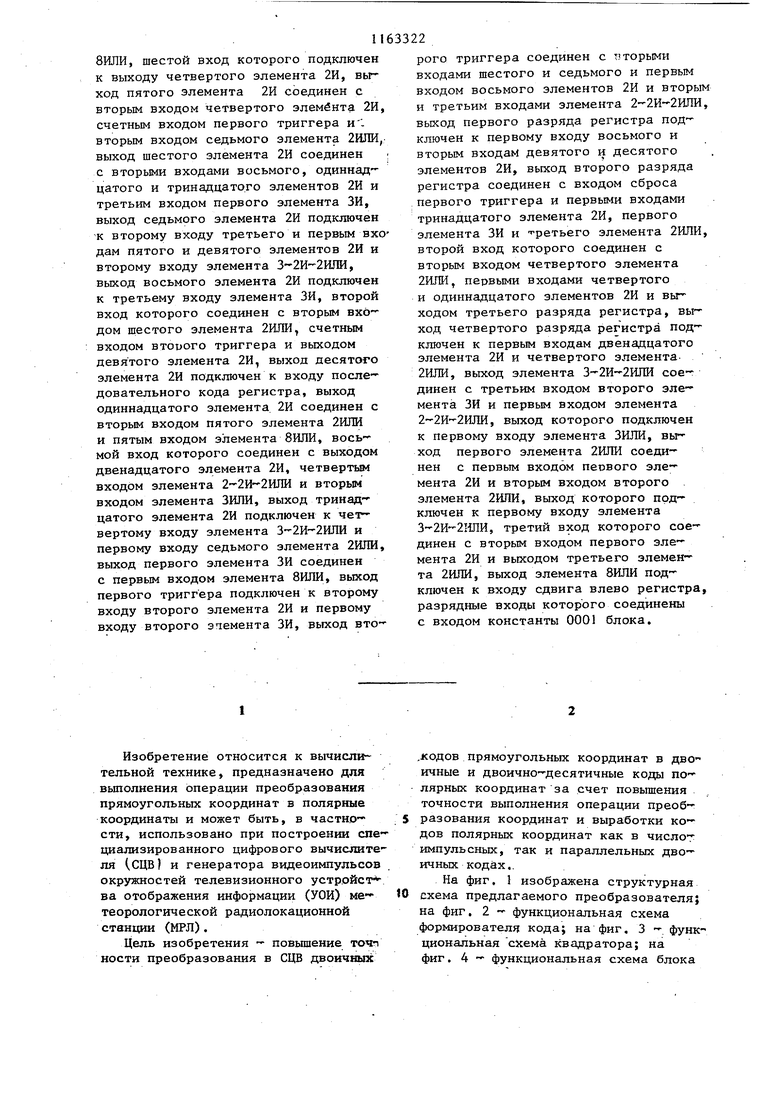

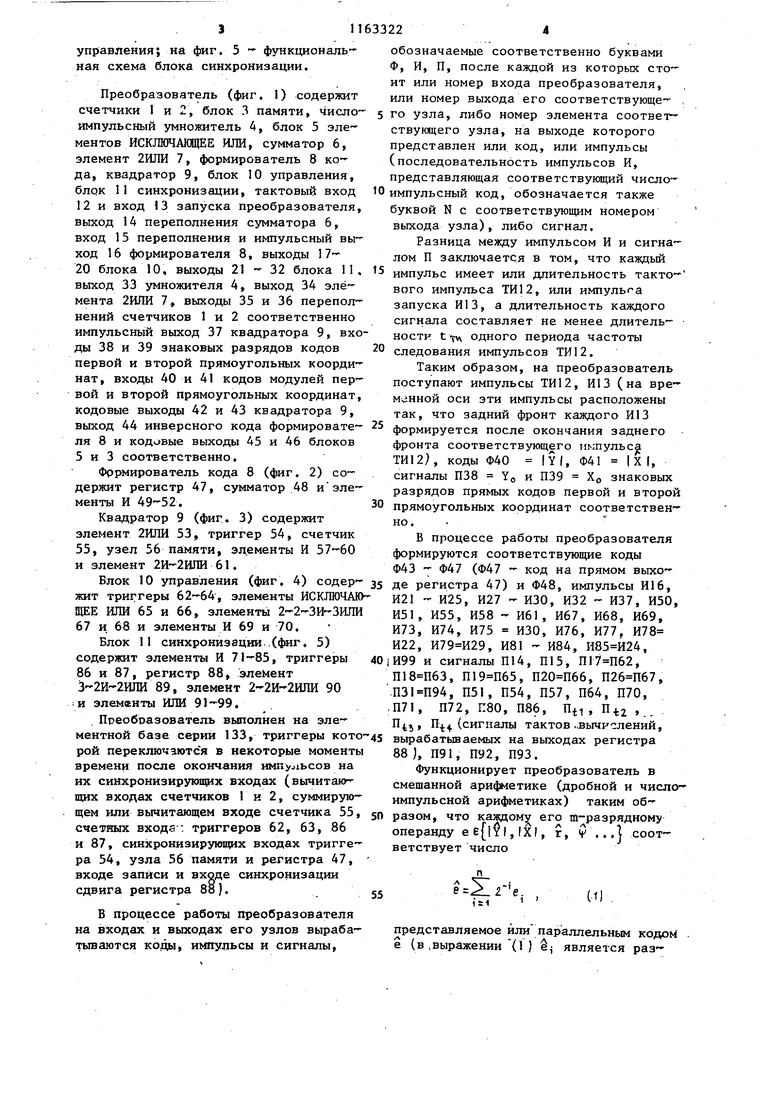

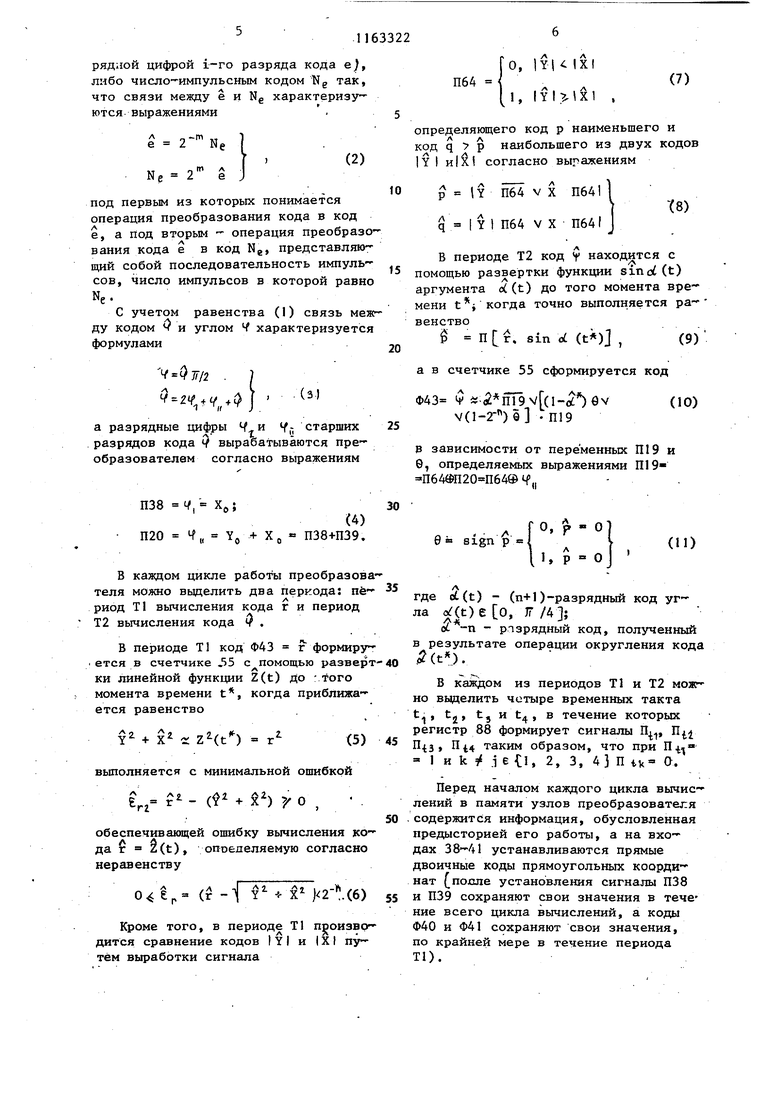

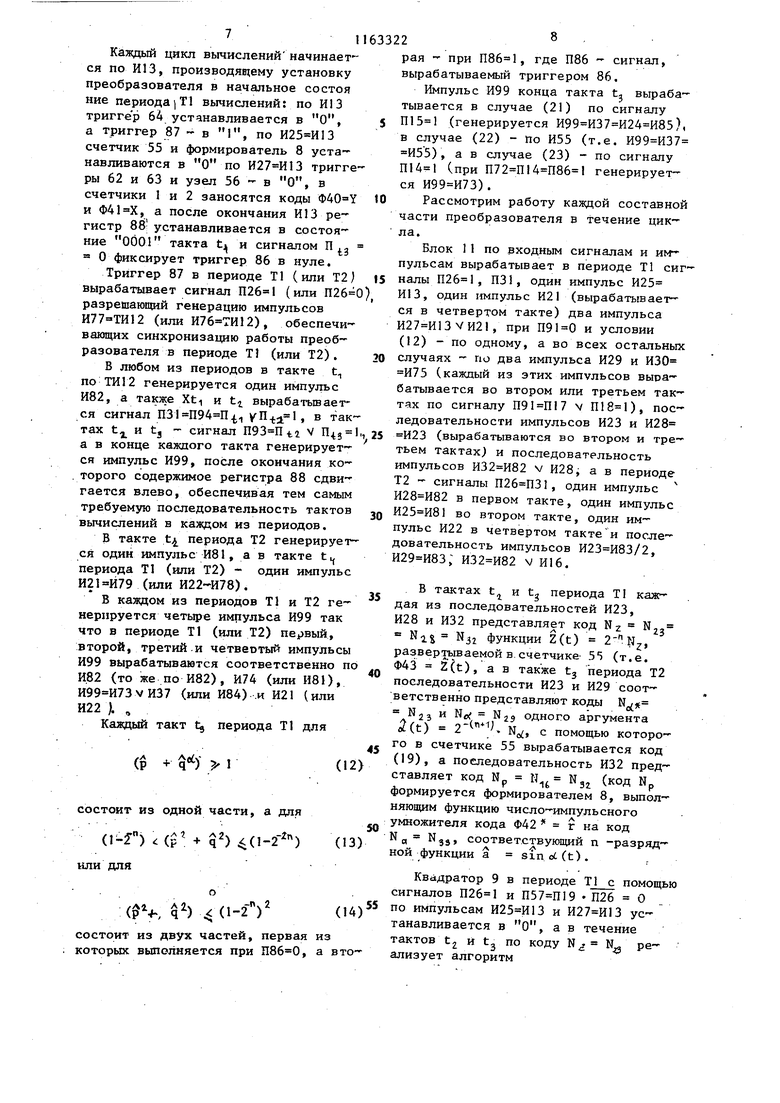

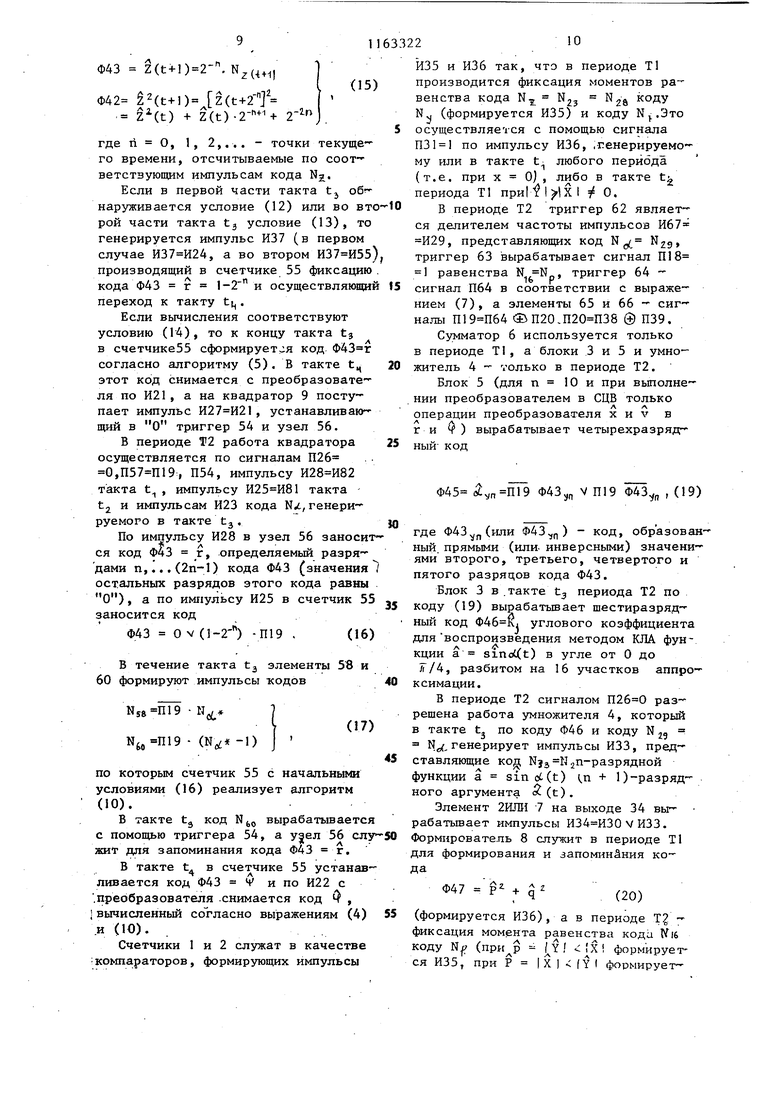

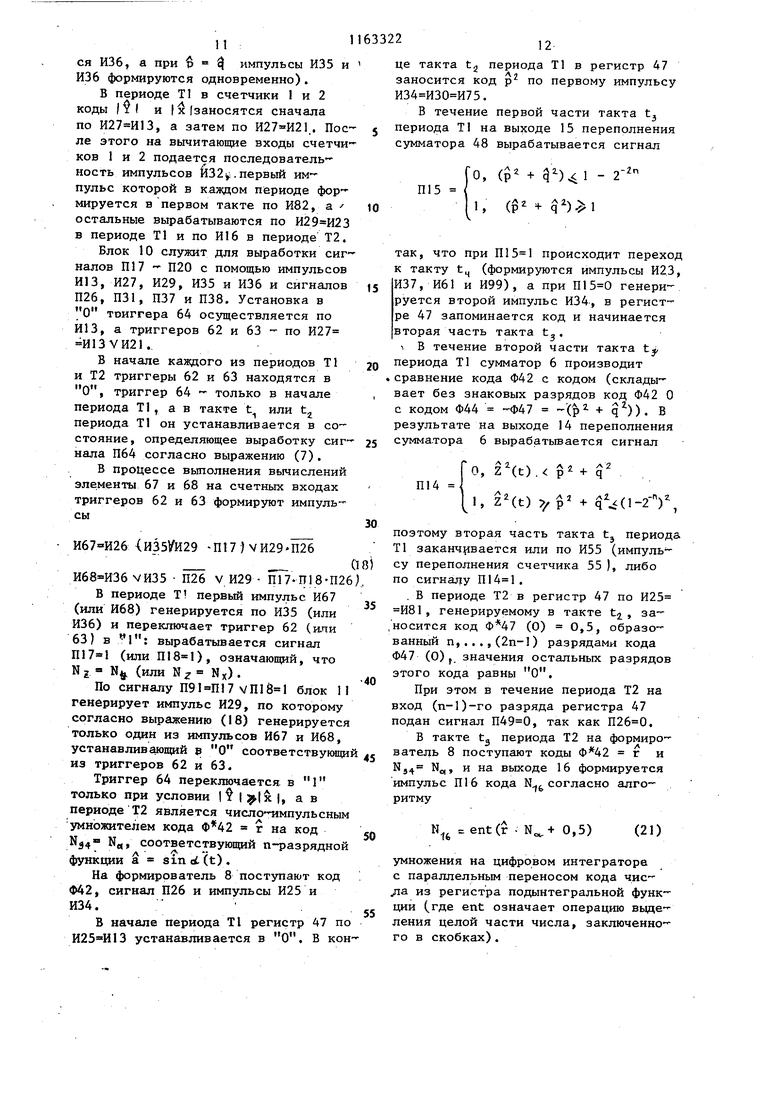

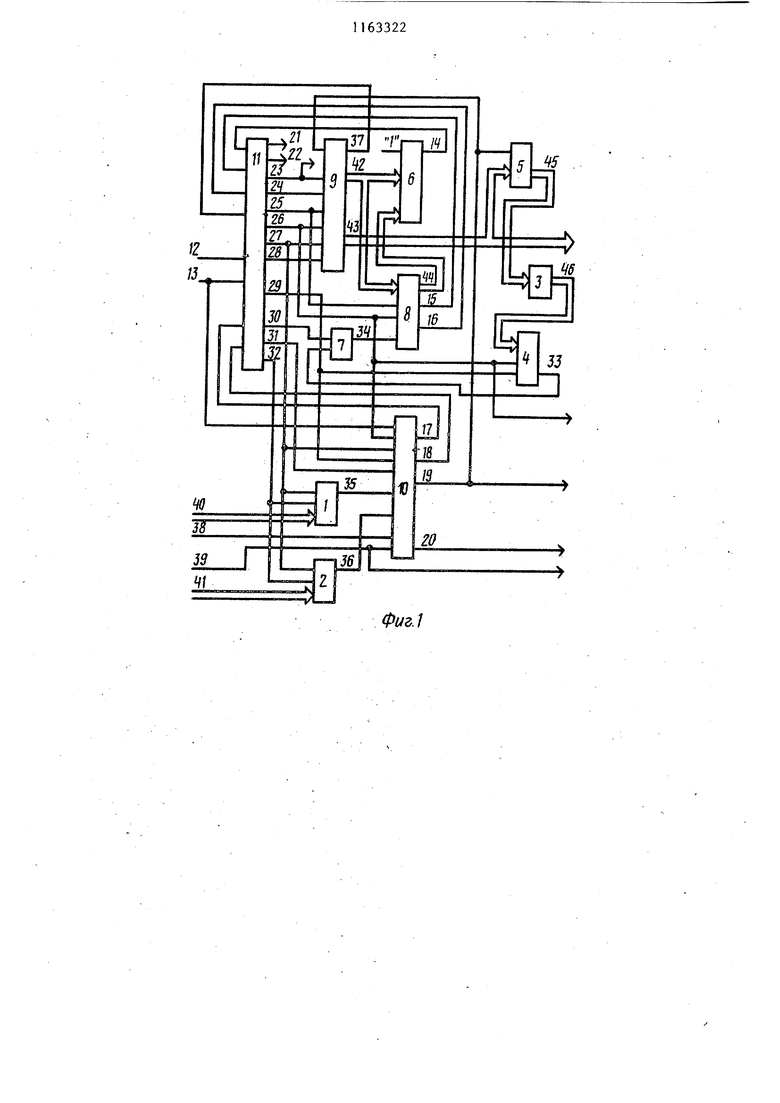

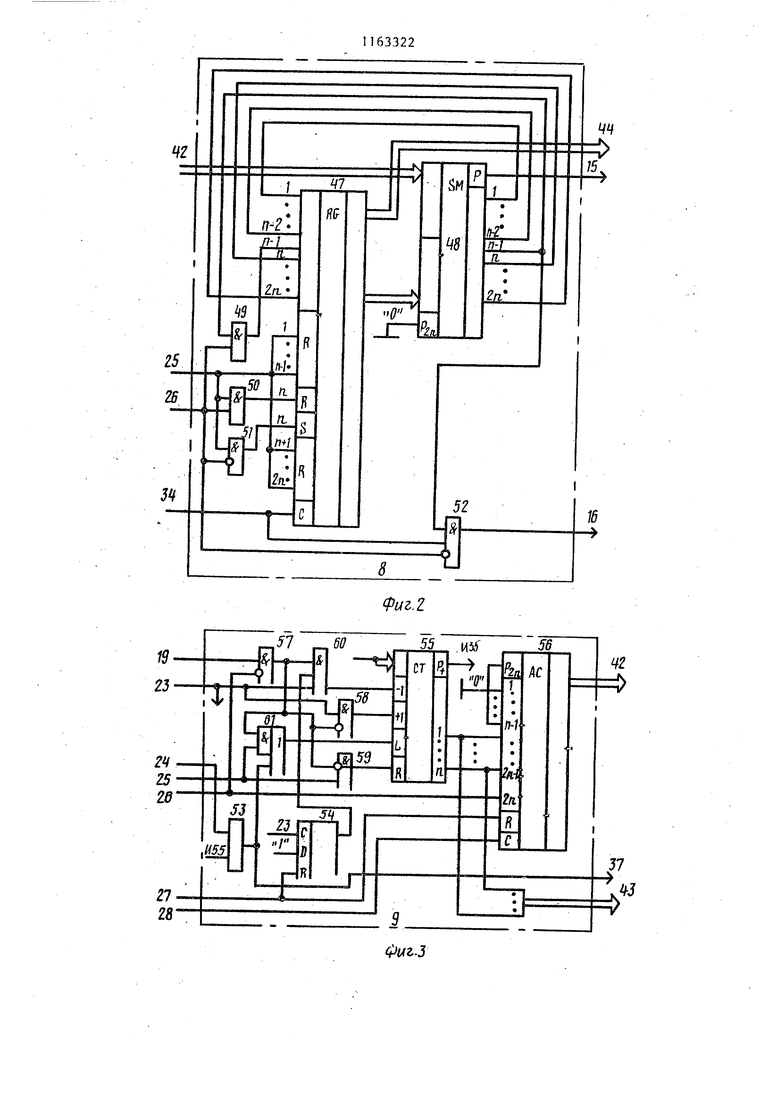

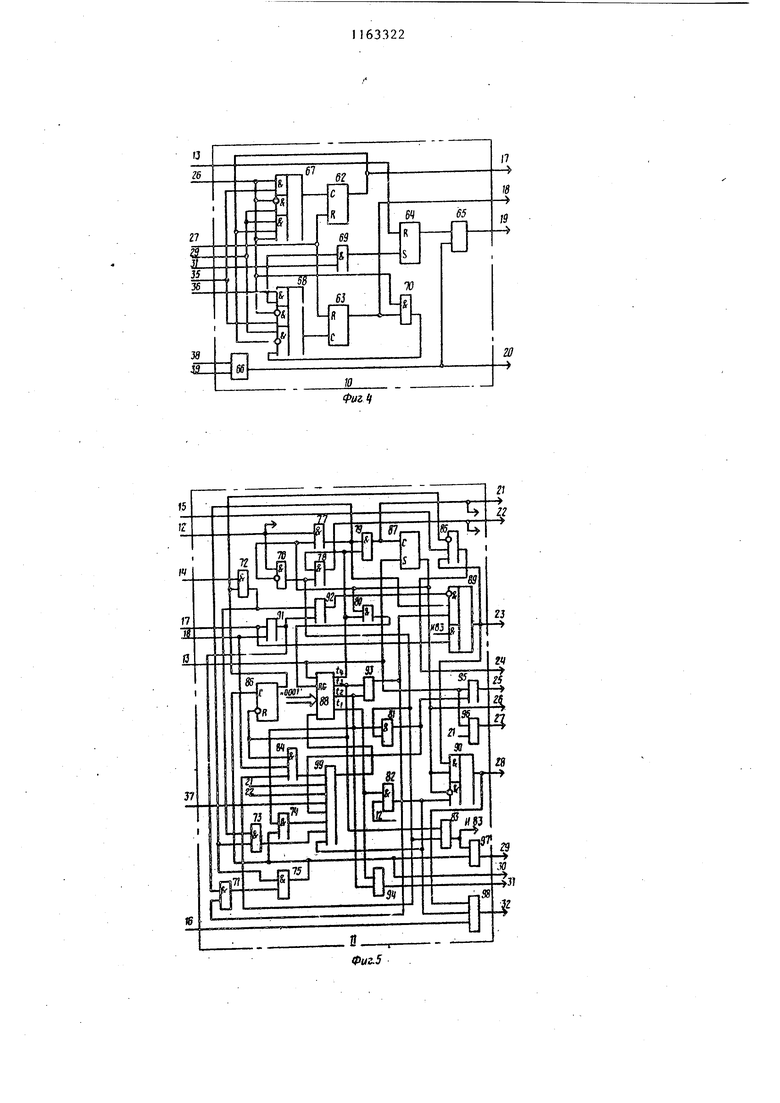

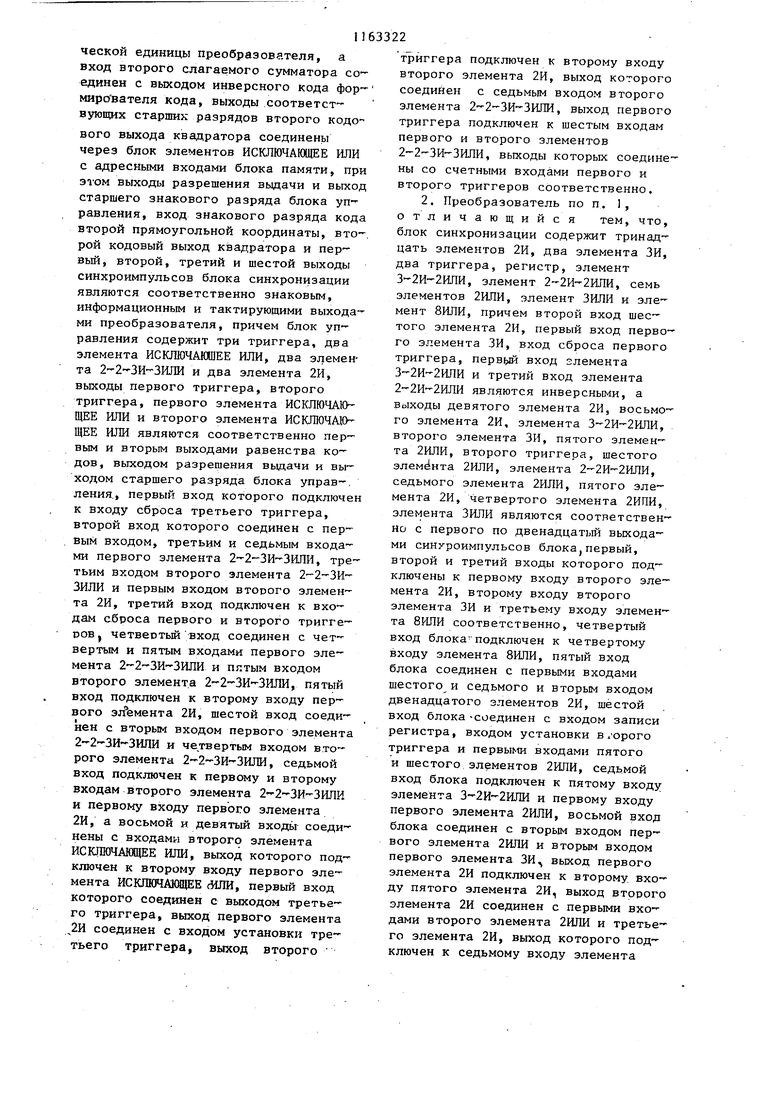

На фиг, 1 изображена структурная схема предлагаемого преобразователя; на фиг. 2 - функциональная схема формировател кода; на фиг. 3 -функциональная схема квадратора; на фиг. 4 - функциональная схема блока 311 управления; на фиг. 5 функциональная схема блока синхронизации. Преобразователь (фиг. 1) содержит счетчики 1 и 2, блок 3 памяти, число-импульсный умножитель 4, блок 5 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматор 6, элемент 2ИЛИ 7, формирователь 8 ко да, квадратор 9, блок 10 управления. блок 11 синхронизации, тактовый вход 12 и вход 13 запуска преобразователя, вьгеод 14 переполнения сумматора 6, вход 15 переполнения и импульсный вы ход 16 формирователя 8, выходы 1 20 блока 10, выходы 21 - 32 блока 11. выход 33 умножителя 4, выход 34 элемента 2ИЛИ 7, выходы 35 и 36 перепол нений счетчиков 1 и 2 соответственно импульсный выход 37 квадратора 9, вхо ды 38 и 39 знаковых разрядов кодов первой и второй прямоугольшх координат, входы 40 и 41 кодов модулей первой и второй прямоугольных координат, кодовые выходы 42 и 43 квадратора 9, выход 44 инверсного кода формирователя 8 и кодовые выходы 45 и 46 блоков 5 и 3 соответственно. Формирователь кода В (фиг. 2) содержит регистр 47, сумматор 48 иэлементы И 49-52. Квадратор 9 (фиг. 3) содержит элемент 2Ш1И 53, триггер 54, счетчик 55, узел 56 памяти, эдементы И 57-60 и элемент 2И-2ИПИ 61. Блок 10 управления (фиг. 4) содержит триггеры , элементы ИСКЛЮЧАЮ ЩЕЕ ИЛИ 65 и 66, элементы 2-2-ЗИ-ЗИЛИ 67 и. 68 и элементы И 69 и 70. Блок 11 синхронизации .(фиг. 5) содержит элементы И 71-85, триггеры 86 и 87, регистр 88, элемент 3-2И-2ИПИ 89, элемент 2-2И-2ШШ 90 и элементы ИЛИ 91 -99. Преобразователь выполнен на элементной базе серии 133, триггеры кото рой переключаются в некоторые моменты времени после окончания HMnyjibcoB на их синхронизирующих входах (вычитающих входах счетчиков I и 2, суммирующем или вычитающем входе счетчика 55, счетных входб : триггеров 62, 63, 86 ,™.г ,,, - А9. fi-. Rfi и 87, синхронизирующих входах триггера 54, узла 56 памяти и регистра 47, входе записи и входе синхронизации сдвига регистра 88). В процессе работы преобразователя на входах и выходах его узлов вырабатываются коды, импульсы и сигналы. 2 обозначаемые соответственно буквами , И, П, после каждой из которых сто т или номер входа преобразователя, ли номер выхода его соответствующео узла, либо номер элемента соответствующего узла, на выходе которого редставлен или код, или импульсы последовательность импульсов И, редставляющая соответствующий число- мпульсный код, обозначается также буквой N с соответствующим номером выхода узла), либо сигнал. Разница между импульсом И и сигна-лом П заключается в том, что каждый импульс имеет или длительность тактового импульса ТИ|2, или импульса запуска И13, а длительность каждого сигнала составляет не менее длитель-- ности t j одного периода частоты следования импульсов ТИ12. Таким образом, на преобразователь поступают импульсы ТИ12, И13 (на временной оси эти импульсы расположены так, что задний фронт каждого И13 формируется после окончания заднего фронта соответствующего I ;пyльca ТИ12), коды Ф40 lYI, Ф41 IX I, сигналы П38 YO и II39 Хо знаковых разрядов прямых кодов первой и второй прямоугольных координат соответствен- но. В процессе работы преобразователя формируются соответствующие коды Ф43 - Ф47 (Ф47 код на прямом выхо- де регистра 47) и Ф48, импульсы И16, и21 - И25, И27 - ИЗО, И32 - И37, И50, И51, И55, И58 - И6, И67, И68, И69, И73, И74, И75 ИЗО, И76, И77, И78 И22, , И81 - И84, , И99 и сигналы П14, П15, , , , , , , П51, П54, П57, П64, П70, П71, П72, П80, П86, П , П., , , (сигналы тактов .вычислений. вырабатываемых на выходах регистра 88), П91, П92, П93. Функционирует преобразователь в смещанной арифметике (дробной и числоимпульсной арифметиках) таким образом, что каждому его л-разрядному операнду ,lXI, г, V ...} соответствует число Iti представляемое или параллельным кодом ё (в.выражении (1 ) ё является разрядной цифрой i-ro разряда кода е), либо число-импульсным кодом Ng так, что связи между ё и Ng характеризуются выражениями ё 2- N. N- т fi р 2 е под первым из которых понимается операция преобразования кода в код ё, а под вторым - операция преобразо вания кода ё в код Ng, представляющий собой последовательность импульсов, число импульсов в которой равно Ne. С учетом равенства (I) связь меж ду кодом ч и углом Ч характеризуется формулами . ) 24;tv,,. J а разрядные цифры f- старших разрядов кода f вырабатываются преобразователем согласно выражениям

П38 Xj,;

П20 f „ Y(j + XQ « П38-1-П39, В каждом цикле работы преобразова теля можно выделить два периода: пё- риод Т1 вычисления кода г и период Т2 вычисления кода . В периоде Т код Ф43 г формируется в счетчике J55 с помощью разверт ки линейной функции Z(t) До г.того момента времени t, когда приближается равенство Х ) г (5) выполняется с минимальной ошибкой ,, г - ( йЪ / о , . обеспечивающей ошибку вычисления кода г Z(t), опоеделяемую согласно нергшенству о«е, ((б) Кроме того, в периоде Т1 производится сравнение кодов IYI и 1X1 путём выработки сигнала

р .л 1 О. Р-0

0 в sign р

(11)

1, Р О, IYKIXI определяющего код р наименьшего и код q р наибольшего из двух кодов IY I и| согласно выражениям lY П64 V X П641 q I Y t П64 V X П641 В периоде Т2 код V находится с помощью развертки функции sinoi(t) аргумента o((t) до того момента времени когда точно выполняется равенство . sin d (t)j , (9) а в счетчике 55 сформируется код Ф43 v(l-, V(l-r)e . П19 в зависимости от переменных П19 и 0, определяемых выражениями П19 П64ФП20 П64Ф tf,, где ot(t) - (п+1)-разрядный код угла o((t) е о, F /4 ; oL п - разрядный код, полученный в результате операции округления кода .(t). В каждом из периодов Т1 и Т2 мозкг но вьвделить четыре временных такта t;j , tj,, t, и Ц, в течение которых регистр 88 формирует сигналы IIi, П rit4 таким образом, что при 1 и k « л е 1, 2, 3, 43 П iv О. Перед началом каждого цикла вычислений в памяти узлов преобразователя содержится информация, обусловленная предысторией его работы, а на входах 38-41 устанавливаются прямые двоичные коды прямоугольных координат (пojaлe установления сигналы П38 и П39 сохраняют свои значения в течение всего цикла вычислений, а коды Ф40 и Ф41 сохраняют свои значения, по крайней мере в течение периода ТО. Каждый цикл вычисленийначинает ся по И13, производящему установку преобразователя в начальное состоя ние периода)Т1 вычислений: по И13 триггер 64 устанавливается в О, а триггер 87 - в 1, по счетчик 55 и формирователь 8 уста навливаются в О по тригге ры 62 и 63 и узел 56 - в О, в счетчики 1 и 2 заносятся коды и , а после окончания И13 регистр 88; устанавливается в состоя ние 000 такта Ц и сигналом П О фиксирует триггер 86 в нуле, Триггер 87 в периоде Т1 (или Т2) вырабатывает сигнал (или П26 разрешающий генерацию импульсов И77-ТИ12 (или ), обеспечивающих синхронизацию работы преоб разователя в периоде И (или Т2). В любом из периодов в такте Ц по ТИ12 генерируется один импульс И82, а также Xti и t вырабатьшает ся сигнал уП.. , в так тах tg и tj - сигнал V в конце каждого такта генерируется импульс И99, после окончания которого содержимое регистра 88 сдвигается влево, обеспечивая тем самым требуемую последовательность тактов вычислений в каждом из периодов. В такте t периода Т2 генерирует ся один импульс И81, а в такте t периода Т1 (или Т2) - один импульс (или И22-И78). В каждом из периодов Т| и Т2 генерируется четыре импульса И99 так что в периоде Т1 (или Т2) первый, второй, третий.и четвеотый импульсы И99 вырабатываются соответственно п И82 (то же по И82), И74 (или И81), И99 И73УИ37 (или И84) .и И21 (или И22 J. , Каждый такт tj периода Т1 для (Р + q) J состоит из одной части, а для (1-Г) .( + q(l-2-) или для (V. )(1-2) состоит из двух частей, первая из которых выполняется при , а вт П / рая При , где 1186 - сигнал, вырабатываемый триггером 86. Импульс И99 конца такта t вырабатывается в случае (21) по сигналу (генерируется ), в случае (22) - по И55 (т.е. И55), а в случае (23) - по сигналу (при генерируется ). Рассмотрим работу каждой составной части преобразователя в течение цикла. Блок 11 по входным сигналам и импульсам вырабатывает в периоде Т1 сигналы , П31, один импульс И25 И13, один импульс И2I (вырабатывается в четвертом такте) два импульса H27 H13VH21, при и условии (12) - по одному, а во всех остальных случаях - по два импульса И29 и И30 И75 (каждый из этих ИМПУЛЬСОВ вырабатывается во втором или третьем тактах по сигналу v ), последовательности импульсов И23 и И28 И23 (вырабатываются во втором и третьем тактах) и последовательность импульсов v И28, а в периоде Т2 - сигналы , один импульс в первом такте, один импульс во втором такте, один импульс И22 в четвертом тактеи последовательность импульсов И23 И83/2, V И16, В тактах t и t периода Т1 каждая из последовательностей И23, И28 и И32 представляет код Нг N. iis N32 функции Z(t) , развертываемой в.счетчике- 55 (т.е. Ф43 2(t), а в также tj периода Т2 последовательности И23 и И29 соответственно представляют коды Nj)( N23 и Ncf N23 одного аргумента ot(t) 2 . Ыд, с помощью которого в счетчике 55 вырабатывается код С) последовательность И32 предN, (код N, ставляет код Np N формируется формирователем 8, выполняющим функцию число-импульсного умножителя кода Ф42 г на код я ° зз соответствующий п -разрядной функции а sinot(t). Квадратор 9 в периоде TJс помощью сигналов и П26 О по импульсам и устанавливается в О, а в течение тактов t и tj по коду N N реализует алгоритм Ф43 Z(t + l)2-. N(,, Ф42 2(t+i) z(t+2-f Z(t) + Z(t) 2- где , 1, 2,... - точки текуще го времени, отсчитываемые по соот ветстзующим импульсам кода N. Если в первой части такта tj об наруживается условие (12) или во вт рой части такта tj условие (13), то генерируется импульс И37 (в первом случае , а во втором производящий в счетчике 55 фиксацию кода Ф43 г 1-2 и осуществляющи переход к такту ti,. Если вычисления соответствуют условию (14), то к концу такта tj в счетчике55 сформируется код согласно алгоритму (5). В такте t этот код снимается с преобразовате ля по И21, а на квадратор 9 поступает импульс , устанавливаю щий в О триггер 54 и узел 56. В периоде Т2 работа квадратора осуществляется по сигналам П26 0,, П54, импульсу такта t , импульсу такта t и импульсам И23 кода N, генерируемого в такте tj , По импульсу И28 в узел 56 заноси ся код Ф43 ,г, определяемый разрядами п,...(2п-1) кода ФАЗ (значения остальных разрядов этого кода равны О), а по импульсу И25 в счетчик 55 заносится код Ф43 О V (1-2-) -П19 . (16 В течение такта t элементы 58 и 60 формируют импульсы кодов - Ы ,П19 - () по которым счетчик 55 с начальными условиями (16) реализует алгоритм (10). В такте tj код Nj вырабатывается с помощью триггера 54, а 56 слу жит для запоминания кода Ф43 г. В такте t в счетчике 55 устан ливается код Ф43 V и по И22 с .преобразователя .снимается код Q , i вычисленный согласно выражениям (4) и (10). Счетчики 1 и 2 служат в качестве KONma.paTOpoB, формирующих импульсы И35 и ИЗб так, что в периоде Т1 производится фиксация моментов равенства кода N N23 2& °ДУ Ny (формируется И35) и коду К.Это осуществляется с помощью сигнала по импульсу И36, .генерируемому или в такте t любого периода (т.е. при X 0), либо в такте t периода Т1 npHl I IXl 0. В периоде Т2 триггер 62 является делителем частоты импульсов И67 И29, представляющих код НдС N29, триггер 63 вырабатывает сигнал П18 1 равенства N N , триггер 64 сигнал П64 в соответствии с выражением (7), а элементы 65 и 66 - сигналы ®П20, @) П39. Сумматор 6 используется только в периоде ТI, а блоки 3 и 5 и умножитель 4 - только в периоде Т2. Блок 5 (для п 10 и при выполнении преобразователем в СЦВ только операции преобразователя х и v в л л Г И Ч) вырабатывает четырехразря;г ный код П19 Ф43,,„ V П19 Ф43,,„ , (19) Ф45 oi. где Ф43.,(или Ф43,,.,) - код, образованный. прямыми (или. инверсными) значениями второго, третьего, четвертого и пятого разрядов кода Ф43. Блок 3 в .такте t периода Т2 по коду (19) вырабатывает шестиразрядный код углового коэффициента для воспроизведения методом КЛА функции а sinoG(t) в угле от О до F/4, разбитом на 16 участков аппро- ксимации. В периоде Т2 сигналом разрешена работа умножителя 4, который в такте t по коду Ф46 и коду N j, N, генерирует импульсы ИЗЗ, представляющие ко Ызэ и п-разрядной функции а sin (t) t,n + 1)-разрядного аргумента о (t) . Элемент 2ИЛИ 7 на выходе 34 вырабатывает импульсы И34 ИЗОМИЗЗ. Формирователь 8 служит в периоде Т1 для формирования и запоминания кода + Ф47 р (формируется И36), а в периоде Т фиксация момента равенства кода Ni6 коду N ( - li I :|Х формируется ИЗЗ, при Р IX 1 (Y( формируется И36, а при импульсы И35 и И36 формируются одновременно). В периоде Т1 в счетчики 1 и 2 коды IYI и |х {заносятся сначала по , а затем по .. После этого на вычитающие входы счетчи ков 1 и 2 подается последователь ность импульсов Й32.первый им пульс которой в казкдом периоде фор мируется в первом такте по И82, а остальные вырабатываются по в периоде Т1 и по И16 в периоде Т2. Блок 10 служит для выработки сиг налов П17 II20 с помощью импульсов И13, И27, И29, И35 и И36 и сигналов П26, П31, П37 и П38. Установка в О тоиггера 64 осуществляется по И13, а триггеров 62 к 63 - по И27 И13УИ21. В начале каждого из периодов Т1 и Т2 триггеры 62 и 63 находятся в О, триггер 64 только в начале периода Т1 , а в такте t или t периода Т1 он устанавливается в состояние, определяющее выработку сиг нала 1164 согласно выражению (7) . В процессе вьлолнения вычислений элементы 67 и 68 на счетных входах триггеров 62 и 63 формируют импульсы И35УИ29 -П17 ) VH29n26 VH35 П26 V И29 - П17-Г118-П2 В периоде Т первый импульс И67 (или И68) генерируется по И35 (или И36) и переключает триггер 62 (или 63) в вырабатывается сигнал (или ), означающий, что NZ N (или Ne NX). По сигналу блок П генерирует импульс И29, по которому согласно выражению (18) генерируется только один из импульсов И67 и И68, устанавливающий э О соответствующи из триггеров 62 и 63. Триггер 64 переключается в 1 только при условии it , а в периоде Т2 является число-импульсным умножителем кода г на код N54 Кд, соответствующий п-разрядной функции а sin оС (t) . На формирователь 8 поступают код Ф42, сигнал П26 и импульсы И25 и И34. В начале периода Т1 регистр 47 п устанавливается в О. В ко 2 периода Т1 в регистр 47 це такта t л по первому импульсу заносится код р . В течение первой части такта tj периода Т1 на выходе 15 переполнения сумматора 48 вырабатывается сигнал а )41 - 2 О, (р (Р q)l 1, так, что при происходит переход к такту t (формируются импульсы И23, И37, И61 и И99), а при генерируется второй импульс И34, в регистре 47 запоминается код и начинается вторая часть такта t. 1 В течение второй части такта t периода Т1 сумматор 6 производит сравнение кода Ф42 с кодом (складывает без знаковых разрядов код Ф42 О с кодом Ф44 -Ф47 -(р + Q )). В результате на выходе 14 переполнения сумматора 6 вырабатьгоается сигнал О, Z4t). р I, Z(t) /$ q(l-2-) поэтому вторая часть такта tj периода Tl заканчивается или по И55 (импульсу переполнения счетчика 55 ), либо по сигналу . В периоде Т2 в регистр 47 по И25 И81, генерируемому в такте t, заносится код (О) 0,5, образованный п,...,(2п-1) разрядами кода Ф47 (О),, значения остальных разрядов этого кода равны О, При этом в течение периода Т2 на вход (n-l)-ro разряда регистра 47 подан сигнал , так как . В такте tj периода Т2 на формирователь 8 поступают коды г и Нз N(,, и на выходе 16 формируется импульс П16 кода N согласно алгоритмуent(r - 0,5) умножения на цифровом интеграторе с параллельным переносом кода чис- jia из регистра подынтегральной функции (где ent означает операцию вьщеления целой части числа, заключенного в скобках).

Фиг.Ч

фыг.З

.f f

26

-n-I

27

L IL 35 36

17

W

19

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-23—Публикация

1983-03-04—Подача