( ) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ОРЕОБРАЗОСАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1978 |

|

SU742951A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Число-импульсный функциональный преобразователь | 1979 |

|

SU860071A1 |

| Функциональный преобразователь | 1983 |

|

SU1107131A1 |

| Число-импульсный функциональный преобразователь | 1980 |

|

SU924715A2 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Цифровой аппроксиматор | 1981 |

|

SU1010619A1 |

| Цифровой функциональный преобразователь | 1988 |

|

SU1543401A1 |

| Устройство для вычисления полиномов | 1978 |

|

SU792263A1 |

| Число-импульсный функциональный преобразователь | 1985 |

|

SU1256021A2 |

1

Изобретение относится к вычислительной технике, в частности к устройствам обработки дискретной информации, в которых количество импульсов имеет функциональную зависимость от иа(меняемой величины и может быть использовано для воспроизведения по числоимп.ульсному коду аргумента широкого класса функцией, например немонотонных функций, скорость изменения которых (в квантах) может превышать скорость изменения аргумента.

Известен цифровой функциональный преобразователь для воспроизведения функциональных зависимостей по число-, импульсному коду аргумента i .

Однако в этом преобразователе не предусмотрена возможность формирования немонотонных функций.

Наиболее близким по технической сущности к предлагаемому является преобразователь, содержащий вход числоимпульсного кода аргумента,программный блок, образованный регистром

сдвига и блоком памяти, и блок умножения, образованный двоичным умножителем и формирователем сигнала конца участка аппроксимации, причем тактовый вход соединен с входом аргумента, а остальные входы подключены к выходам блока памяти, вход обратной связи которого подключен к выходу сигнала конца участка аппроксимации блока умножения, у которого дво10ичный умножитель образован счетчиком, первой группой элементов И и элементом ИЛИ, а формирователь сигнала конца участка аппроксимации образован второй группой элементов -И.

15

Работа этого преобразователя основана на методе кусочно-линейной аппроксимации. Угловой коэффициент и длина каждого участка аппроксимации задаются блоку умножения программным

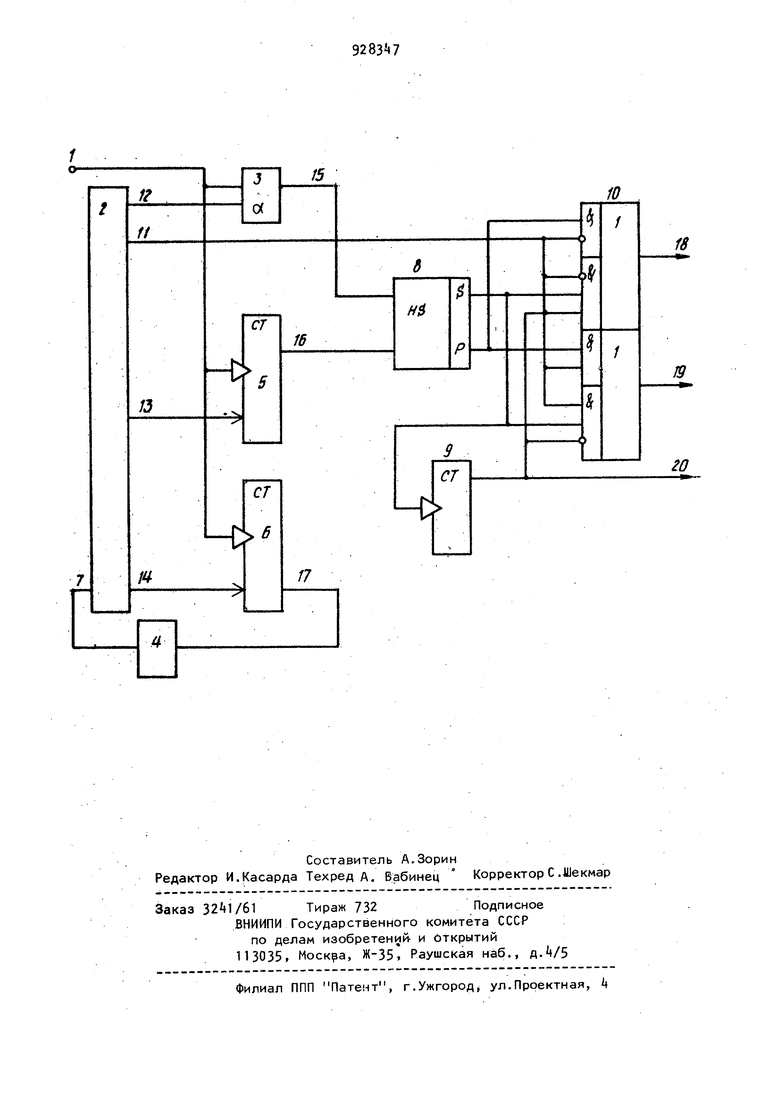

блоком так, что блок- умножения по входному числоимпульсному коду аргумента вырабатывает числоимпульсный код (возрастаю-дей, либо убывающей) 392 функции и сигнал конца участка аппроксимации 2 . . Недостатком такого преобразователя является то, что вследствие недостаточно полного использования возможностей программного блока, преобразователь не может воспроизводить какнемонотонные функции, так и функции, скорость изменения которых (в квантах) могла бы превышать скорость изменения аргумента, т.е. по каждому кванту аргумента выходная функция преобразователя может изменяться не более, мем на один квант. Цель изобретения - расширение класса воспроизводимых функций за счет дополнительной возможности вычисления немонотонных функций и функций, скорость изменения которых превышает скорость изменения аргумента. Поставленная цель достигается тем что в цифровой функциональный преобразователь, содержащий,двоичный умножитель, счетчик, счетчик участков и блок памяти, вход аргумента устройства соединен с входами двоичного умножителя и счетчика, управляющие входы которых соединены соответственно с выходами первой и второй групп блока памяти, вход которого через счетчик участков соединен с выходом счетчика, введены сумматор по модулю два триггер, дешифратор и элемент И, причем вход аргумента устройства соединен с первым входом элемента И, второй вход которого подключен к первому выходу блока памяти, второй выход которого соединен с .первым входом дешифратора, второй вход которого под. ключен к первому выходу сумматора по модулю два и третьему входу дешифратора, четвертый вход которого соединен со вторым выходом сумматора по модулю два, пятым входом дешифратора и.входом триггера, выход которого является выходом младшего разряда значения функции и соединен с шестым и седьмым входами дешифратора, восьмой, девятый и десятый входы которого соединены со вторым выходом блока памяти, первый и второй выходы дешифратора являются выходами числоимпульсного кода положительного и отрицательного соответртвенно приращения функции. На чертеже представлена блок-схема преобразователя. Преобразователь содержит вход 1 аргумента преобразователя, блок 2 памяти, элемент 3 И, счетчик участков, двоичный умножитель 5, счетчик 6, вход 7 блока памяти, сумматор 8 по модулю два, триггер 9. дешифратор 10, выходы 11-1 блока памяти, выход 15 элемента 3 И, выход 16 двоичного /множителя, выход 17 счетчика, выходы 18-20 преобразователя. Работа преобразователя основана на принципах кусочно-линейной аппроксимации и осуществляется следующим образом. Для обеспечения работы преобразователя на его вход Т подается числоимпульсный код аргумента х {ЧИК х) представляющий собой последовательность импульсов, каждый импульс которой имеет вес dx (т.е. означает изменение аргумента х на dx). Преобразователь по ЧИК х вырабатывает на выходах 18-20 цифровые сигналы функции у таким образом, что на выходе 20 вырабатывается младший разряд двоичного кода .у с весом dy,a на выходе 18 (выходе 19) числоимпульсный код положительного (отрицательного) приращения функции у, представляющий собой последовательность импульсов, каждый импульс которой имеет вес 2dy (вес на выходе 19 - 2 dy Перед поступлением на вход 1 преобразователя очередного импульса ЧИК X (т.е. очередного приращения dx) блок 2 памяти, двоичный умножитель 5 счетчик 6 и триггер 9 .находятся в некоторых состояниях, обусловленных предысторией работы преобразователя так, что блок 2 выдает прямой двоичный код углового коэффициента (на выходе 11 - знаковый разряд ki, на выходе 12 - старший разряд kj, а на выходах 13 - остальные разряды kj) j-ro участка аппроксимации и двоичный прямой код длины AXvtV последующего (j+1)-ro участка аппроксимации (код лхjv вырабатывается на выходах 1А блока 2) а в счетчике 6 содержится полный код х или код некоторой длины оставшейся части j-ro участка аппроксимации. С выхода 11 знаковый разряд kb поступает на дешифратор 10, .с выхода 12 старший разряд kj поступает на вход элемента И 3. с выходов 13 остальные разряды k поступают на разрядные входы двоичного умножителя 5 ас выходов 14 код u.xJ4 поступает на разрядные входы счётчика 6. На другие входы дешифратора 10 подаются сигналы с выходов (выхода переполнения и выхода суммы) сумматора 8 по модулю два и с выхода 20 триггера 9. счетный вход которого подключен к выходу суммы сумматора 8 по модулю два. При-этом по каждому импульсу приращения dx аргумента х содержимое счетчика 6 уменьшается на один квант {т.,е. на dx). а в зависимости от Зна чения ky и содержимого двоичногб умножителя 5 возможны три случая выработки приращения функции у: приращение функции у не вырабатывается; вырабатывается импульс приращения dy на выходе 15 элемента И 3 и вырабатывается импульс приращения dу на вы ходе 16 двоичного умножителя 5; выра батывается импульс приращения dy на выходе 15 элемента, И 3, или на выходе 16 двоичного умножителя 5. Импульсы приращений функции ус выхода 15 элемента И 3 и с выхода 16 двоичного умножителя 5 поступают на входы сумматора 8 по модулю два. Поэтому в первом случае преобразователь на выход ничего не вырабаты вает, во втором случае, в зависимоети от знакового разряда kj), вырабаты вается либо на выходе 18 импульс положительного пр 1ращения- 2dy, либо на выходе 19 импульс отрицательного приращения -2dy, а в третьем случае блоки 8-10 работают как одноразрядный реверсивный счетчик, формирующий в. зависимости от знакового разряда kl и состояния триггера 9 либо на выходе 18 импульс положительного при ращения 2 dy, либо на выходе 19 имлульс отрицательного приращения -2d функции у.. Такой процесс воспроизведения функции у на J-OM участке продолжаётся до тех пор, пока счетчик 6 не формирует на выходе 17 импульс переполнения, т.е. импульс конца участка аппроксимации, состояние счетчика k изменяется на единицу и на входе 7 блока 2 появляется новый адрес, по которому в счетчик 6 заносится код AxL. В следующий момент блок 2 вырабатывает код k. и код . и начинается процесс воспроизведения функции у на участке (J+1). 76 Таким образом, предлагаемый пре образователь может воспроизводить как .немонотонные функции, так и функции, скорость изменения которых в квантах может превышать скорость изменения аргумента. Формула изобретения Цифровой функциональный преобразователь, содержащий двоичный умножитель, счетчик, счетчик участков и блок памяти, вход аргумента устройства соединен с входами двоичного умножителя и счетчика, управляющие входы которых соединены соответственно с выходами первой и второй групп блог ка памяти, вход которого через счетчик участков соединен с выходом счетчика, отличающийся тем, ЧТО), с целью расширения класса воспроизврдимых функций за счет дополнительной возможности вычисления немонотонных функций и функций, .скорость изменения котор(ых превышает скорость изменения аргумента, в него введены сумматор по модулю два, три1- гер, дешифратор и элемент И, причем вход аргумента устройства соединен с первым входом элемента И, второй вход которого подключен к первому выходу блока памяти, второй выход которого соединен с первым входом дешифратора , второй вход которого подключен к первому выходу сумматора по модулю два и третьему входу дешифратора, четвертый вход которого соединен со вторым выходом сумматора по модулю два, пятым входом дешифратора и входом триггера, выход которого является выходом младше.го разряда значения функции и соединен.с шестым и седьмым входами дешифратора, восьмой девятый и десятый входы которого соединены со вторым выходом блока памяти, первый и второй выходы дешифратора являются выходами числоимпульсного кода положительного и отрицательного соответственно приращения функции. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 15798, кл, Н 03 К 13/00, 197. 2,Авторское свидетельство СССР N 697989, кл, G Об F 1/02, 1979

Авторы

Даты

1982-05-15—Публикация

1980-02-20—Подача