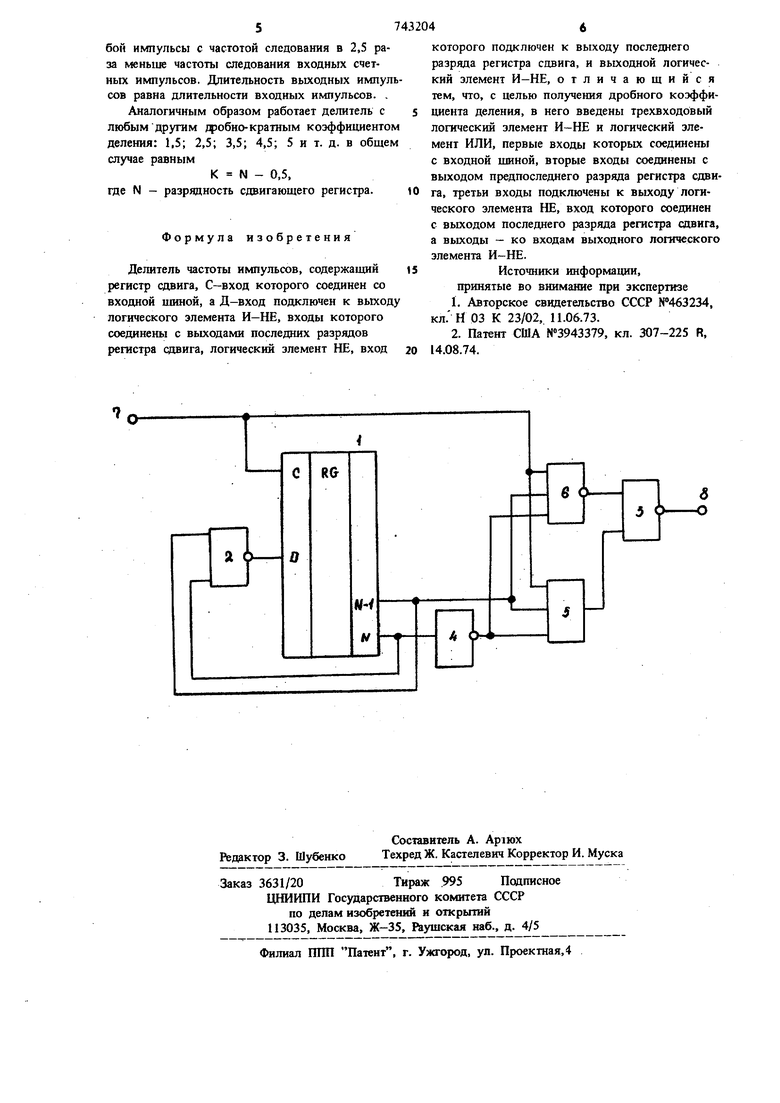

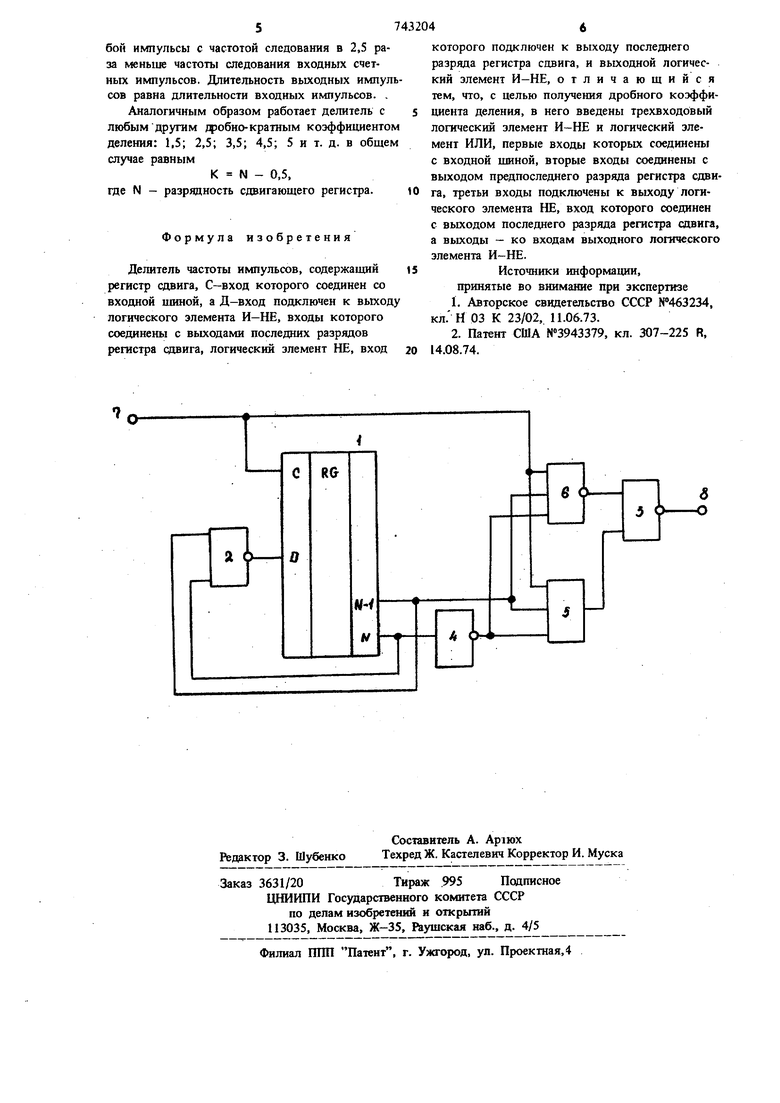

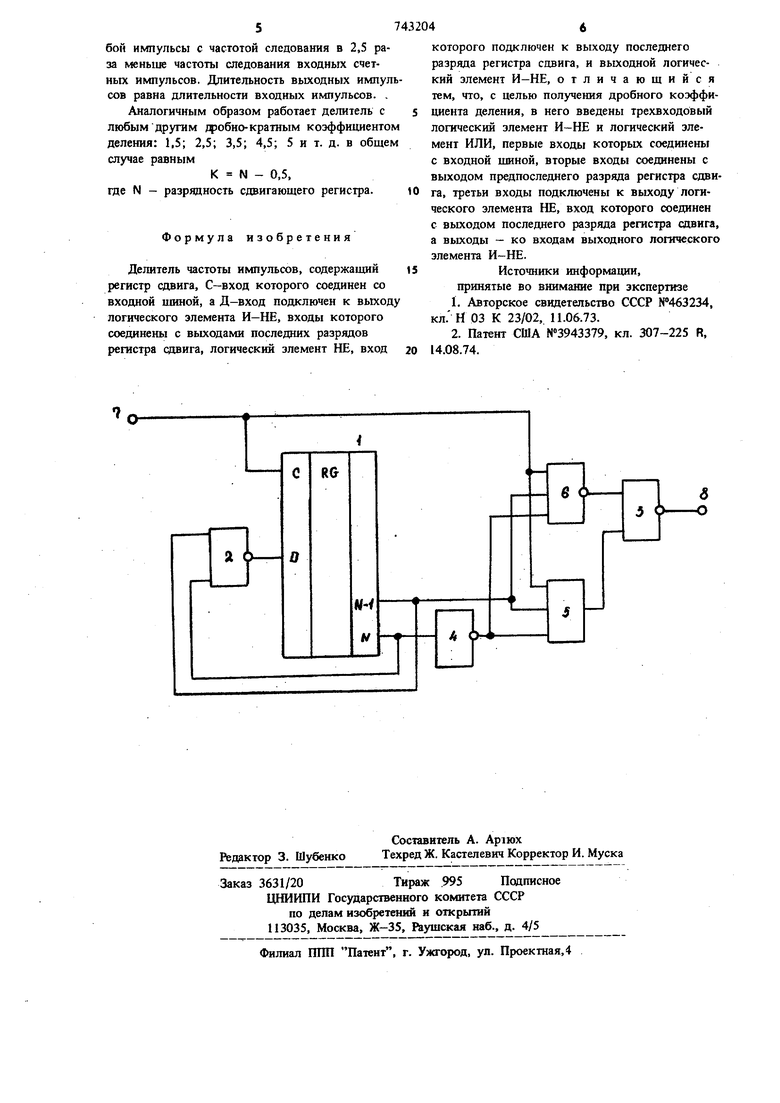

Изобретение относится к импульсной технике. Известен делитель частоты импульсов, содер жаи(ий регистр сдвига, триггер цикла, пусковое устройство, источник входной частоты, управляющий триггер, вход которого подключен к выходу ячейки регистра сдвига, и логические эпекюнты И, соединенные с входами регистра сдвига 11. Недостатком данного делителя является относительная сложность. Наиболее близким но технической сущности к предлагаемому является делитель частоты импульсов, содержащий регистр сдвига. С-в ход которого соединен со входной шиной, а Д-вход подключен к выходу логического элемента И-НЕ, входы которого соединены с выходами последних разрядов регистра сдвига, логический злемент НЕ, вход которого подклю чен к выходу последнего разряда регистра ,и выходной лог тескийэлемштИ-НБ 2 Одюко даниый делитель не обеспечивает получения дробного козффициента деления. Цель изобретения - получение дробного козффициента деления. Поставленная цель достигается тем, что в делитель частоты импульсов, содержащий регистр сдвига. С-вход которого соединен со входной шиной, а Д-вход подключен к выходу логического злемента И-НЕ, входы которого соединены с выходами последних разрядов регистра сдвига, логический злемент НЕ, вход которого подключен к выходу последнего разряда регистра сдвига, и выходной логический злемент И-НЕ, введены трехвходовый злемент И-НЕ и логический злемент ИЛИ, первые входы которых соединены с входной шиной, вто- рые входы соединены с выходом предпоследнего разряда регистра сдвига, третьи входы подключены к выходу логического злемента И-НЕ. На чертеже приведена структурная злектрическая схема описьшаемого делителя частоты. Делитель. частоты содержит регистр 1 сдвига, логический злемент И-НЕ 2, выходной логический злемент И-НЕ 3, логический злемент НЕ 4, логический злемент ИЛИ 5, трехвходовый логический злемент И-НЕ 6. Входные сигналы

3743

поданы на входную шину 7, выходной сигнал снимается с выхода 8.

Принцип работы делителя заключается в следующем.

Рассмотрим работу устройства на примере делителя частоты следования импульсов с коэффициентом деления 2,5. Для получения такого коэффициента деления регистр 1 должен содержать три разряда, т. е. N 3. В этом случае выходы регистра (N-1) и N соответствуют

выходам второго и третьего разрядов регистра 1.

За исходное сосфяние устройств принимается наличие уровней логического О на всех выходах регистра 1 сдвига. При этом уровнями О, поступающими с N-1 и W выходов регистра, на выходе логического элемента И-НЕ 2 поддерживается логическая 1, которая поступает на Д-вход регистра 1. На выходе логического элемента И-НЕ 6 присутствует логическая 1, поддерживаемая уровнем О, поступающим с выхода N-1 регистра 1. На выходе логического элемента ИЛИ 5 - логическая 1, поддерживаемая уровнем 1 с выхода логического элемента НЕ 4, на входе которого присутствует уровень О, поступающий с выхода N регистра 1. Логические 1 с выходов логических элементов 5 и 6.поступают на входы логического элемента И-НЕ 3, при этом на его выходе присутствует . уровень логического О, который подается на выход 8.

После окончания первого счетного импульса на входной щине 7 происходит сдвиг информации в регистре 1 на один разряд, на выходе первого разряда появляется уровень I и в регистре устанавливается код 100. Других изменений сигналов на выходах элементов при этом не происходит.

После окончания второго счетного импульса происходит очередной сдвиг информации в регистре 1 на один разряд и в нем устанавливается код 110. Других изменений сигналов на выходах элементов не происходит.

Третий счетный импульс, поступивший на входную ошну 7, открывает логический элемент И-НЕ 6, так как на двух других его входах присутствуют уровни логических 1, поступающих с N-1 выхода регистра 1 и с выхода логического элемента НЕ 4. На выхс№(е логического элемента И-НЕ 6 появляется логический О, который, поступая иа вход логического элемента И-НЕ 3, вызьтает появление на его выходе уровня 1, далее поступающего на выход 8,

После окончания третьего счетного импульса прсжсходит очередной сдвиг информации в регистре 1 на один разряд и в нем устанавливается код 111. Логические 1 с N-1 и N выходов регистра, поступая на оба входа логического элемента И-НЕ 2, вызывают появление на его выходе уровня логического О, далее поступающего на Д-вход регистра 1. Кроме того, 1 с N выхода регистра поступает на вход логического элемента НЕ, на выходе которого появляется уровень О, который, воэдействуя на один из входов логического элемента И-НЕ 6, запирает его и на его выходе появляется логическая 1, а так как на выходе логического элемента ИЛИ 5 также присутствует логическая 1, поддерживаемая уровнем 1 с N-1 выхода регистра, то на выходе логического элемента И-НЕ 3 появляется уровень логического О, далее поступающий на вь1ход 8.

После окончания четвертого счетного импульса происходит сдвиг информации в регистре 1 на один разряд, на выходе первого разряда появляется уровень О и в регистре устанавливается код 011. Других изменений сигналов на выходах элементов не происходит.

После окончания пятого счетного импульса происходит очередной сдвиг информации в регистре 1 на один разряд и в нем устанавливается код 001. Логический О с выхода N-1 регистра, постзшая на один из входов логического элемента И-НЕ 2, вызьтает появление на его выходе уровня логической 1, далее поступающего на информационный вход регнстра 1. На всех трех входах логического элемента ИЛИ 5 присутствуют уровни логического О, поступающие с N-1 выхода регистра 1, с выхода логического элемента НЕ 4 и с входной щины 7, поэтому на выходе логического элемента ИЛИ 5 устанавливается уровень логического О, который,поступая на вход логического элемента И-ЙЕ 3, выйьтает появление на его выходе логической 1, далее поступающей на выход 8.

Шестой счетный импульс, поступивший на входную щину 7, проходит логический элемент ИЛИ 5 и, поступая на один из входов логического элемента И-НЕ 3, вызьюает появление на его выходе уровня логического О, так как на другом его входе прнсутствует уровень 1, поступающий с логического элемента И-НЕ 6.

После окончания щестого счетного импульса в очередной раз происходит сдвиг информации в регистре 1 на один разряд и в нем устанавливается код 100.

После окончания каждого из последующих счетных импульсов происходит сдвиг информаци в регистре 1 на один разряд, при этом регистр последовательно принимает пять устойчивых состояний, соответствующих кодам: ПО, 111, 011, 001, 100, затем цикл работы устройства вновь повторяется. При этом на выходе 8 формируется выходной сигнал, представляющий со5бон импульсы с частотой следования в 2,5 раза меньше частоты следования входных счетных нилпульсов. Длительность выходных нмпул сов равна длительности входных импульсов. Аналогичным образом работает делнтель с любым другим щзобно-кратным коэффициентом деления: 1.5; 2.5; 3,5; 4,5; 5 и т. д. в общем случае равным К N - 0,5. где N - разрядность сдвигающего регистра. Формула изобретения Делитель частоты импульсов, содержащий регистр сдвига, С-вход которого соединен со входной шиной, а Д-вход подключен к выходу логического элемента И-НЕ. входы которого соединены с выходами последних разрядов регистра сдвига, логический элемент НЕ. вход 4 которого подключен к выходу последнего разряда регистра сдвига, и выходной логический элемент И-НЕ. отличающийся тем. что, с целью получения дробного коэффициента деления, в него введены трехвходовый логический элемент И-НЕ и логический элемент ИЛИ. первые входы которых соединены с входной цшной, вторые входы соединены с выходом предпоследнего разряда регистра сдвига, третьи входы подключены к выходу логического элемента НЕ. вход которого соединен с выходом последнего разряда регистра сдвига, а выходы - ко входам выходного логического элемента И-НЕ. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР N 463234 кл. И 03 К 23/02. 11.06.73. 2.Патент США N«3943379. кл. 307-225 R. 14.08.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1709515A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1988 |

|

SU1837323A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1709269A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Демодулятор фазоманипулированных сигналов | 1987 |

|

SU1443200A1 |

| Устройство для деления частоты пов-ТОРЕНия иМпульСОВ | 1979 |

|

SU817891A1 |

| Делитель частоты следования импульсов | 1983 |

|

SU1128390A1 |

| Устройство индикации пеленга | 1983 |

|

SU1167555A1 |

| Делитель частоты следования импульсов с нечетным коэффициентом деления | 1977 |

|

SU708515A1 |

71

W-f ti

гти

Авторы

Даты

1980-06-25—Публикация

1977-04-12—Подача