Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств цифровых вычислительных машин. Известны комбинационные, параллельные суммирующие устройства, состоящие из одноразрядных сумматоров со сквозным последовательным переносом. Они позволяют выполнять только арифметическое сложение двух чисел Для выполнения, например, сложения по модулю 2 требуются дополнительные схемы поразрядного сравнения. Это приводит к непроизводительным затратам оборудования 1. Известен также сумматор с управля емым переносом, в котором для выполнения арифметического сложения и сложения по модулю 2 на одном и том же оборудовании вводится схема управ ления переносом. Это достигается введением в каждый четный (нечетный) разряд сумматора узла инвертирования одного из слагаемых управляемого сиг нала обратного значения переноса из предыдущего разряда, а также коллекторным объединением выхода инвертора управляемого сигнала гашение переноса с выходом прямого зна 1ения переноса 2.. Недостатком такого сумматора является сложность управления схемой переноса, неоправданная избыточность оборудования и, хотя и незначительное, увеличение времениобщего суммирования за счет прохождения одного из слагаемых через соответствующий узел инвертированая на одноразрядный сумматор. Кроме того, коллекторное объединение, применяемое в указанном устройстве, приемлемо не для всякой элементной базы. Наиболее близким к предлагаемому является комбинационный сумматор, содержащий в кгикдом разряде два элемента И-ИЛИ-НЕ, на выходе одного из которых формируется значение суммы данного разряда, а на выходе второго - значение переноса в последующий разряд. К входс1М первого элемента И-ИЛИ-НЕ для получения значения разрядной суммы подключены шины прямых и инверсньйх значений соответствующих разрядов слагаемых и переноса из предыдущего разряда. Для получения значения переноса в последующий разряд КО входам второго элемента И-ИЛИ-НЕ в каждом нечетном разряде йумматорй подключены шины инверсных значений соответствующих разрядов слагаемых и переноса из предыдущего рааряда, а в каждом четном разряде сумматора - шины прямых значений соответствующих разрядов слагаемых и переноса из предыдущего разряда 3.

Недостаток такого сумматора - его недостаточные функциональные возможности, позволяющие производить лишв операцию .арифметического сложения и не позволяющие осуществлять поразрядное суммирование (сложение по модулю 2).

Цель изобретения - устранение указанного недостатка, т.е. расширение функциональных возможностей сумматора.. ... , , - .

Для достижения поставленной цели в комбинационном .сумматоре, содержаздем в каждом разряде узел формирования суммы и узел формирования перено.са, причем узел формирования переноса содержит три элемента И и элемент ИЛИ-НЕ, три входа которого подключены к выходам элементов И, а выход - , к выходу узла формирования переноса данного разряда,выход которого является выходом переноса из данного разряда сумматора, входы узла формирования суммы каждого разряда соединены со входами значений слагаемых данного разряда и выходом переноса ИЗ предыдущего разрйда сумматьра-, первыйи второй входы первого элемента И узла формирования переноса каждого разряда соединены с первым и вторым входами узла формирования переноса, входы второго элемента Hi- с первым и третьим входами данного узла, а входы третьего элемента И со вторым и третьим входами данного узла, при этом первый, второй и третий входы узла формирования переноса каждого нечетного разряда сумматора подключены к шинам инверсных значений соответствующих разрядов первого и BTOpofo слагаемых и выходу переноса из предыдущего разряда соответственно, а первый, второй и третий входы . узла формирования переноса.каждого четного разряда сумматора подключены к шинам прямых значений соответствующих разрядов первого и второго AafaeNfcjx и вахЬду переноса иэ преыдущего разряда соответственно, етвертый вход элемента ИЛИ-НЕ узла формирования переноса каждого нечетного разряда сумматсгра соединен с иной запрета переноса, а третий вход nejpBoro элемента И узла формироания переноса каждого четного разяда сумматора - с шиной инверсии апрета переноса.

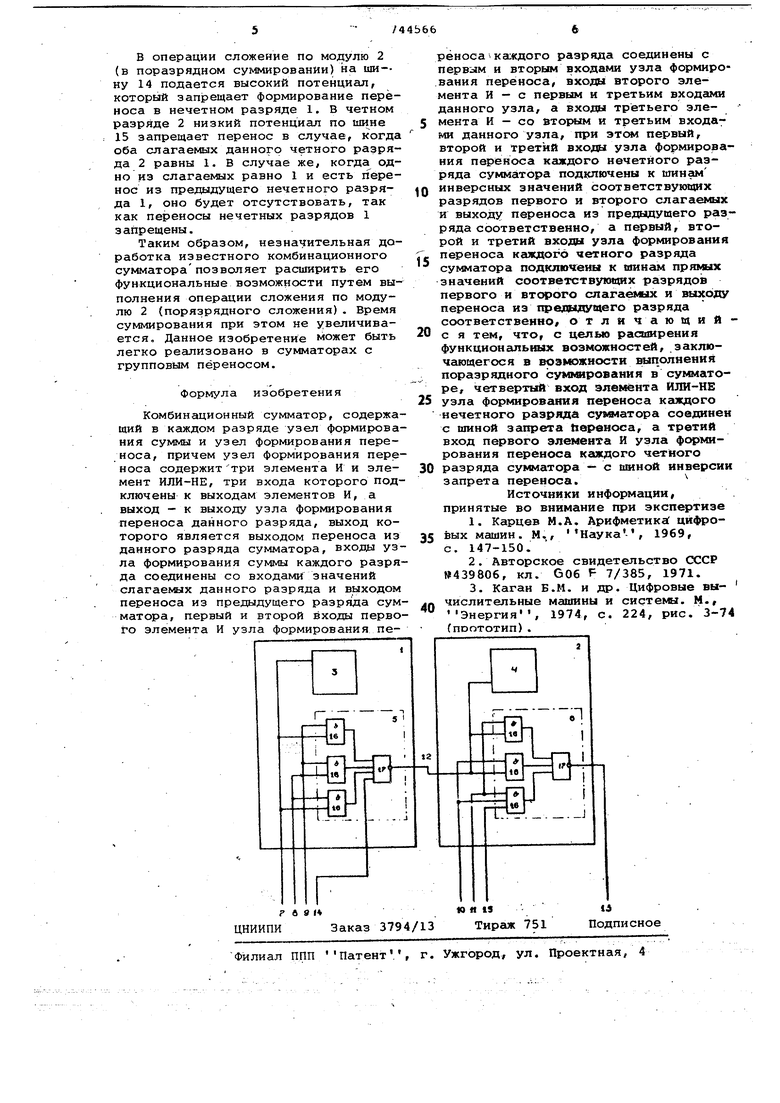

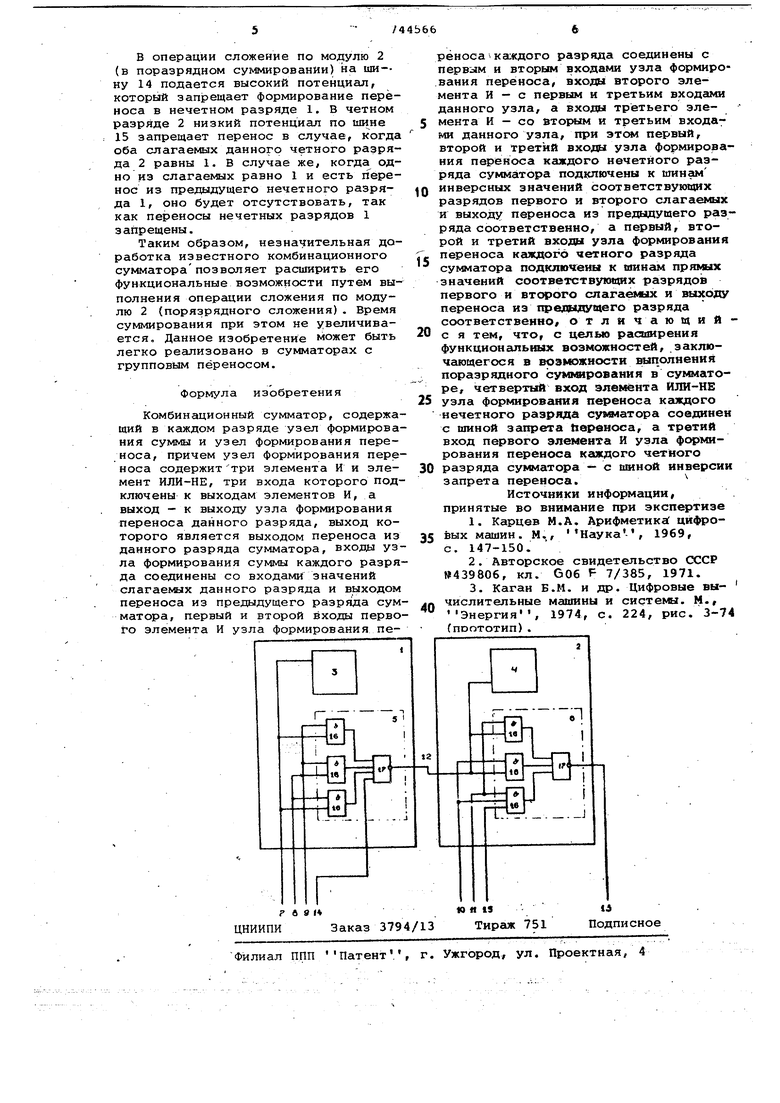

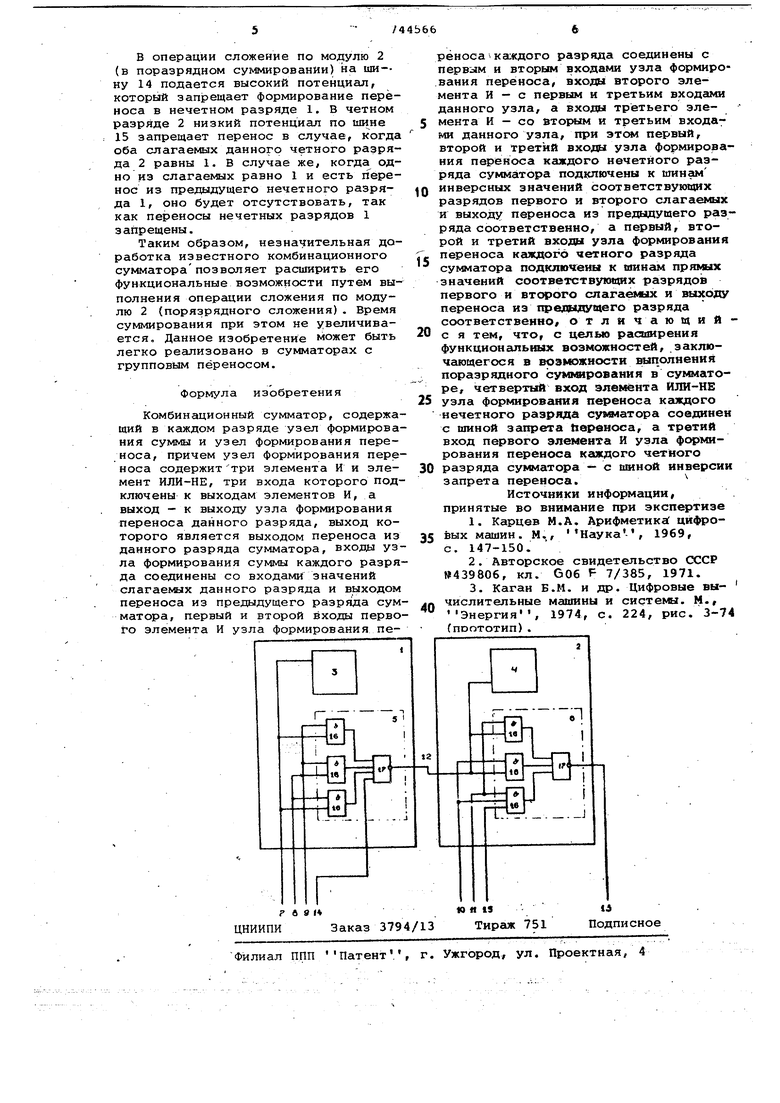

На чертеже представлена функциоальная схема двух разрядов комбиационного сумматора.

Нечетный (21-1)-и и четный (2i)-t( разряды сумматора 1 и 2 содержат узлы 3 и 4 формирования сумм; узлы 5 и 6 формирования переносов соответственно (21-1)-го и (21)-горазрядов сумматора 1 и 2; вход 7 инверсного значения переноса из (21-2)-го

разряда; шины 8 и 9 инверсных значений слагаемых нечетного разряда сумматора 1; шины 10 и 11 прямых значейий слагае1 1ых четного разряда сумf aTopa 2; выход 12 прямого значения переноса (21-1)-го разряда сумматора 1; выход инверсного значения переноса 13 (21)-гО разряда сумматора 2; шину 14 запрета переноса,

шину 15 инверсии запрета переноса; элементы И 16 и ИЛИ-НЕ 17.

Узел 5 формирования переноса нечетного (21-1)-го разряда 1 формирует функцию

гг-- - --

2iV 21-, V1 i-1Sv2 ai-,S,,.a

где а .г Ь . - инверсные значения

соответственно первоГО И второго слагаемых, которые поданы на шины 8, 9; - инверсное значение пе21-2реноса из (21-2)-го разряда, которое подано на вход 7; . 3 - сигнал запрета переноса, поданный на шину 14.

Узел 6 формирования переноса четного (21)-го разряда формирует функцию

C,r- 2i 2i baiSi-H

где а, Ь - npHtJShse значения первого и второго слагаемых, которые поданы соответственно на шины 10;

прямое значение предыдущего (нечетного 21-1-го) разряда, которое образуется на выходе 12;

3 - сигнал инверсии пере-, носа, поданный на ши0ну 15.

Сигнал по шине запрета переноса 14 разрешает или запрещает прохождение сигнала переноса по цепи переноса.

ij В сйучае выполнения операции арифметического сложения на шину 14 подается низкий потенциал, который разрешает формирование переноса в нечетном разряде 1 и его распространение в четный разряд сумматора 2. При О этом на вход узла 6 формирования переноса четного разряда 2 по шине 15. поступает высокий потенциал и разрешает формирование переноса в четном разряде 2, когда оба слагаемых четного разряда 2 равны 1,

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор с управляемым переносом | 1971 |

|

SU439806A1 |

| Комбинационный сумматор | 1979 |

|

SU849207A1 |

| Сумматор со сквозным переносом | 1977 |

|

SU705445A1 |

| Сумматор с параллельным переносом | 1977 |

|

SU744557A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1291969A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Двоично-десятичный сумматор | 1977 |

|

SU746509A1 |

| Ячейка однородной структуры | 1990 |

|

SU1805461A1 |

| Устройство для суммирования избыточных кодов | 1986 |

|

SU1341632A1 |

Авторы

Даты

1980-06-30—Публикация

1978-03-07—Подача