113

Изобретение относится к вычисли тельной технике и может быть использовано при построении специализированных цифровых систем контроля, регистрации и управления.

Цель изобретения - увеличение быстродействия и упрощение устройства.

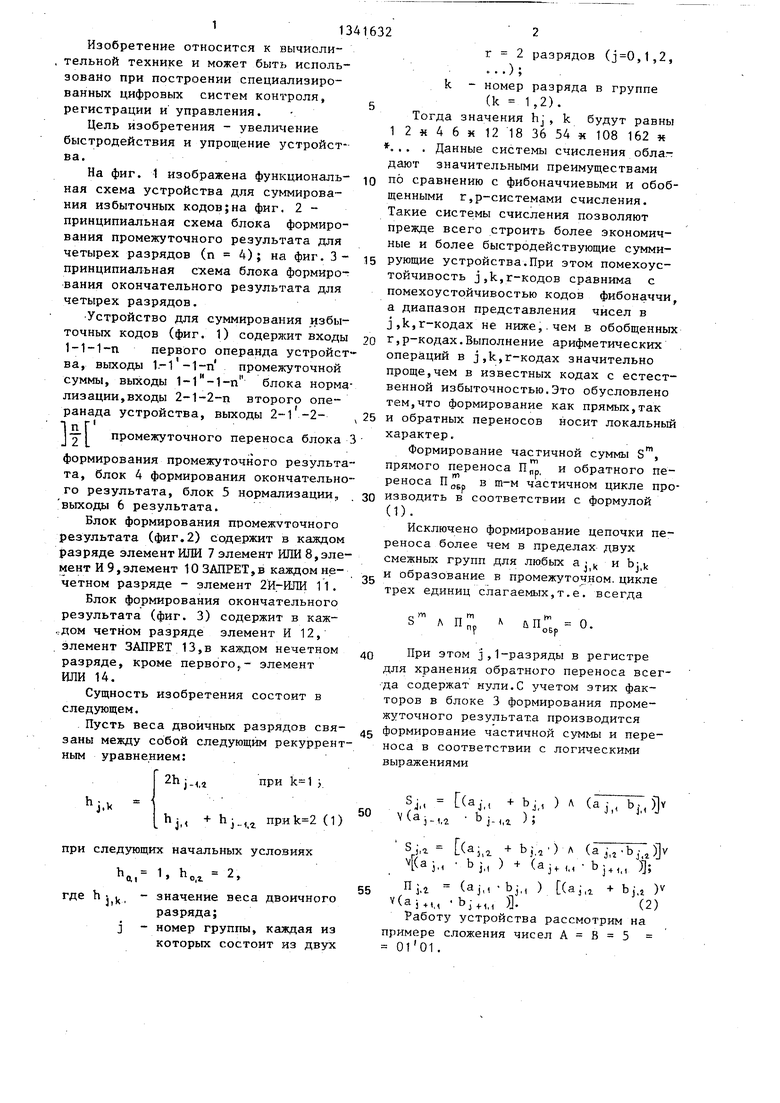

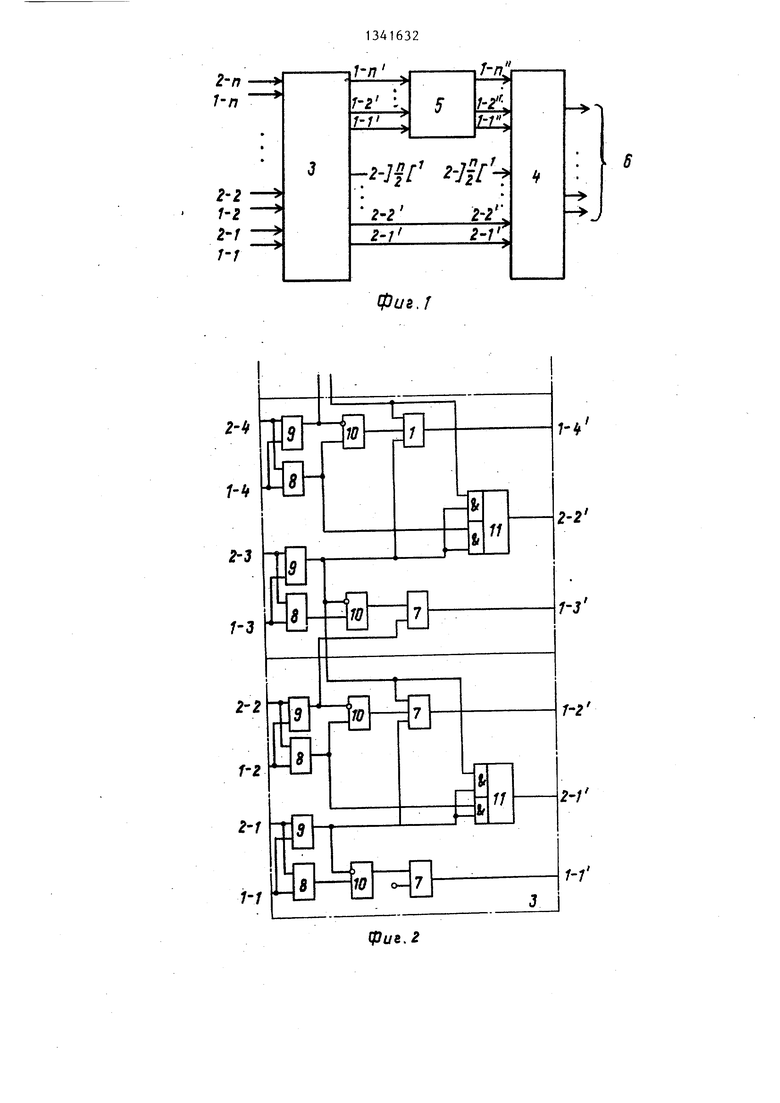

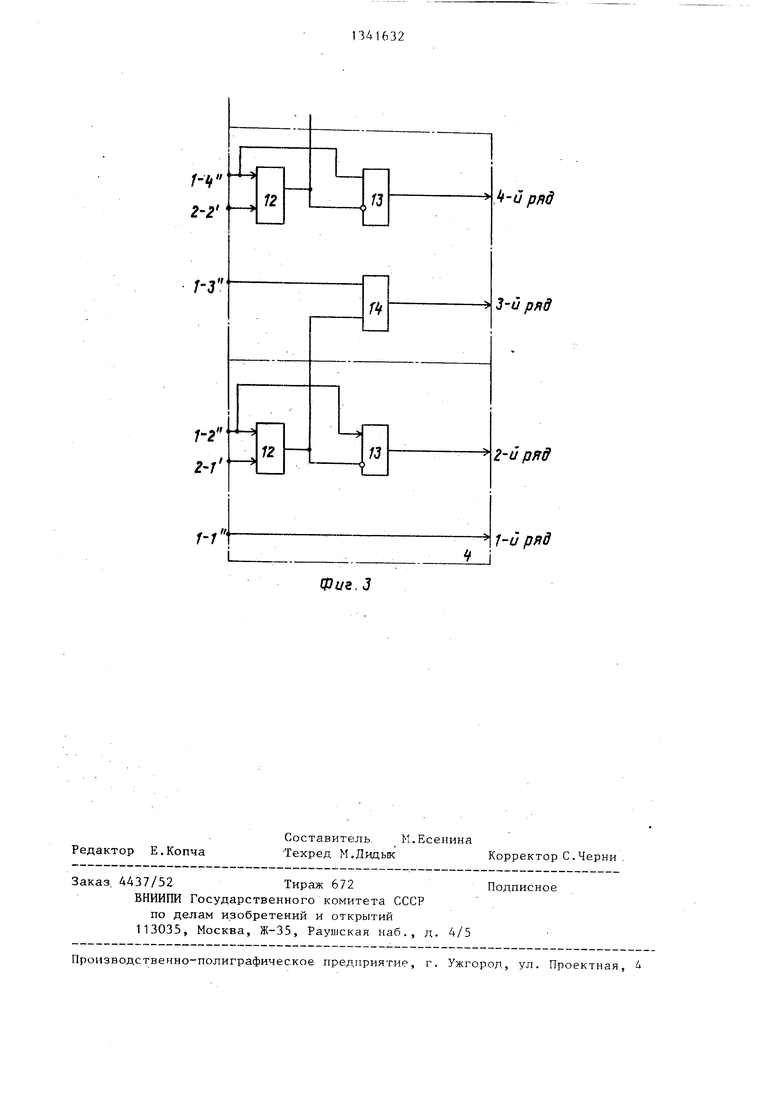

На фиг. 1 изображена функциональная схема устройства для суммирования избыточных кодов;на фиг. 2 - принципиальная схема блока формирования промежуточного результата для четырех разрядов (п 4); на фиг. 3- принципиальная схема блока формирования окончательного результата для четырех разрядов.

Устройство для суммирования избыточных кодов (фиг. 1) содержит входы 1-1-1-п первого операнда устройст

ва, выходы 1-1 -1-п

суммы, выходы 1-1 -1-п

промежуточной

блока нормализации, входы 2-1-2-п второго one- ранада устройства, выходы 2-1 -2-

-г- промежуточного переноса блока 3

формирования промежуточного результата, блок 4 формирования окончательного результата, блок 5 нормализации., выходы 6 результата.

Блок формирования промежуточного результата (фиг.2) содержит в каждом разряде элемент ШШ 7 элемент ИЛИ 8,элемент И 9, элемент 10 ЗАПРЕТ, в каждом нечетном разряде - элемент 2И-ИШ 11.

Блок формирования окончательного результата (фиг. 3) содержит в каж- дом четном разряде элемент И 12, элемент ЗАПРЕТ 13,в каждом нечетном разряде, кроме первого,- элемент ИЛИ 14.

Сущность изобретения состоит в следующем.

Пусть веса двоичных разрядов связаны между собой следующим рекуррентным уравнением:

2h

J-(,2

при ,

j.V

J

h-, (1)

следующих начальных условиях

ha, 1. Ь„, 2, h , 1,. - значение веса двоичного

j,k. J о,г

значение

разряда;

номер группы, каждая из

которых состоит из двух

0

г 2 разрядов (,1,2, ...); k - номер разряда в группе

(k 1,2).

Тогда значения hj, k будут равны 1 2 « 4 6 к 12 18 36 54 к 108 162 к . . . . Данные системы счисления обладают значительными преимуществами по сравнению с фибоначчиевыми и обобщенными г,р-системами счисления. Такие системы счисления позволяют прежде всего строить более экономичные и более быстродействующие суммирующие устройства.При этом помехоустойчивость j,k,r-кoдoв сравнима с помехоустойчивостью кодов Фибоначчи, а диапазон представления чисел в j,k,r-кoдax не ниже,.чем в обобщенных г,р-кодах.Выполнение арифметических операций в j,k,r-кoдax значительно проще,чем в известных кодах с естественной избыточностью.Это обусловлено тем,что формирование как прямых,так 25 и обратных переносов носит локальньй характер.

Формирование частичной суммы s,

и обратного пе- про15

20

30

прямого переноса П„„ „тГ

реноса п в т-м частичном цикле

изводить в соответствии с формулой (1).

Исключено формирование цепочки переноса более чем в пределах двух

смежных групп для любьпс а

35

J.k

и Ь

j.k

и образование в промежуточном, цикле трех единиц слагаемых,т.е. всегда

П

F

ЬП

ОБр

0.

При этом j,1-разряды в регистре для хранения обратного переноса всег- да содержат нули.С учетом этих факторов в блоке 3 формирования промежуточного результата производится формирование частичной суммы и переноса в соответствии с логическими выражениями

V(aj,,, -bj,,, ).(2)

Работу устройства рассмотрим на примере сложения чисел А В 5 Ol OI.

соответству На выходах 1-1 и

31

На входы 1-1,2-1, 1-3, 2-3 блока 3 поступают единичные сигналы (фиг. 2 в результате чего возбуждаются выходы элементов И 9 соответствующих разрядов,которые через время t запрещают прохождение единичного сигнала с выходов элементов ИЛИ 8 соответствующих разрядов через элементы 10 ЗАПРЕТ соответствующих разрядов на входы элементов ИЛИ 7 ющих разрядов

1-3 будут нулевые сигналы, что действительно соответствует S , Sj., О при подстановке а ,, - Ь,, 0 и а, Ь, 0 в уравнение (2) для Sj,2 . Так как на входах 1-2, 2-2, 1-4, 2-4 блока 3 присутствуют нулевые сигналы, то элементы И 9 соответствующих разрядов, элементы ИЛИ 8 соответствующих разрядов и элементы 10 ЗАПРЕТ третьего и четвертого разрядов не срабатывают. На входе элемента РШИ 7 второго разряда устанавливается единичный сигнал, так как на первом и третьем входах присутствуют единичные сигналы.Элемент ИЛИ 7 четвертого разряда срабатывает только по первому входу (так, как в данном случае ). В результа

те на выходах блока 3 1-2 и 1-4 будут единичные.сигналы, что действительно соответствует S Sj 1 при подстановке а ,, -bi.z 1 и 2.1 2,, 1 в уравнение (2) .

Единичными сигналами с выходов . элементов И 9 первого и третьего разрядов срабатывает один из входных элементов И элемента 2И-Ш1И 11 первого разряда. Так как на третий вход элемента ИЛИ 7 четвертого разряда по дается нулевой сигнал () и на входе элемента ИЛИ 8 четвертого разряда будет нулевой сигнал,то на выходе элемента 2И-ИЛИ 11 второго разряда будет также нулевой сигнал.Это соответствует значению П . 1 и при подстановке а ,, b . 1 и

1,1 г, 1 в (2) для Hj .i .

В результате на выходах 1-4-1-1 блока 3 будет соответственно установлен код Sj.k 10 10, а на выходах 2-2 и 2-Г - код ,.Код Sj,k 10 Ю для j,k,r-кoдoв представлен в основной форме. Поэтому на выходах 1-4 -1-1 5 лизации установлен код S

J,k

нормаю ю.

I

Так как на шинах 2-Г присутствуют единичные сигналы,то еди

ничным сигналом с выхода элемента И 12 первого разряда через время t запрещается прохождение единичного сигнала на выходе элемента ЗАПРЕТ первого разряда, а на выходе элемента ИЛИ 14 первого разряда устанавливается единица в третьем разряде результата.

Нулевым сигналом с выхода элемента И 12 второго разряда (на щине 2-2 становлен нулевой сигнал) разрешается прохождение единичного сигнала с входа 1-4 блока 3 через элемент 13 ЗАПРЕТ второго разряда на выход устройства, соответствующий четвертому разряду результата. В результате на выходе устройства будет установлен код 11 00, что соответствует

А+В 10,0 11 00.

20

Формула изобретения

Устройство для суммирования избыточных кодов, содержащее блок формирования промежуточного результата блок нормализации, отличающееся тем,что,с целью увеличения быстродействия и упрощения устройства, введен блок формирования окончательного результата,первая и вторая группы входов блока формирования промежуточного результата соединены соответственно с входами первого и второго операндов устройства, выходы промежуточной суммы блока формирования промежуточного результата соединены соответственно с входами блока нормализации,выходы которого соединены соответственно с входами первой группы блока формирования окончательного результата выходы которого соединены соответственно с выходами результата устройства, входы в торой группы блока форми;35

45

рования окончательного результата соединены соответственно с выходами промежуточного переноса блока формирования промежуточного результата, блок формирования промежуточного ре50 зультата в каждом разряде содержит элемент И первой и второй элементы ИЛИ, элемент ЗАПРЕТ и в каждом нечетном разряде элемент 2И-ИЛИ,первые входы элемента И и первого элемента

55 ИЛИ данного разряда блока формирования промежуточного результата соединены с соответствующим входом первой группы блока формирования промежуточного результата,вторые входы.

513

первого элемента И и первого элем-; та ИЛИ данного разряда блока формирования промежуточного результата соединены с соответствующим входом второй группы блока формирования промежуточного результата,выход первого элемента ИЛИ нечетного разряда блока формирования промежуточного результата соединен с прямым входом элемента ЗАПРЕТ того же нечетного разряда блока формирования промежуточного результата, инверсный вход которого соединен с выходом элемента И данного разряда блока формирования промежуточного результата,с первьм и вторым входами элемента 2И-Ш1И данного разряда блока формирования -промежуточного результата и первым входом второго элемента ИЛИ следующего четного разряда блока формирования промежуточного результата, выход первого элемента ИЛИ данного четного разряда блока формирования промежуточного результата соединен с прямым входом элемента ЗАПРЕТ данного разряда и третьим входом элемента 2И-ИЛИ предыдущего нечетного разряда блока формирования промежуточного результа.та,выход элемента И четного разряда блока формирования промежуточного результата соединен с инверсным входом элемента ЗАПРЕТ данного разряда блока формирования промежуточного результата и первым входом второго элемента ИЛИ следующего нечетного разряда блока формирования промежуточного результата, выход элемента ЗАПРЕТ данного разряда блока формирования Промежуточного результата соединен с вторым входом второго элемента ИЛИ . данного разряда блока формирования промежуточного результата,выход элемента И нечетного разряда блока формирования промежуточного результата соединен с третьим входом второго элемента ИЛИ предыдущего четного разряда блока формирования промежуточного результата и четвертым входом элемента 2И-Ш1И предьщущего нечетного разряда блока формирования промежутоного результата выходы вторых элеметов РШИ блока формирования промежутоного результата соединены с выходами

5

0

50 соответствующих разрядов промежуточной суммы блока формирования промежуточного результата,выходы элементов 2И-ИЛИ блока формирования промежуточного результата соединены с выходами соответствующих разрядов промежуточного переноса блока формирования промежуточного результата, блок формирования окончательного результата содержит в каждом четном разряде элемент И, элемент ЗАПРЕТ, в каждом нечетном разряде, кроме первого - элемент НШ, вход первого разряда второй группы блока формирования окончательного результата соединены с выходом первого разряда блока формирования окончательного результата, первые входы элементов И четного разряда блока формирования окончательного результата соединены с входами соответствующих разрядов первой группы блока формирования окончательного результата,вторые входы элементов И и прямые входы элементов ЗАПРЕТ 5 четных разрядов блока формирования окончательного результата сдединены с входами соответствующих четных.разрядов первой группы блока формирования окончательного результата,первые входы элементов ИЛИ нечетных разрядов блока формирования окончательного результата соединены с входами соответствующих разрядов,кроме того, первой группы блока формирования окончательного результата, выход элемента И данного четного разряда блока формирования окончательного результата соединен с инверсным входом элемента ЗАПРЕТ данного четного разряда блока формирования окончательного результата и вторым входом элемента ИЛИ следующего нечетного разряда блока формирования окончательного результата,выход которого соединен с выходом соответствующего нечетного разряда блока формирования окончательного результата, выходы элементов ЗАПРЕТ данного четного разряда блока формирования окончательного результата соединены с выходами соответствующего четного разреда блока фор- - мирования окончательного результата ,

0

5

0

5

2 п 1-п

2-2

1-2 2 Г

г-г

Фиг.Г

Фие.2

фцг.З

Редактор Е.Копча

Составитель. М.Есенина

Техред МоДицыкКорректор С.Черни

Заказ. 4437/52Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, i

t-u pfld

3-й ряд

2-й pffd

1-й ряд

| название | год | авторы | номер документа |

|---|---|---|---|

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ПОРЯДКА ПРИ НОРМАЛИЗАЦИИ ЧИСЕЛ | 2017 |

|

RU2638724C1 |

| Делитель частоты импульсов | 1985 |

|

SU1298907A1 |

| Отсчетное устройство | 1976 |

|

SU661548A1 |

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| Устройство для выделения значащих разрядов из последовательности многоразрядных двоичных кодов | 1982 |

|

SU1038935A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для масштабирования числа в интервально-модулярном коде | 1986 |

|

SU1305678A1 |

| Вычислительное устройство | 1984 |

|

SU1176322A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных цифровых систем контроля, регистрации и .управления.Цель изобретения - увеличение быстродействия и упрощение устройства. Устройство для суммирования избыточных кодов содержит блок формирования промежуточного результата, блок нормализации, блок формирования окончательного результата. 3 ил. сл с: 00 4 О5 СО

| Соловьев Г.Н | |||

| Арифметические устройства ЭВМ | |||

| М.: Энергия, 1978, с | |||

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU102A1 |

| Суммирующее устройство | 1979 |

|

SU824200A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-30—Публикация

1986-02-07—Подача