Изобретение относится к вычислительной технике, в частности к устройствам, выполняющим арифметические операции в цифровых вычислительных машинах.

Известны комбинационные сумматоры с ускоренным переносом, построенные на многовходовых элементах fl и 2.

Недостатком таких сумматоров является наличие большого количества внутренних и межразрядных связей, что приводит к увеличению оборудования и снижению надежности.

Наиболее близким к изобретению является сумматор, содержащий в каждом разряде два сумматора по модулю два и узел формирования переноса Гз.

Однако известный сумматор содержит сравнительно большое количество элементов.

Цель изобретения - сокращение количества оборудования сумматора.

Поста1вленная цель достигается тем, что в сумматоре,содержащей в каждом нечетном разряде сумматор по модулю два и узел формирования переноса и в каждом четном ра-зряде - два сумматора по модулю лва и узел формирования переноса, причем входы первого сумматора по модулю два в каждом разряде подключены к входам операндов данного разряда комбина°ционного сумматора, узел формирования переноса содержит элемент 2И-ИЛИНЕ, причем э каждом четном разряде комбинационного сумматора входы второго сумматора по модулю два подключены к выходу первого сумматора по модулю два и входу переноса из

10 предыдущего разряда, а выход является выходом суммы данного разряда комбинационного сумматора, входы элемента 2И-ИЛЙ-НЕ узла формирования переноса первой группы подключе15ны к входам операндов данного разряда комбинационного сумматора, входы элемента 2И-ИЛИ-НЕ узла формирования переноса второй группы - к выходу первого сумматора по модулю

20 два данного разряда комбинационного сумматора и входу переноса из предыдущего разряда комбинационного сумматора, выход элемента 2И-ИЛИ-НЕ .узла формирования переноса является вы25ходом инверсии переноса в последующий разряд комбинационного сумматора, в каждый нечетный разряд введены элемент 2И-ИЛИ-НЕ и элемент НЕ, причем в каадом нечетном разряде комби30национного сумматора входы, элемента

2И-ИЛИ-НЕ узла формирования переноса первой группы соединены с входами инверсий операндов данного разряда комбинационного сумматора, входы элемента 2И-ИЛИ- 1Е узла формирования переноса второй группы соединены с выходом первогосумматора по модулю два данного разряда комбинационного сумматора и входом инверсии переноса на предьздущего разряда комбинационного сумматора, входы элемента 2И-ИЛИ-НЕ первой группы соединены с входом инверсии переноса из предыдущего разряда комбинационного сумматора и через элемент НЕ с выходом первого сумматора по модулю два данного разряда комбинационного сумматора, входы элемента 2И-ИЛИ-НЕ второй группы соединены с выходом первого сумматора по модулю два и выходом элемента 2И-ИЛИ-НЕ узла формирования переноса, являющегося выходом переноса в последующий разряд комбинационного сумматора.

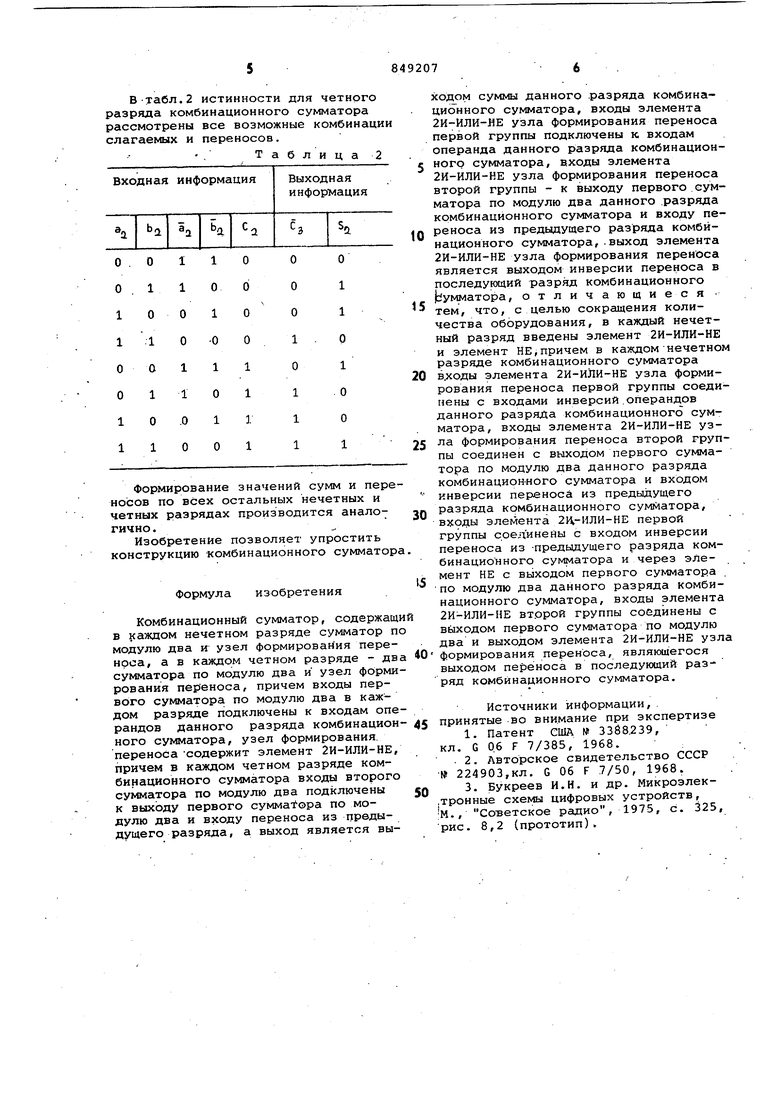

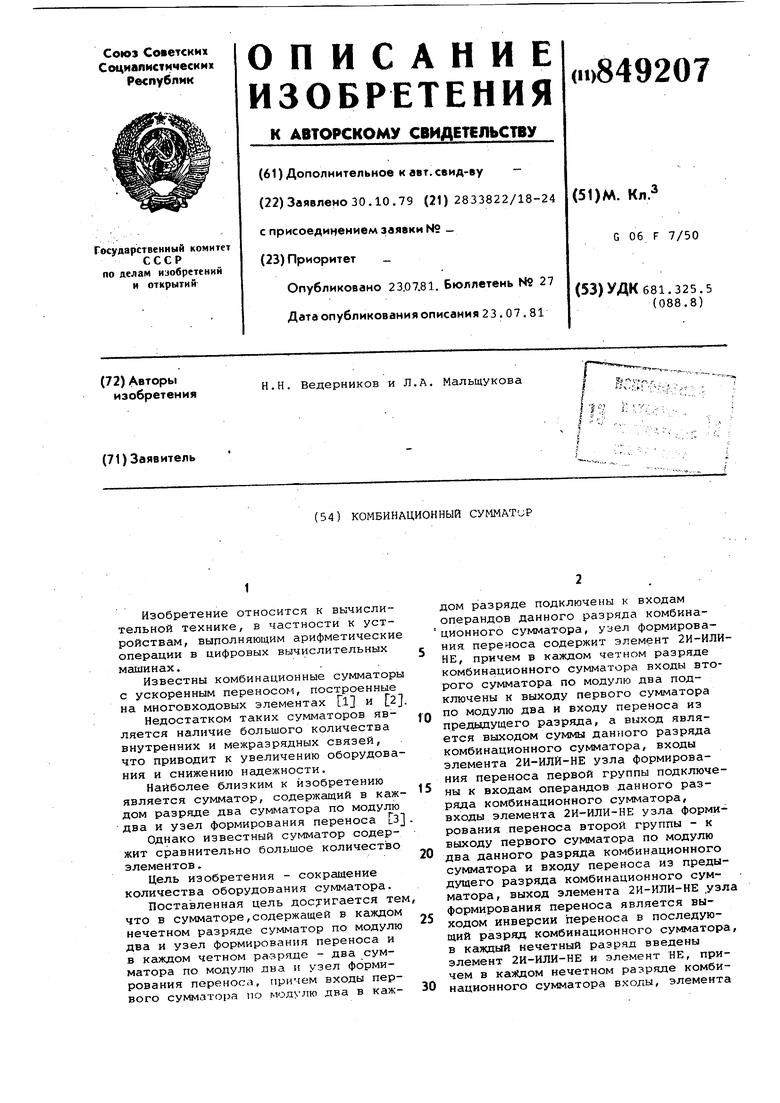

На фиг. 1 изображена схема двух разрядов комбинационного сумматора; на фиг. 2 - вариант выполнения разрядов сумматора на элементах И-НЕ.

Нечетный разряд 1 сумматора содержит сумматор 2 по модулю два, выполненный на элементе 3 2И-ИЛИ-НЕ, узел 4 формирования переноса, выполненный на элементе 5 2И-ИЛИ-НЕ,элемент 6 НЕ и элемент 7 2И-ИЛИ-НЕ.Четный разряд.8 сумматора содержит сумматор 9 по модулю два, выполненный на элементе 10 2И-ИЛИ-НЕ, узел 11 формирования переноса, выполненный на элементе 12 2И-ИЛИ-Н.Е, и сумматор 13 по модулю два, выполненный на элементе 14 2И-ИЛИ-НЕ.

Со входами сумматора 2 по модулю два соединены входы 15-18 прямых и. инверсных значений операндов соответствующего разряда сумматора (а, Ь- , а и Б.,) . Входы 17 и 18 инверсных значений операндов (а., и ) соединены также с входаиии одной группы . узла 4, зходы .другой группы которого соединены с выходом сумматора 2 по модулю два и входом 19 инверсии переноса в данный разряд (C-i). Выход сумматора 2 и выход .узла 4, который является выходом 20 переноса (C/j) в последующий четный разряд 8 сумматора, соединены с входами одной группы элемента 7 2И-ИЛИ-НЕ, входы другой группы которого подключены к входу 19 и выходу элемента б НЕ, вход которого- соединен с выходом сумматора 2, на выходе 21 формируется значение суммы данного разряда CS-i),

Входы сумматора 9 соединены с входами 22-25 инверсных и прямых значений операндов соответствующего разряда сумматора (5/, Ь.;, b)..: Входы 24 и 25 прямых значейий операндов соединены с входами одной группы узла 11, входы другой группы которого

соединены с выходом сумматора 9 и входом 26 переноса из предыдущего райряда, на который поступает значение переноса Cj с выхода 20. На выходе 27 узла 11 формируется.инверсия переноса в последующий разряд сумматора (Cj). Выход сумматора 9 и вход 26 соединены с входами сумматор .13 (с прямыми входами первой группы Ьлемента 14 2И-ИЛИ-гНЕ и инверсными входами второй группы того же элемента) , на выходе 28 которого формируется значение суммы Sj данного.разряда.

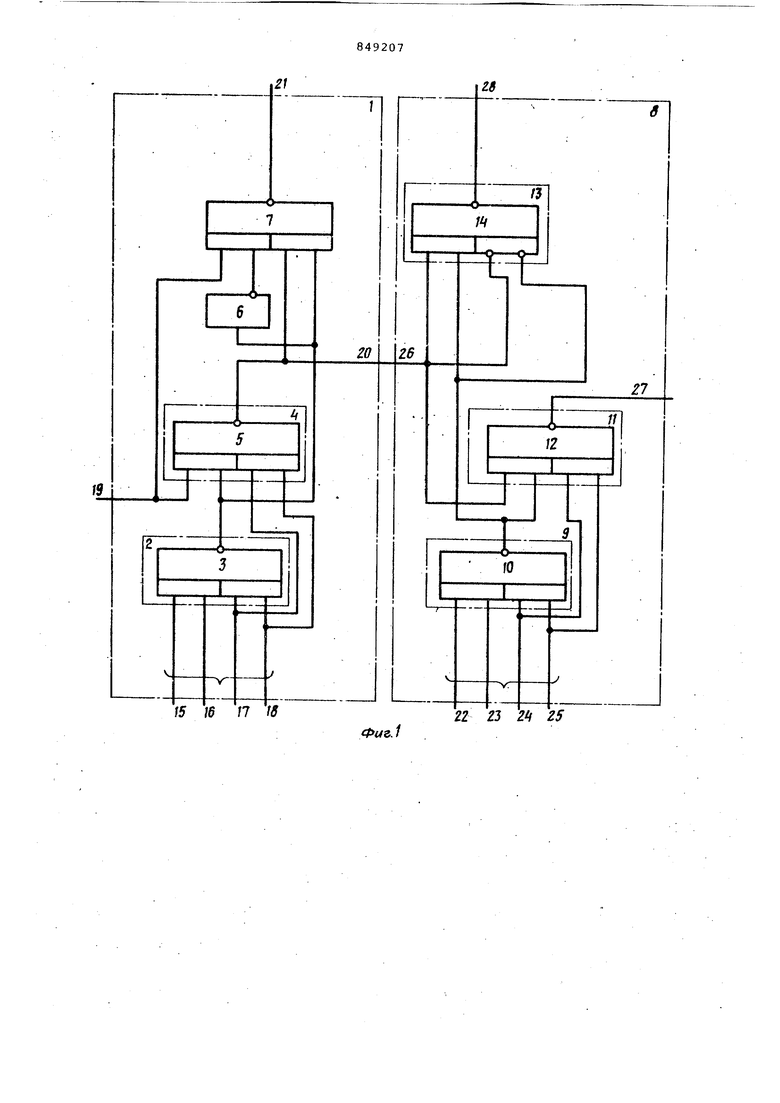

Вместо использования элементов 2И-ИЛИ-НЕ (в том числе, в составе сумматоров 2, 9 и 13 и узлов 4 и 11) возможна эквивалентная замена на двухвходовые элементы И-НЕ 2.9-43 с объединением из выходов (фиг.2).

Значение переноса Сдиз нечетного разряда 1 реализуется по формуле

C:j,-q.,(a-,®bJc ,

где V - знаки логических операций ИЛИ; © - знак сложения .по модулю два. Значение инверсии переноса Сз из четного разряда 8 реализуется по формуле

Cj ajl32(ai®txj)c.j .

Значение суммы S нечетного разряда 1 реализуется по формуле

5.

(Од® Ъ) N (©t)c,j .

Значение суммы Зачетного разряда 8 реализуется по формуле

S2(,j)®c,,,.

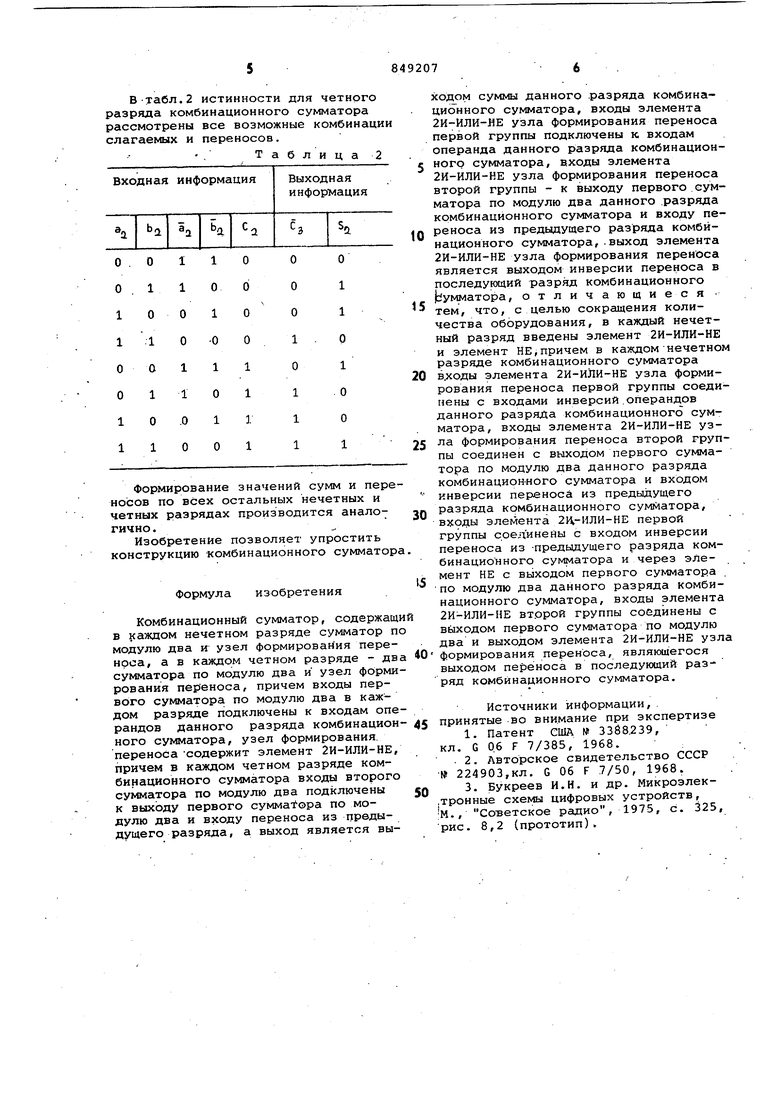

В табл.1 истинности для нечетног разряда комбинационного сумматора рассмотрены все возможные комбинации слагаемых и переносов.

Таблица 1 В-табл.2 истинности для четного разряда комбинационного сумматора рассмотрены все возможные комбинаци слагаемых и переносов. Таблица2 Формирование значений сумм и пер носов по всех остальных нечетных и четных разрядах производится аналогично. Изобретение позволяет упростить конструкцию комбинационного суммато Формула изобретения Комбинационный сумматор, содержа в каждом нечетном разряде сумматор модулю два и узел формирования пере носа, а в каждом четном разряде - д сумматора по модулю два и узел форм рования переноса, причем входы первого сумматора по модулю два в каждом разряде подключены к входам оп рандов данного разряда комбинацие ного сумматора, узел формирования, переноса содержит элемент 2И-ИЛИ-НЕ причем в каждом четном разряде комбинационного сумматора входы второг сумматора по модулю два подключены к выходу первого сумматора по модулю два и входу переноса из предыдущего разряда, а выход является вы ходом суммы данного разряда комбинационного сумматора, входы элемента 2И-ИЛИ-ЙЕ узла формирования переноса первой группы подключены к входам операнда данного разряда комбинационного сумматора, входы элемента 2И-ИЛИ-КЕ узла формирования переноса второй группы - к выходу первого . сумматора по модулю два данного разряда комбинационного сумматора и входу переноса из предыдущего разряда комбинационного сумматора,.выход элемента 2И-ИЛИ-НЕ узла формирования переноса является выходом инверсии переноса в последующий разряд комбинационного liyNwaTopa, отличающиеся тем, что, с целью сокращения количества оборудования, в каждый нечетный разряд введены элемент 2И-ИЛИ-НЕ и элемент НЕ,причем в каждом-нечетном разряде комбинационного сумматора В.ХОДЫ элемента 2И-ИЛИ-НЕ узла формирования переноса первой группы соединены с входами инверсий.операндов данного разряда комбинационного сумматора, входы элемента 2И-ИЛИ-НЕ узла формирования переноса второй группы соединен с выходом первого сумматора по модулю два данного разряда комбинациоННого сумматора и входом инверсии переноса из предыдущего разряда комбинационного сумматора, входы элемента 2Ц-НЛИ-НЕ первой группы соединены с входом инверсии переноса из -предыдущего разряда комбинационного сумматора и через элемент НЕ с выходом первого сумматора по модулю два данного разряда комбинационного сумматора, входы элемента 2И-ИЛИ-НЕ второй группы соединены с выходом первого сумматора по модулю два и выходом элемента 2И-ИЛИ-НЕ узла формирования переноса, являющегося выходом neipesHOca в последующий разряд комбинационного сумматора. Источники информации,, принятые во внимание при экспертизе 1. Патент США № 3388.239, кл. G 06 F 7/385, 1968. . 2. Авторское свидетельство СССР № 224903,кл. G 06 F 7/50, 1968. 3. Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств, М., Советское радио, 1975, с. 325, рис. 8,2 (прототип).

21

ZS

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный сумматор | 1978 |

|

SU744566A1 |

| Накапливающий сумматор | 1984 |

|

SU1174921A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Накапливающий сумматор | 1984 |

|

SU1251069A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2021632C1 |

| Устройство для умножения по модулю М=2 @ -1 | 1986 |

|

SU1383339A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Накапливающий перемножитель | 1981 |

|

SU987618A1 |

/5 /б Л 8

Z6

fO

2Z Z3 Zff Z5

Фие.1 /5 16 7 IS ZZ 2:5

Фиг. 2 2 Z5

Авторы

Даты

1981-07-23—Публикация

1979-10-30—Подача