Изобретение относится к вычислительной технике и предназначено для построения вычислительных структур, работающих в режиме мультипользования, в которых производится контроль правильности работы процессоров каждого пользователя. Известны микропроцессорные вычислительные структуры высокой производительности, избыток вычислительной мощности которых создается за счет организации режима мультипользования. Каждая задача, или каждый пользователь получают в свое расгюряжени один или несколько решающих блоков структуры {1, Однако в режиме мультипользования ошибки могут возникать одновременно в задачах, решаемых разными пользевателями. . Наиболее близкой по технической сущности к предлагаемой является вычислительная структура, которая содержит набор решающих блоков, каждый из которых включает в себя вычислительный узел, соединенный с узлом контроля, блок управления, соединенный с вычислительными узлами решающих блоков, и блок ввода-вывода, соединенный с блоком управления/ и информационными шинами решающих блоков 2. Недостаток известной вычислительной структуры заключается в том, что, работая в режиме мультипользования, она не может селектировать сигналы ошибок, т. е. вьщавать их отдельно тем пользователям, в решении задач которых произошла ошибка. Цель изобретения - расширение функциональных возможностей за счет селекции сигналов ошибок в режиме мультипользования. Поставленная цель достигается тем, что в вычиалительную структуру, содержащую п решающих блоков, каждый из которых включает в себя вычислительный узел, выход которого подключен :к первом f входу узла контроля, блок управления, выход которого соединен со входами всех вычислительных узлов,вход-выход блока управления подключен к первому выходу-входу блока ввода-вывода, второй вход блока ввода-вывода соединен с выходами п решающих блоков, введен приоритетный блок, а в каждый решающий блок - узел памяти, узел сравнения, ког мутатор вывода и

коммутатор управления, причем в каждом решающем блоке выход узла памяти подключен к первым входам узла сравнения и коммутатора вывода, выходы коммутаторов вывода соединены с входом блока ввода-вывода, выход блока управления соединен с входами УЗЛОВ памяти, вторыми входами узлов сравнения и контроля, вторые входы узлов контр ля и коммутаторов вывода

подключены к соответствующим выходам приоритетного блока, входы которого подключены соответственно к выходам коммутаторов управления, выход блока, ввода-вывода соединен с третьими входами узлов сравнения, выход узла контроля в каждом решающем блоке соединен с третьим входом комму.татора вывода и первым входом коммутатора управления, второй вход которого подключен к выходу узла сравнения в каждом решающем блоке, выход приоритетного блока соединен со входом блока управления.

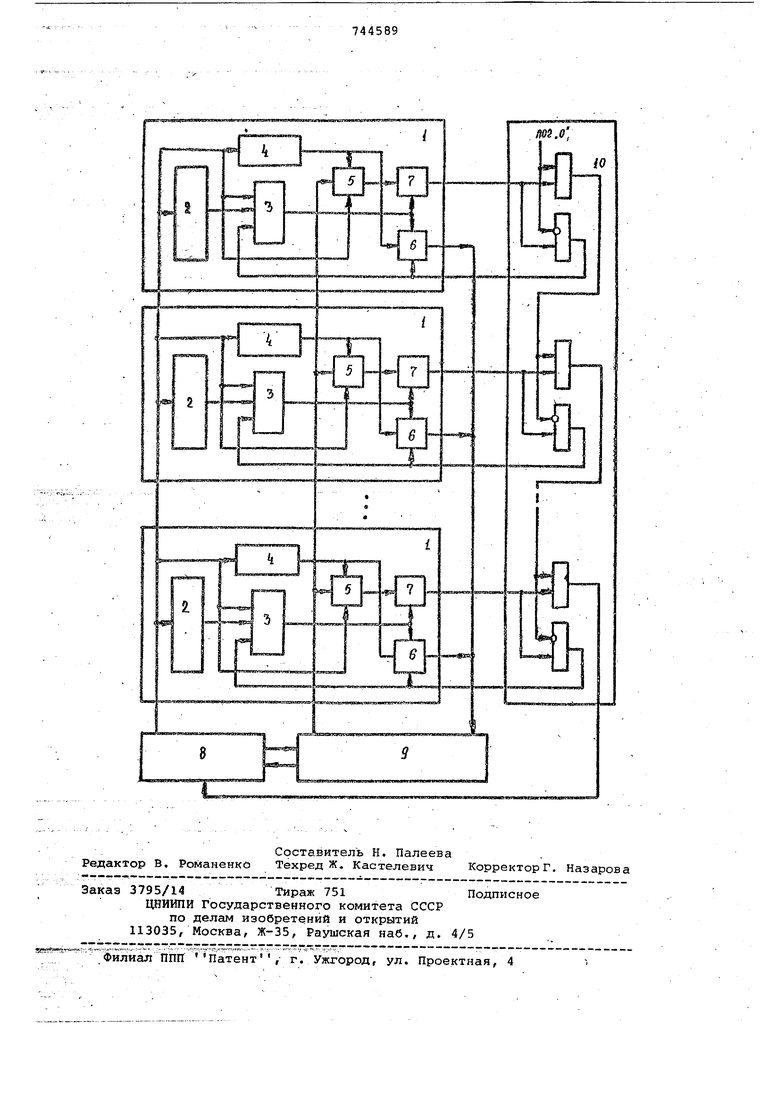

На чертеже представлена блок-схема вычислительной структуры.

Структура содержит набор решающих блоков 1, каждый из которых включает в себя вычислительный узел 2 и узел 3контроля, узел 4 памяти, узел 5 сравнения,коммутатор б вывода, коммутатор 7 управления. В состав структуры входит также блок 8 .управления, блок 9 ввода-вывода, приоритетный блок 10. . ,

Узел 4 памяти предназначен для хранения номера пользователя и номера решающего блока, причем номер решающего блока представлен двоичным кодом, а номер пользователя определяется положением логической единицы в узле памяти.

Функционирование вычислительной структуры рассматривается в предположении, что пользователи распределят решающие блоки 1 между собой произольным образом, при этом каждый ользователь заносит логическую едиицу в соответствующий разряд узла каждого из занятых им решающих локов 1.

Допустим, что в задачах, решаемых разными пользователями, одновременно происходят сбои, тогда единичные сигналы с выходов узлов 3 тех реш:аюих блоков 1, где это происходит, открывают вторые входы соответствуюих коммутаторов 7-, и номера пользователей из узла 4 поступают в блок 9. В блоке 9 производится селекция этих номеров и каждый из пользоватеей получает сигнал б наличии сбоев в решаемой им задаче.

Каждому пользователю, получающему такой сигнал, необходимо ysHjiTb занятых им решающих блоков 1, теЩраГТЯ|юШх6дйтсбой.Для этогопользователь подает через блок 9 а блок 8 команду управления, где

она дешифрируется-и передается на узлы 5 всех решающих блоков 1. На эти же узлы пользователь передает из блока 9 свой номер. По данной команде управления в узлах 5 всех решающих блоков производится одновременное сравнение номеров пользователей, хранящихся в узле 4 решающих блоков 1 с номером пользователя, поступающим из блока 9.

В тех решающих блоках 1, где происходит совпадение этих номеров, на выходе узла 5 появляется сигнал, который открывает первый вход коммутатора 7. Очевидно, что это происходит только в тех решающих блоках 1, которые принадлежат данному пользователю. Номер отказавшего решающего блок.а 1 проходит через коммутатор 7 на вход блока 10. Этот блок введен для обеспечения последовательного вывода номеров решающих блоков 1,начиная с младшего и кончая старшим.

.Номер решающего блока 1 выдается в том случае, когда в решающих блоках с меньшими номерами отсутствуют сигналы сбоев.

Блок 8 управления перед подачей следующей команды анализирует информацию, поступающую с сигнального выхода блока 10. Если это единичная информация, то необходим переход вычислительной структуры к выполнению следующей команды пользователя.

Блок10 содержит элементы И и элементы ИЛИ, выход каждого из которых соединен с первым входом последующего элемента ИЛИ и инверсным входом последующего элемента И, а второ вход является входом блока 10, который подсоединен к прямому входу соответствующего элемента И, выход каждого элемента И является выходом блокаЮ.

В том случае, если в одном из решающих блоков происходит сбой, а в решающем блоке с меньшим по отношению к нему номером сбоя нет, то элемент И, соответствующий данному решающему блоку 1, выдает единичный сигнал, открывает третий вход коммутдтора 7 и разрешает вывод на блок 9 номера решающего блока 1. Когда вьшод номера решающего блока 1 оканчивается, узел 3 сигналом, поступающим от блока 8, сбрасывается в нулевое состояние, и далее производится вывод следующего номера решающего блока 1 со сбоем. Выход элемента ИЛИ соответствующего решающего блока со старшим номером. является сигнальным выходом блока 10.

Блок 8 выдает управляющие сигналы обеспечивающие правильную работу решающих блоков 1, исигналы сброса .узлов контроля тех решающих блоков, р которых происходит сбой. Изобретение обеспечивает.работу вычислительных структур ,с контролем правильности обработки информации в режиме мультипользования. Формула изобретения Вычислительная структура, содержащая п решающих блоков, каждый из .которых включает в себя вычислитель ный узел,выход которого подключен к первому входу узла контроля, блок управления, выход которого соединен со входами всех вычислительных узлов, вход-выход блока управления подключен к первому выходу-входу блока ввода-вывода, второй вход бло ввода-вывода соединен с выходами п решающих блоков, отличающа с я тем,что,с целью расширения функциональных возможностей за счет селекции сигналов ошибок в режиме .мультипользования, в нее введен при ритетный блок, а в каждый решающий блок - узел памяти, узел сравнения, коммутатор вывода и коммутатор уп.рйвления, причем в каждом решающем блоке выход узла памяти подключен к первым входам узла сравнения и коммутатора вывода, выходы коммутаторов/ вывбда co flaffeiffibi с входбм блока ввода-вывода, выход блока управления соедийен с входами узлов памяти, вторыми входами узлов сравнения и контроля, вторые входы узлов контроjjR и коммутаторов вывода подключены к соответствующим выходам приоритет-, него блока, входы которого подключены соответственно к выходам коммутаторов управления, выход блока ввода-вывода соединен с третьими входами узлов сравйения, выход узла контроля в каждом решающем .блоке соединен с третьим входом коммутатора вывода и первым входом коммутатора управления, второй вход которого подключён к выходу узла сравнения в каждом реигайщём блоке, выход приоритетного блока соединен со входом блока управления . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 572787, кл. G 06 F 9/00, 1977. 2.Отчет по НИР гос. 72018725, Таганрогский радиотехнический институт им. в.д. Калмыкова, 1972, с, 194-234 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка волновой коммутационной системы | 1980 |

|

SU934467A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| Цифровая интегрирующая структура | 1978 |

|

SU680001A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

Авторы

Даты

1980-06-30—Публикация

1978-02-22—Подача