регистра подынтегральной функции, рё гистра остатка интеграла, первого счетчика по модулю d,третий вход блока квантования соединены, с входом сброса цифрового интегратора, четвертый вход масштабного блока, четвертый вход блока квантования, вход третьего элемента задержки и управляющий вход блока сравнения соединены с входом конца итерации цифрового интегратора, второй выход блока квантования подключен к выходу приращения интеграла, а выход блока сравнения - к выходу контроля цифрового интегратора, отличающийся тем,, что, с целью сокращения аппаратурных затрат, в него введены второй и третий счетчики по модулю d и группа элементов задерж,ки, причем вЕЛчитающий и суммирующий входы второго счетчика по модулю d соединены соответственно с третьим

и четвертым выходами второго блока коммутации, пятыйвыход которого подключен к суммирующему входу третьего счетчика по модулю d, входы текущей установки второго и третьего счетчиков по модулю d соединены с выходом третьего элемента задержки, а входы начальной установки этих счетчиков соединены с входом сброса цифрового интегратора, единичные выходы каждого разряда третьего счетчика по модулю d соединены через элементы задержки группы с информа-ционными входами второго счетчика . по модулю d, выход которого соединен с вторым входом блока сравнения, выход марштабного блока соединен с входом второго слагаемого сумма тора подынтегральной функции и седьмьо 4 входом второго блока коммутации, выход первого элемента ИЛИ соединен с информационным входом регистра подын;тегральной функции и с восьмым входом второго блока коммутации, выход второго элемента ИЛИ соединен с информационным входом регистра остатка интеграла и девятьм входом второго блока коммутации, выход регистра остатка интегргша соединен с десятьм входом второго блока коммутации.

2. Интегратор по п. 1, о тли ч ю щ и и с я тем, что второй блок ком мутации содержит элемент ИЛИ-НЕ, двенадцать элементов И, четыре элемента ИЛИ и три элемента НЕ, причем выходы первого, второго, третьего и четвертого ; лементов И соединены с первьи.

вторым, третьим и четвертым входами первого элемента ИЛИ соответственно, выход которого соединен с первым выходом блока, выходы пятого и шестого элементов И соединены с первым и вторым входами второго элемента ИЛИ соответственно, выход которого пбдключен к второму выходу блока, выходы седьмого и восьмого элементов И соединены с первым и вторым входами третьего элемента ИЛИ соответственно выход которого соединен с третьим выходом блока, выход первого элемента НЕ соединен с первым входом четвертого элемента И, первый вход блока подключен через .второй элемент НЕ к первому входу восьмого элемента И, выход девятого элемента И подключен к первому входу седьмого элемента И, второму входу восьмого элемента И и через третий элемент НЕ - к первому входу десятого элемента И, выход которого соединен с четвертым выходом блока, а второй вход - с первым входом блока, второй вход блока подключен к первому ВХОДУ первого элемента И, третий вход блока соединен с первым входом второго элемента И, четвертый вход блока соединен с первым входом одиннадцатого элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с пятым .выходом блока, пятый вход блока соединен с первыми входами третьего и пятого элементов И, шестой вход .бло ка соединен с вторым входом четвертого элементами и первьпл входом шестого элемента И, седьмой вход блока соединен с первым входом двенадцатого элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ, восьмой вход блока соединен с первым входом девятого элемента И, девятый вход блокд соединен с вторыми входами девятого, пятого и шестого элементов И, входом первого элемента НЕ, первым и вторьоу входами элемента ИЛИ-НЕ, выход которого соединен с вторым входом второго элемента И, второй вход третьего элемента И подключен к девятому входу блока, десятый вход блока соединен с третьими входсши второго, третьего, четвертого, пятого, шестого, восьмого и дерятого элементов И .и с вторыми входами первого, седьмого, одиннадцатого и двенадцатого элементов И.

Изобретение относится к вычислите.льной технике и предназначено для использования в цифровых интегрирующих структурах (ЦИС).

Известны цифровые интеграторы, содержащие регис-тр и сумматор прдынтер ральной функции, блок умножения, регистр и сумматор остатка интеграла, выходной блок и предназначенные для использования в цифровых интегрирующих, структурах с фиксированной запятой и одноразрядными приращениями {J

ИЙОсновнйм недостатком указанных цифровых интеграторов является отсутствие контроля за достоверностью их функционирования, что очень важно при использовании цифровых интег-г рирукрих структур в системах управ ления-ответственными процессами.

Наиболее близким по технической сущности к изобретению является цифровой интегратор, содержащий масштабный блок, сумматор подынтегральйой функции, регистр подынтегральной функции, блок умножения,.сумматор остаткд интеграла, регистр остатка интеграла, блок квантования, блок свертки приращения подынтегральной функции, блок свертки подынтёгр альной Функции, блок свёртки остахка интеграла, блок коммутации, сумматор по модулю d, счетчик по модулю d, блок сравнения, причем выход масштабного блока соединен с входом блока свертки приргицения подынтегралной функции, выходы которого соеди- нейы с входом блока коммутации и входом сумматора подынтегральной функции,, второй вход которого соед11гнен с выходом регистра подынтегральной функции, вход которого соединен с выходом блока свертки подынтегральной функции, второй выход которого соединен с входом блока коммутации, первый выход сумматора подынтеграль-т ной функции соединен с входом блоки коммутации7 с входом блока свертки подынтегральной функции и входом блока умножения, а второй выход - р другим входом блока коммутации, вц-: ход блока умножения соединен с входом сумматора остатка интеграла, второй Ьход которого соединен с вы ходом ррегистра остатка интеграла, вход которого соединен с выходом блока свертки остатка интегргша, .второй выход которого соединен с . входом блока коммутации, первый сумматора остатка интеграла cpeiдинен с входом блока коммутации, с входом блока свертки остатка интегргша и с входом блока квантования, второй выход сумматора остатка ин- . теграла соединен с входом блока коммутации, выходы которого, соединены с входом сумматора по модулю d и входом счетчика по модулю d, выход

сумматора по модулю d соединен с входом блока сравнения, второй вход которого соединен с выходом счетчика по модулю d, вход масштабного блока является входом приращения подынтегральной функции цифрового интегратора, второй вход блока умножения является входом приращения переменной интегрирования цифрового интегратора и объединен с входом блока koммyтaции вторым входом суммтора по модулю d, выход блока-квантования является выходом цифрового интегратора, а выход блока сравнени является выходом контроля цифрового интегратора 3j , .

Описанный цифровой интегратор наряду с выполнением операции численного интегрирования обеспечивает оперативный аппаратный контроль за выполнением этой операции, что позволяет использовать его в системах управления ответственными процессами и подвижными объектами.

Основным недостатком данного цифрового интегратора является то, что организация оперативного аппаратног контроля в нем, требует все-таки сранительно больших затрат оборудования, в то же время при использовани цифровых интеграторюв в системах управления подвижными объектами к ним предъявляются жесткие требования не только по надежности, но и по затратам оборудования.

Цель изобретения - сокращение аппаратурных затрат.

Поставленная цель достигается тем что в цифровой интегратор, содержащий масштабный блок, сумматор подынтегральной функции, регистр подынтегргшьной функции, первый элемент задержки, первый элемент ИЛИ, блок умножения, сумматор остатка интеграла, регистр остатка интеграла, второй элемент задержки, второй элемент ИЛИ, блок квантования, первый и второй блоки коммутации, первый счетчик по модулю d, где d - значение модуля, по которому производится контроль, третий элемент задержки и блок сравнения, причем выход переноса сумматора подынтегральной функции соединен через первый элемент задержки с входом переноса сумматора подынтегральной функции, выход суммы которого соединен с первым входом блока умножения и с первым входом nefiBoro элемента ИЛИ, второй вход которого соединен с п.ервым выходом первого блока коммутации, выход регистра подынтегральной функции соединен с выходом первого слагаемого сумматора подынтегральной функции, выход блока умножения соединен с уходом первого слагаемого сумматора остатка интеграла,- выход

переноса которого соединен через второй элемент задержки с входом переноса сумматора остатка интеграла вход второго слагаемого которого соединен с выходом регистра остатка интеграла, а выход суммы соединен с первым входом блока квантования, первый выход которого соеди|нен с первым входом второго элемента ИЛИ, второй вход которого соединен с вторым выходом первого блока коммутации, первый, второй, третий н четвертый входы второго блока коммутации соединены с выходами перено са и суммы сумматора подынтегральной функции и сумматора остатка интеграла соответственно, первый и второй выходы второго блока коммутации соединены с вычитающим и суммируквдим входами первого счетчика по модулю d, первый установочный вход которого соединен с выходом третьего элемента задержки, а выход соединен с первым входом блока сравнения, первый и второй входы масштабного блока соединены соответственно с входом приращении подынтегральной функции цифрового интегратора и входом масштабного сигнала цифрового интегратора, первый, второй и третий входы первого блока коммутации соединены соответственно с входом выбора номера цифрового интегратора, с входом начального значения подынтегральной функции и входом начального значения остатка интеграла цифрового интегратора, второй вход блока умножения, второй установочный вход первого счетчика по модулю d и пятый вход второго блока коммутации соединены с входом приращения переменной интегрирования цифрового интегратора, второй вход блока квантования и шестой вход второго блока коммутации соединены соответственно с входом сигнала выделения остатка цифрового интегратора и входом -стробиручощих сигналов цифрового интегратора, третий вход масштабного блока и входы сброса регистра подынтегральной функции, регистра остатка интеграла первого счетчика по модулю d, трети вход блока квантования соединены с входом сброса цифрового интегратора четвертый вход масштабного блока, четвертый вход блока квантования, .вход третьего элемента задержки и управляющий вход блока сравнения соединены с входом конца итерации цифрового интегратора, второй выход блока квантования подключен к выходу приращения интеграла, а выхо блока сравнения - к выходу контроля цифрового интегратора, введены второй и третий счетчики по модулю d и группа элементов задержки, причем вычитающий и суммирующий входы второго счетчика по модулю d соединены соответственно с третьим и четверты (выходами второго блока коммутации, пятый выход которого подключен к суммирующему входу третьего счетчик по модулю d, входы текущей установки второго и третьего счетчиков по модулю d соединены с выходом третьего элемента задержки, а входы начальной установки этих с.четчиков соединены с входом сброса цифрового интегратора, единичные выходы каждого разряда третьего счетчика помодулю d соединены через элементы задержки с информационными входами второго счетчика по модулю d, вы- ход которого соединен с вторым входом блока сравнения, выход масштабного блока соединен с второго слагаемого сумматора подынтегральной функции и седьмым входом второго блока коммутации, выход первого элемента ИЛИ соединен с информционным входом регистра подынтегралной функции и с восьмым входом ВТОРОГО блока коммутации,, выход второг элемента ИЛИ соединен с информационным входом регистра остатка интеграла и девятым входом второго блока коммутации, выход регистра остатка интеграла также соединен с десятым входом второго блока коммутации.

Кроме того, второй блок коммутации содержит элемент ИЛИ-НЕ, двенадцать элементов И, четыре элемента ИЛИ и три элемента НЕ, причем выходы первого, второго, третьего и четвертого элементов И соединены с первым, вторым, третьим и четвертым входами первого элемента ИЛИ соответственно, выход которого соединен с первым выходом блока, выходы пятого и шестого элементов И соединены с первым и вторым входами второго элемента ИЛИ соответственно, выход которого подключен к второму выходу блока, выходы седьмого и восьмого элементов И соединены с первым и вторым третьего элемента ИЛИ соответственно, выход которого соединен с третьим выходом блока, выход первого элемента НЕ соединен с первым входом четвертого элемента И, первый вход блока подклк чен че-: рез второй элемент НЕ к первому входу восьмого элемента И, выход девятого элемента И подключен к первому входу седьмого элемента И, второму входу восьмого элемента И и через третий элемент НЕ - к перрому входу десятого элемента И, выход которого соединен с четвертым выходом блока, а второй вход - с первым входом блока, второй вход блока подключен к первому входу первого элемента И, третий вход блока соединен с первым входом второго элемента И,. четвертый

вход блока соединен с первым входом одиннадцатого элемента И, выход ко торого соединен с первым входом четвертого элемента ИЛИ, выход кото- рого соединен с пятым выходом блока пятый вход блока Соединен с первыми входами третьего и пятого элементов И, шестой вход блока соединен с вторым входом четвертого элемента И и первым входом шестого элементу И, седьмой вход блока соединен с первым входом двенадцатого элемента И, выход которого соединен с вторь входом четвертого элемента ИЛИ, восьмой вход блока соединен с первь м входом девятого элемента И, девятый вход блока соединен с вторыми входами девятого, пятого и шестогр элементов И, входом первого элемеита НЕ, первым и вторым входами элемента ИЛИ-НЕ, выход которого соединен с вторым входом второго элемеи та И, второй ьход третьего элемента И подключен к девятому входу блока, десятый вход блока соединен с третьими входами второго, третьего, четвертрго, пятого, шестого, восьмого и десятого элементов И и с вторыми таходамя первого, седьмого, одиннадцатого и двенадцатого элементов И.

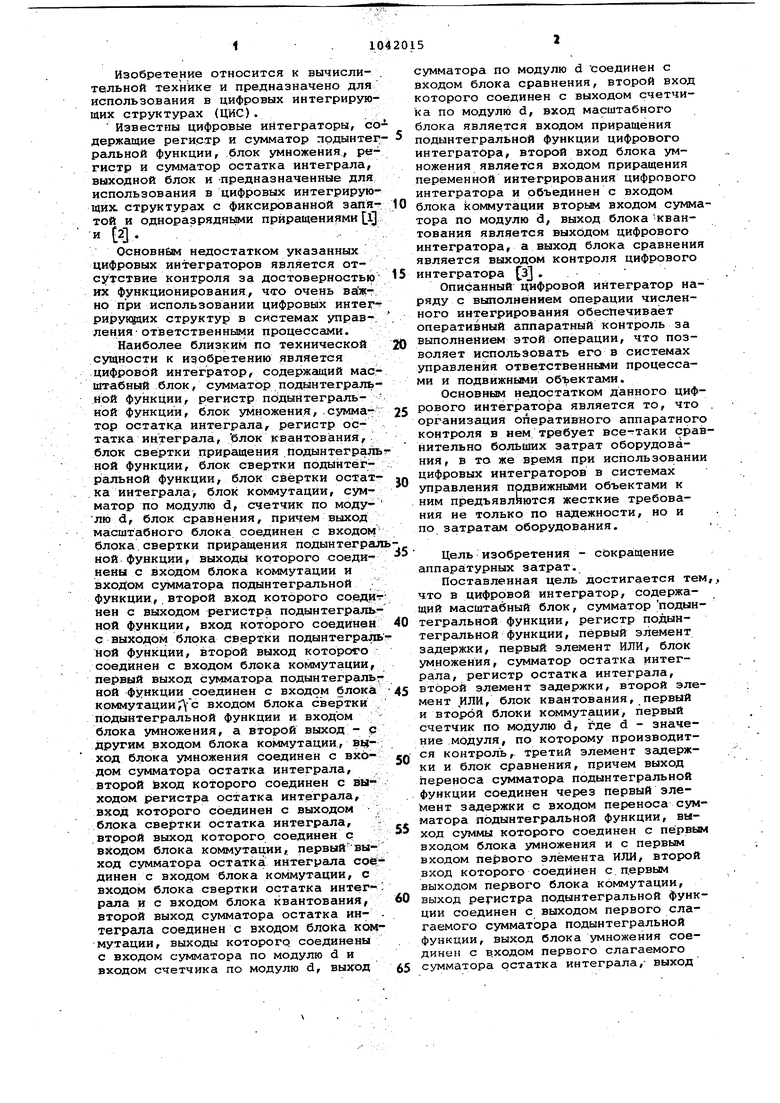

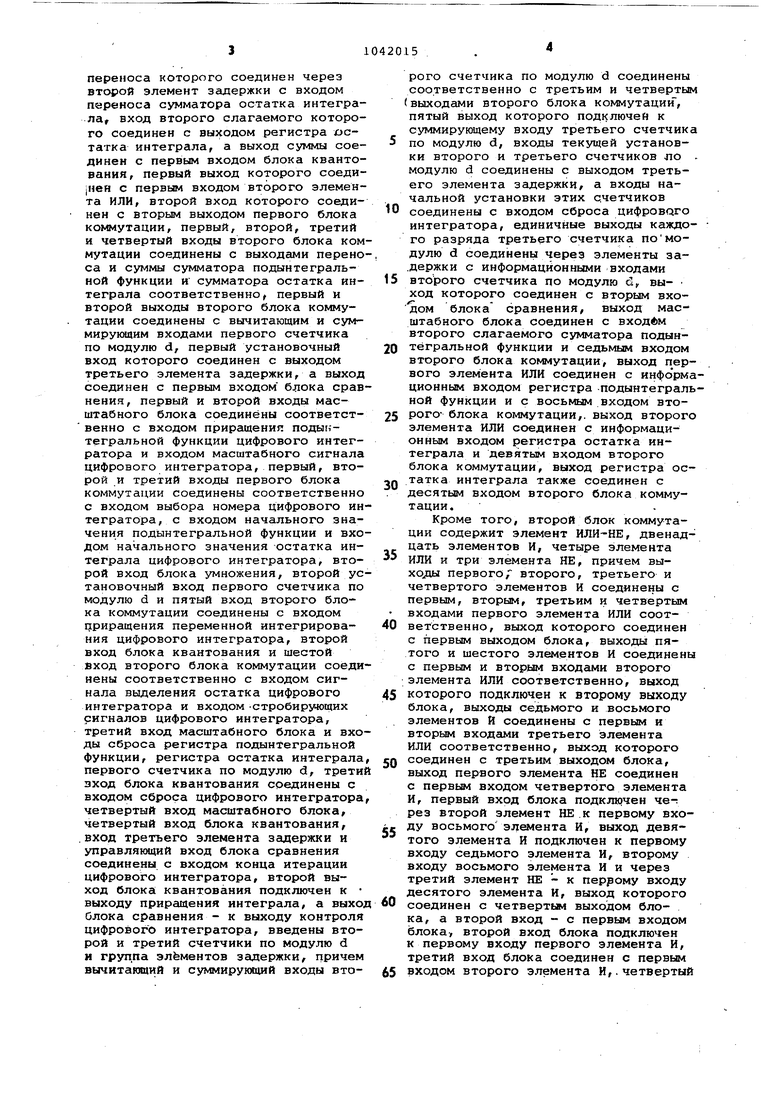

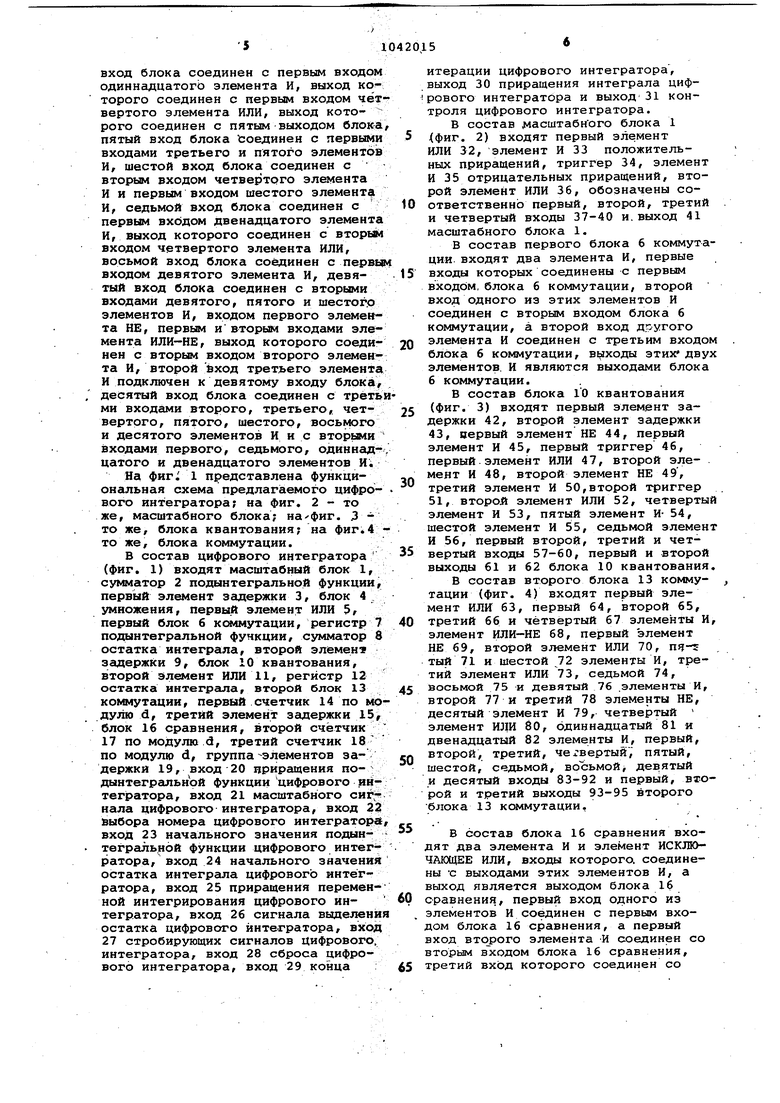

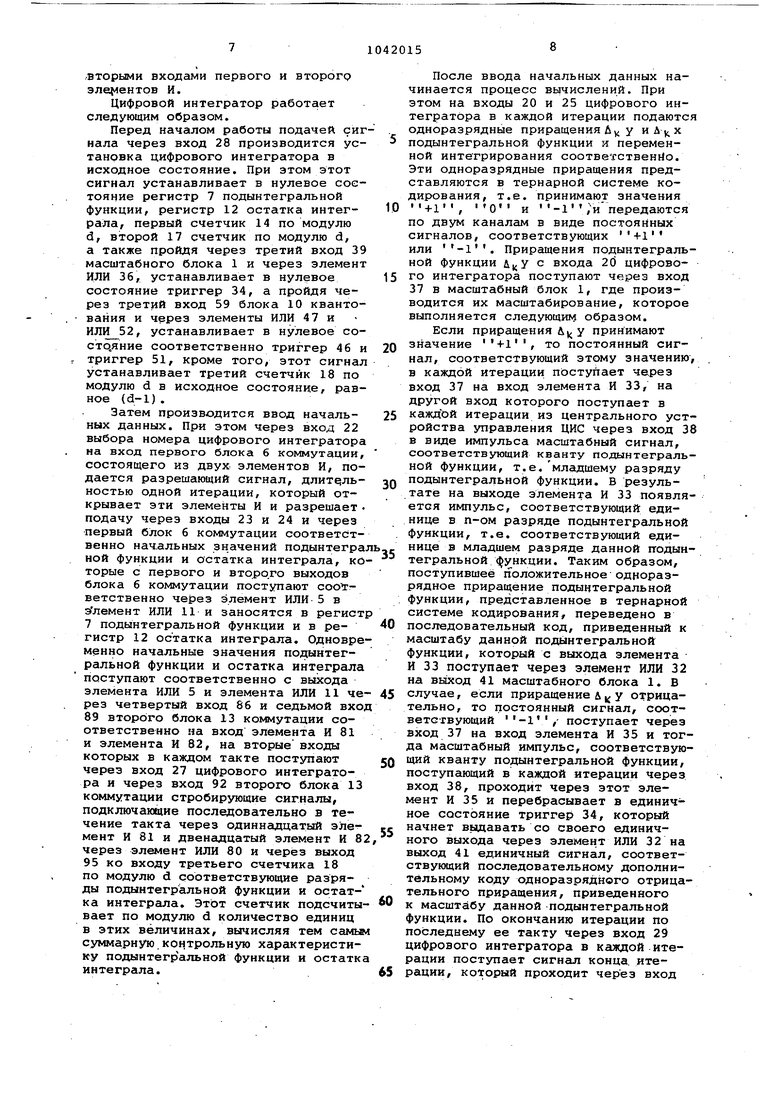

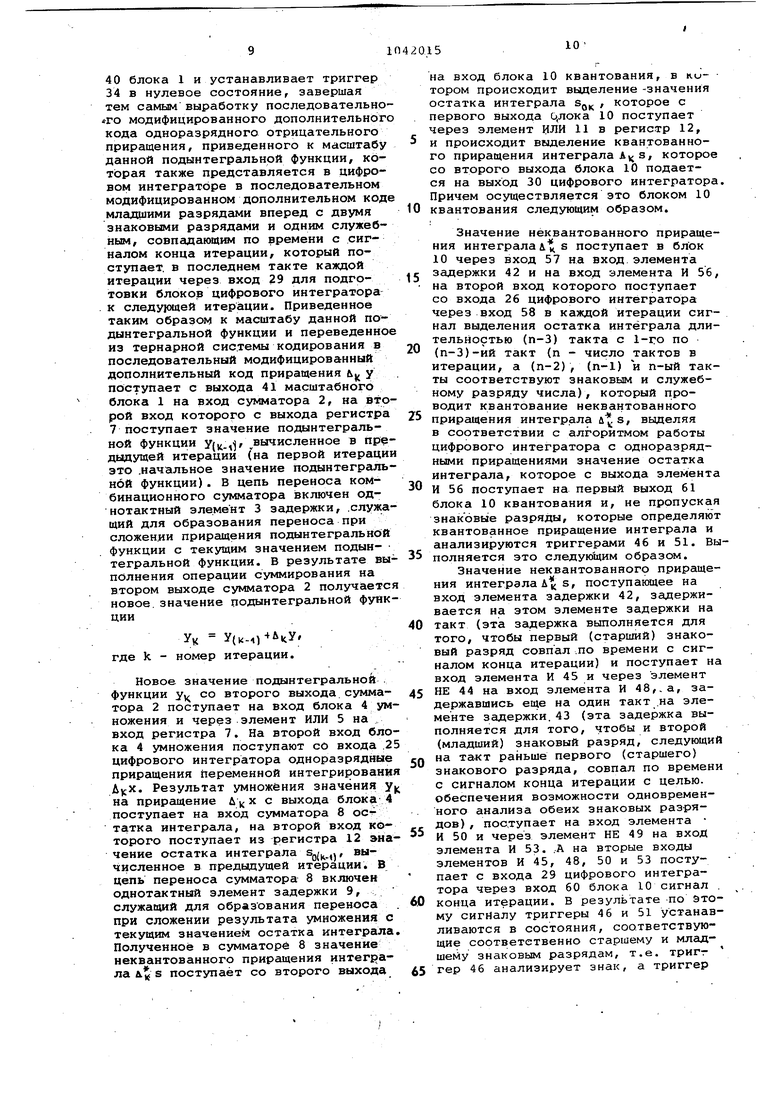

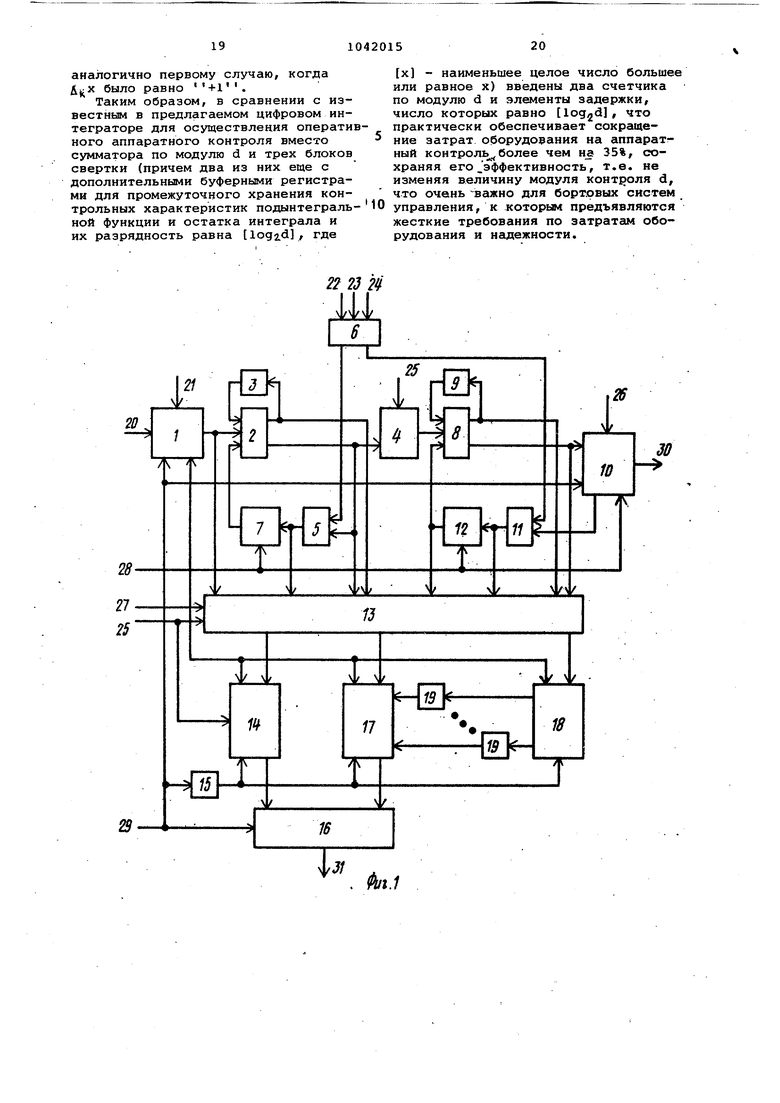

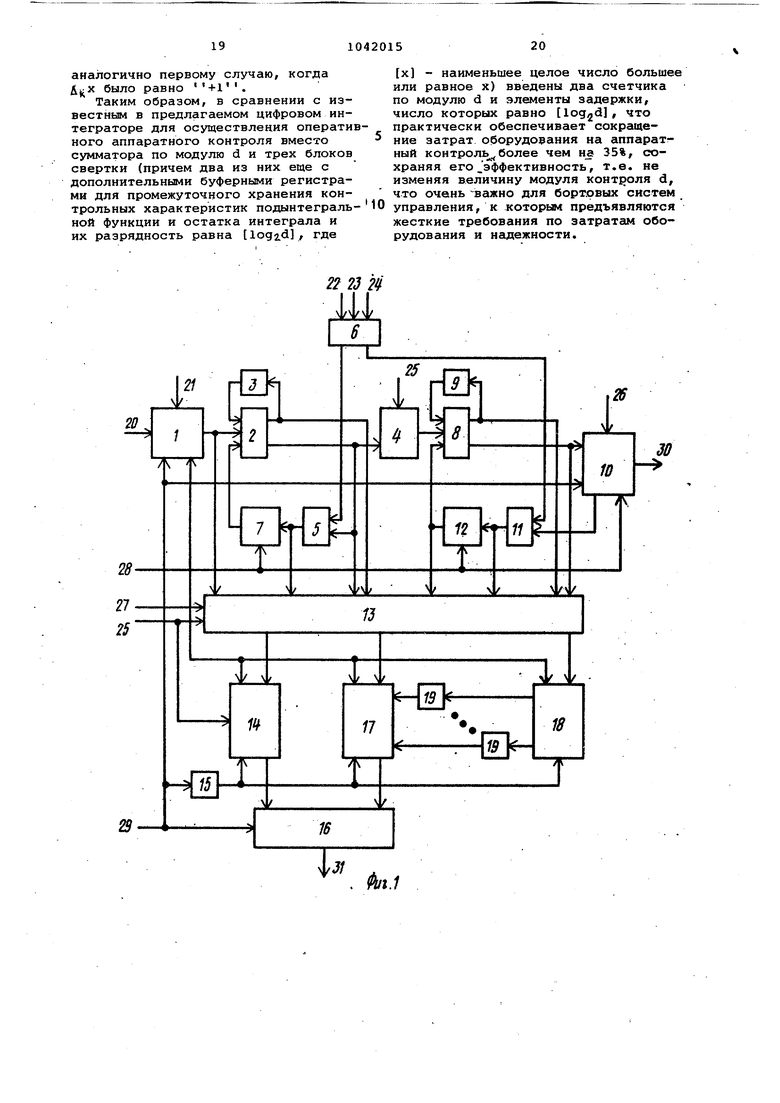

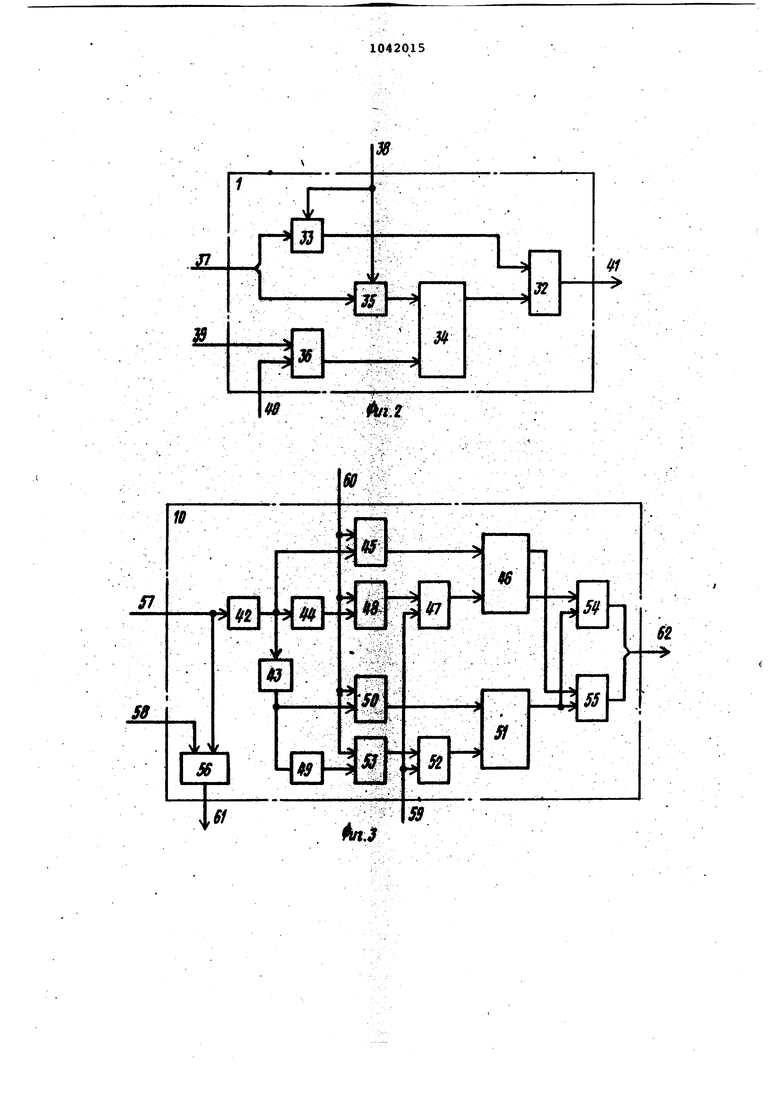

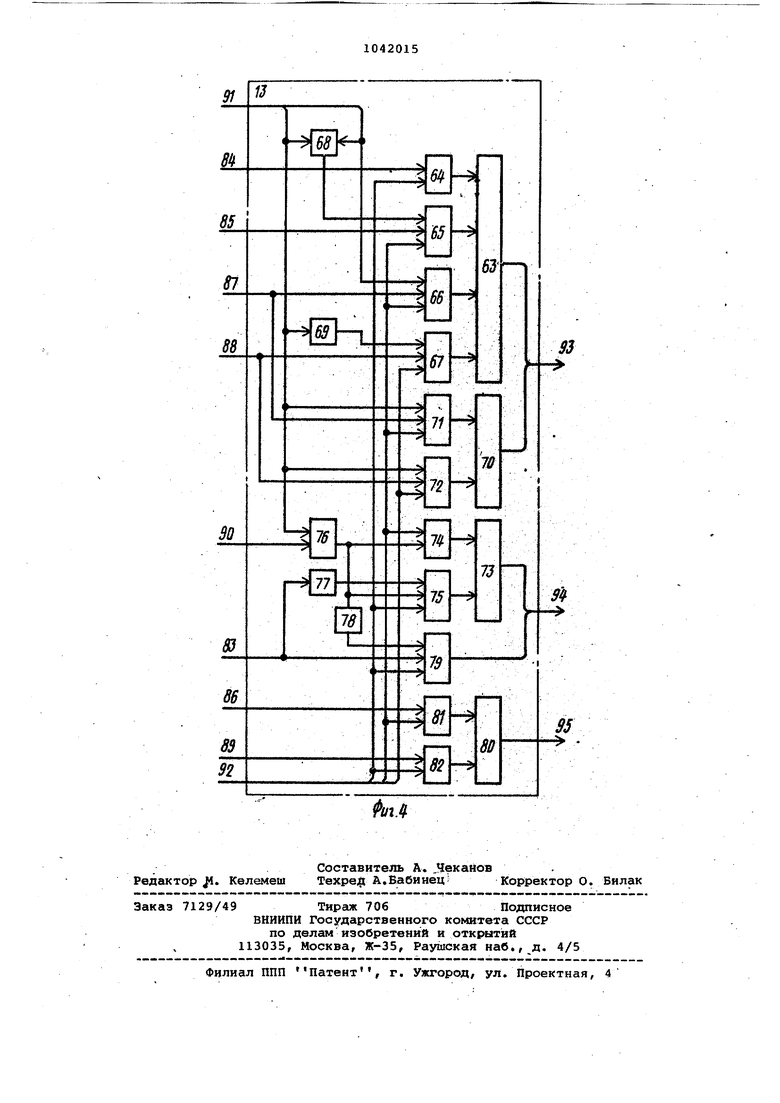

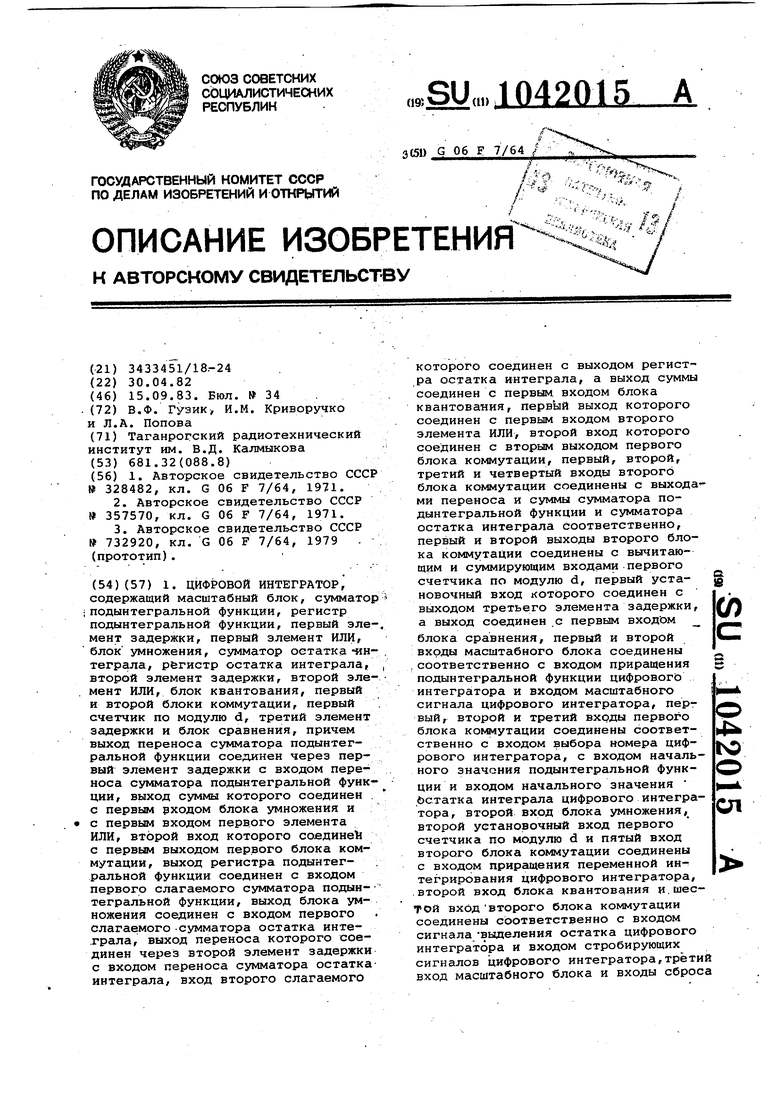

На Фиг 1 представлена функциональная схема пpeдлaгiaeмot o цифрового интегратора; на фиг. 2 - то же, масштабного блока; . 3 то же, блока квантования; на фиг.4 то же, блока коммутации.

В состав цифрового интегратора (фиг. 1) входят масштабный блок 1, сумматор 2 подынтегральной функции, первый элемент згщержки 3, блок 4 умножения, первый элемент ИЛИ 5, первый блок 6 кошутации, регистр 7 подынтегральной функции, сумматор 8 остатка интеграла, второй эл еменг задержки 9, блок 10 квантования, второй элемент ИЛИ 11, регистр 12 остатка интеграла, второй блок 13 коммутации, первый счетчик 14 по модулю d, третий элемент задержки 15 блок 16 сравнения, второй счётчик 17 по модулю d, третий счетчик 18 по модулю d, группа -элементов задержки 19, вход 20 приращения по- дынтегрсшьной функции цифрового интегратора, вход 21 масштабного сигнала цифрового интегратора, вход 22 Ёыбора номера цифрового интеграторам, вход 23 начального значения подын- теграль,н6й функции цифрового ин тегратора, вход 24 начального значения остатка интеграла цифрового интегратора, вход 25 приращения переменной интегрирования цифрового интегратора, вход 26 сигнала выделения остатка цифрового интегратора, вход 27 стробирующих сигналов цифрового, интегратора, вход 28 сброса цифрового интегратора, вход 29 конца

итерации цифрового интегратора, выход 30 приращения интеграла циф рового интегратора и выход-31 контроля цифрового интегратора.

В состав 1асштабного блока 1 фиг. 2) входят первый элемент ИЛИ 32, элемент И 33 положительных приращений, триггер 34, элемент И 35 отрицательных приращений, второй элемент ИЛИ 36, обозначены соответственно первый, второй, третий и четвертый нходы 37-40 и.выход 41 масштабного блока 1.

В состав первого блока 6 коммутации входят два элемента И, первые входы которых соединены с первым входом, блока 6 коммутации/ второй вход одного из этих элементов И соединен с вторым входом блока 6 коммутации, а второй вход другого элемента И соединен с третьим входо блока 6 коммутации, в 1ходы этих дву элементов. И являются выходами блока 6 коммутации.

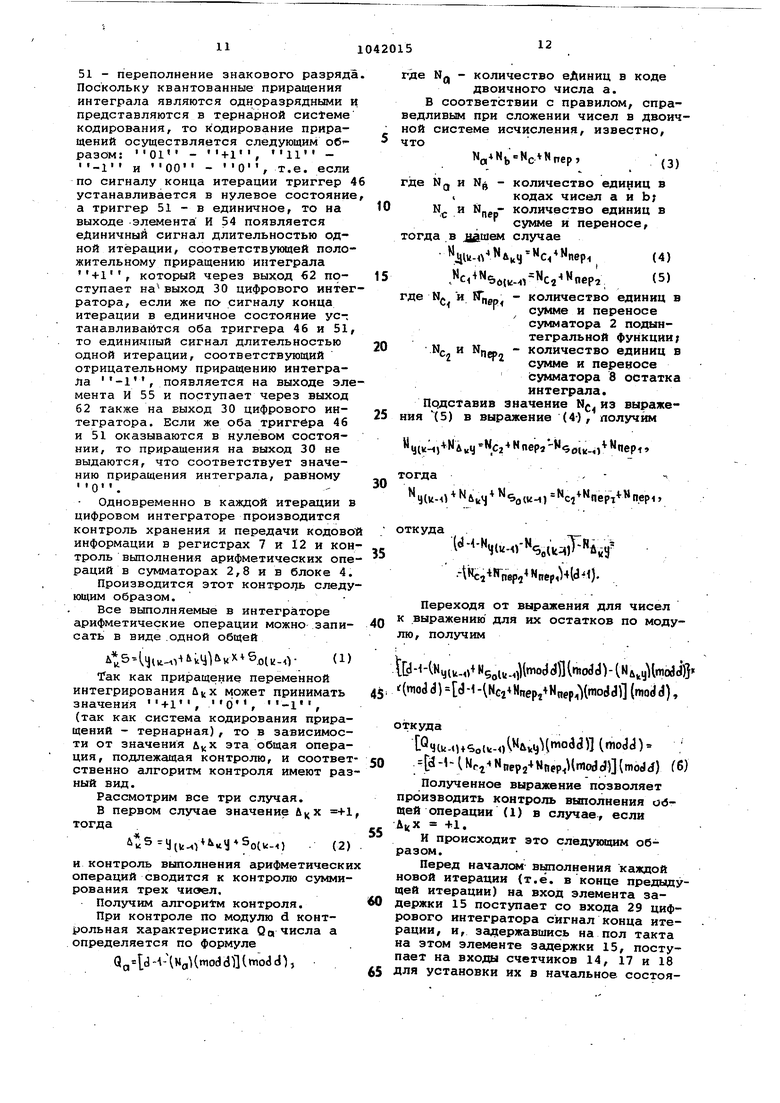

В состав блока 10 квантования (фиг. 3) входят первый элемент задержки 42, второй элемент задержки 43, первый элемент НЕ 44, первый элемент И 45, первый триггер 46, первый элемент ИЛИ 47, второй элемент И 48, второй элемент НЕ 49, третий элемент И 50,второй триггер 51, второй элемент ИЛИ 52, четверты элемент И 53, пятый элемент И- 54, шестой элемент И 55, седьмой элемен И 56, первый второй, третий и четвертый входы 57-60, первый и второй выходы 61 и 62 блока 10 квантования

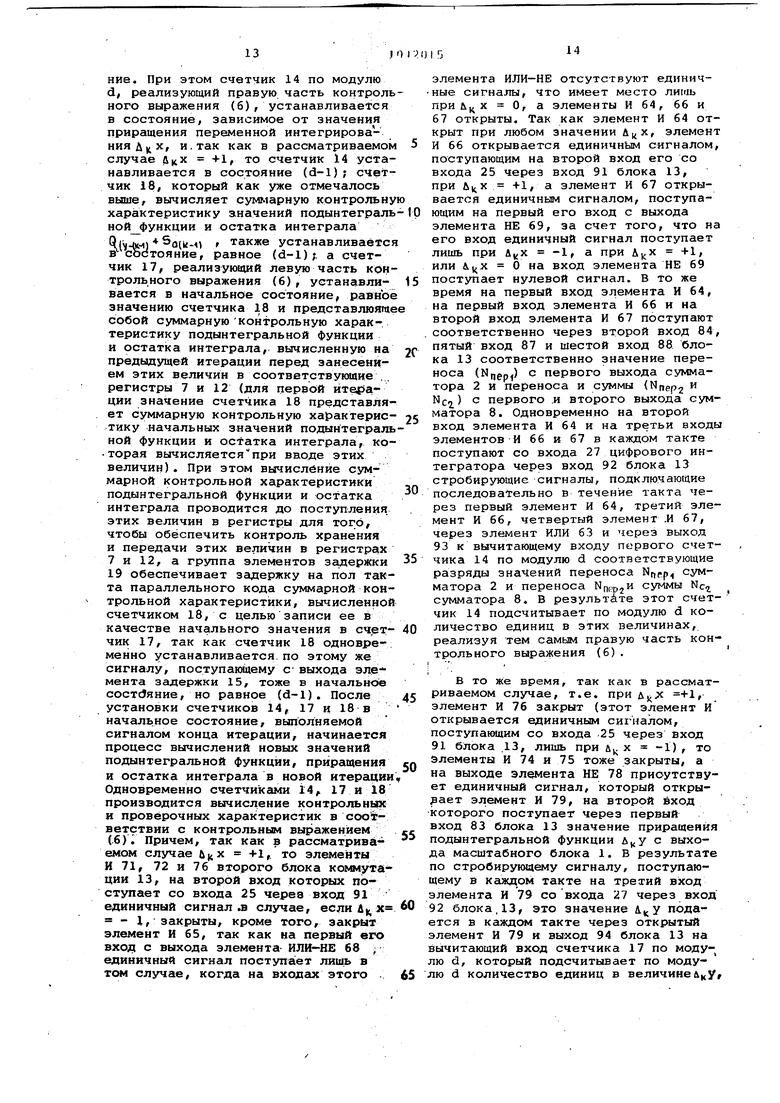

В состав второго блока 13 коммутации (фиг. 4) входят первый элемент ИЛИ 63, первый 64, второй 65, третий 66 и четвертый 67 элементы И элемент ИЛИ-НЕ 68, первый элемент НЕ 69, второй элемент ИЛИ 70, пя-5 тый 71 и шестой 72 элементы И, третий элемент ИЛИ 73, седьмой 74, восьмой 75 и девятый 76 элементы И, второй 77 И третий 78 элементы НЕ, десятый элемент И 79, четвертый элемент ШЩ 80, одиннадцатый 81 и двенадцатый 82 элементы И, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой де:щятый и десятый входы 83-92 и первый, второй и третий выходы 93-95 второго блока 13 коммутации.

В состав блока 16 сравнения входят два элемента И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого, соединены -с выходами этих элементов И, а выход является выходом блока 16 сравнения, первый вход одного из элементов И соединен с первым входом блока 16 сравнения, а первый вход второго элемента -И соединен со вторьам входом блока 16 сравнения, третий вход которого соединен со /вторыми входами первого и второго элеч ентов И, Цифровой интегратор работает следующим образом. Перед началом работы подачей сиг нала через вход 28 производится установка цифрового интегратора в исходное состояние. При этом этот сигнал устанавливает в нулевое состояние регистр 7 подынтегральной функции, регистр 12 остатка интеграла, первый счетчик 14 по модулю d, второй 17 счетчик по модулю d, а также пройдя через третий вход 39 масштабного блока 1 и через элемент ИЛИ 36, устанавливает в нулевое состояние триггер 34, а пройдя через третий вход 59 блока 10 квантования и через элементы ИЛИ 47 и , устанавливает в нулевое состо яние соответственно триггер 46 и триггер 51, кроме того, этот сигнал устанавливает третий счетчик 18 по модулю d в исходное состояние, равное (d-1). Затем производится ввод начальных данных. При этом через вход 22 выбора номера цифрового интегратора на вход первого блока б коммутации, состоящего из двух элементов И, подается разрешающий сигнал, длит льностью ОДНОЙ итерации, который открывает эти элементы И и разрешает подачу через входы 23 н 24 я через первый блок 6 коммутации соответственно начальных значений подынтегра ной функции и остатка интеграла, ко торые с первого и второ.го выходов блока 6 коммутации пост5Гпают соответственно через элемент ИЛИ-5 в элемент ИЛИ 11 и заносятся в регист 7 подынтегральной функции и в регистр 12 остатка интеграла. Одновре менно начальные значения подынтегральной функции и остатка интеграла поступают соответственно с выхода элемента ИЛИ 5 и элемента ИЛИ И че рез четвертый вход 86 и седьмой вхо 89 второго блока 13 коммутации соответственно на вход элемента И 81 и элемента И 82, на вторые входы которых в каждом такте пост5шают через вход 27 цифрового интегратора и через вход 92 второго блока 13 коммутации стробирующие сигналы, подключающие последовательно в течение такта через одиннадцатый элемент И 81 и двенадцатый элемент И 8 через элемент ИЛИ 80 и через выход 95 ко входу третьего счетчика 18 по модулю d соответствующие разряды подынтегральной функции и остатка интеграла. Этот счетчик подсчиты вает по модулю d количество единиц в этих величинах, вычисляя тем самьа суммарную.контрольную характеристику подынтегр альной функции и остатк интеграла. После ввода начальных данных начинается процесс вычислений. При этом на входы 20 и 25 цифрового интегратора в каждой итерации подаются одноразрядные приращения Д у. у и А ц, х подынтегральной функции я переменной интегрирования соответственно. Эти одноразрядные приращения представляются в тернарной системе кодирования, т.е. принимают значения +1, О и ,и передаются по двум каналам в виде постоянных сигналов, соответствующих или . Приращения подынтегральной функции с входа 20 цифрового интегратора поступают через вход 37 в масштабный блок 1, где производится их масштабирование, которое выполняется следующим образом. Если приращения л, у принимают значение , то постоянный сигнал, соответствующий этому значению, в каяодой итерации поступает через вход 37 на вход элемента И 33, на другой вход которого поступает в каждой итерации из центрального устройства управления ЦИС через вход 38 в виде импульса масштабный сигнал, соответствующий кванту подынтегральной функции, т.е.младшему разряду подынтегральной функции. В результате на выходе элемента И 33 появляется импульс, соответствующий единице в п-ом разряде подынтегральной функции, т.е. соответствующий единице в младшем разряде данной подынтегральной функции. Таким образом, поступившее хголожительное одноразрядное приращение подынтегральной функции, представленное в тернарной системе кодирования, переведено в последовательный код, приведенный к масштабу данной подынтегральной функции, который с выхода элемента И 33 поступает через элемент ИЛИ 32 на вьЬсод 41 масштабного блока 1. В случае, если приращение Л | у отрицательно, то постоянный сигнал, соответствующий ,- поступает через вход 37 на вход элемента И 35 и тогда масштабный импульс, соответствующий кванту подынтегральной функции, поступающий в каждой итерации через вход 38, проходит через этот элемент И 35 и перебрасывает в единичное состояние триггер 34, который начнет вьвдавать со своего единичного выхода через элемент ИЛИ 32 на выход 41 единичный сигнал, соответствующий последовательному дополнительному коду одноразрядного отрицательного приращения, приведенного к масштабу данной подынтегральной функции. По окончанию итерации по последнему ее такту через вход 29 цифрового интегратора в каждой итерации поступает сигнал конца, итерации, который проходит через вход 40 блока 1 и устанавливает триггер 34 в нулевое состояние, завершая тем самым выработку последовательно го модифицированного дополнительног кода одноразрядного отрицательного приращения, приведенного к масштабу данной подынтегральной функции, которая также представляется в цифровом интеграторе в последовательном модифицированном дополнительном код млсцциими разрядами вперед с двумя знаковыми разрядами и одним служебным, совпадающим по времени с сигналом конца итерации, который поступает, в последнем такте каждой итерации через вход 29 для подготовки блоков цифрового интегратора к следу 0{цей итерации. Приведенное таким образом к масштабу данной подынтегральной функции и переведенно из тернарной системы кодирования э последовательный модифицированный дополнительный код приращения ь у поступает с выхода 41 масштабного блока 1 на вход сумматора 2, на вто рой вход которого с выхода регистра 7 поступает значение подынтегральной функции у{,,вычисленное в пре дыдущей итерации (на первой итераци это .начальное значение подынтеграль ной функции). В цепь переноса комбинационного сумматора включен однотактный элемент 3 задержки, .служа щий для образования переноса при сложении приращения подынтегральной функции с текущим значением подын- тегральной функции. В результате вы полнения операции суммирования на втором выходе сумматора 2 получаетс новое.значение подынтегральной функ ции УК У(к-ч) где k - номер итерации. Новое значение подынтегральной . функции уц со второго выхода сумматора 2 поступает на вход блока 4 ум ножения и через злемент ИЛИ 5 на вход регистра 7. На второй вход бло ка 4 умножения поступают сО входа .2 цифрового интегратора одноразрядные приращения переменной интегрировани . Результат умножения значения У на приращение Л х с выхода блока 4 поступает на вход сумматора 8 ocf татка интеграла, на второй вход которого поступает из -регистра 12 эна чение остатка интеграла Sg(|., вычисленное в предыдущей итерации. В цепь переноса сумматора 8 включен однотактный элемент задержки 9, служащий для образования переноса при сложении результата умножения с текущим значением остатка интеграла Полученное в сумматоре 8 значение неквантованного приращения интеграла л s поступает со второго выхода на вход блока 10 квантования, в ли- тором происходит выделение -значения остатка интеграла s, которое с первого выхода цлока 10 поступает через элемент ИЛИ 11 в регистр 12, и происходит выделение квантованного приращения интеграла А ( з, которое со второго выхода блока 10 подается на выход 30 цифрового интегратора. Причем осуществляется это блоком 10 квантования следующим образом. Значение неквантованного приращения интеграла л S поступает в блок 10 через вход 57 на вход элемента задержки 42 и на вход элемента И 56, на второй вход которого поступает со входа 26 цифрового интегратора через вход 58 в каждой итерации сигнал выделения остатка интеграла длительностью (п-3) такта с 1-го по (п-З)-ий такт (п - число тактов в итерации, а (п-2), {п-1) и п-ый такты соответствуют знаковым и служебному разряду числа), который проводит квантование неквантованного приращения интеграла л s, выделяя в соответствии с алгоритмом работы цифрового интегратора с одноразрядными приращениями значение остатка интеграла, которое с выхода элемента И 56 поступает на первый выход 61 блока 10 квантования и, не пропуская знаковые разряды, которые определяют квантованное приращение интеграла и анализируются триггерами 46 и 51. Выполняется это следующим образом. Значение неквантованного приращения интеграла А S, поступающее на вход элемента задержки 42, задерживается на этом элементе задержки на такт (эта задержка выполняется для того, чтобы первый (старший) знаковый разряд совпал .по времени с сигналом конца итерации) и поступает на вход элемента И 45 и через элемент НЕ 44 на вход элемента И 48,,а, задержавщись еще на один такт .на элементе задержки. 43 (эта задержка выполняется для того, чтобы и второй (младший) знаковый разряд, следующий на такт раньше первого (старшего) знакового разряда, совпал по времени с сигналом конца итерации с целью. обеспечения возможности одновременного анализа обеих знаковых разрядов) , поступает на вход элемента И 50 и через элемент НЕ 49 на вход элемента И 53. .А на вторые входы элементов И 45, 48, 50 и 53 поступает с входа 29 цифрового интегратора через вход 60 блока 10 сигнал . конца итерации. В результате по этому сигналу триггеры 46 и 51 устанавливаются в состояния, соответствующие соответственно старшему и млгщшеМу знаковым разрядам, т.е. тригг гер 46 анализирует знак, а триггер 51 - переполнение знакового разряд Поскольку квантованные приращения интеграла являются одноразрядными и представляются в тернарной кодирования, то кодирование приращений ос5Ществляется следующим об разом: 01 - +1 , 11 и 00 - О, т.е. если по сигналу конца итерации триггер устанавливается в нулевое состояние а триггер 51 - в единичное, то на выходе элемента И 54 появляется единичный сигнал длительностью одной итерации, соответствующей положительному приращению интеграла 4-1, который через выход €2 поступает на выход 30 цифрового интег ратора, если же по сигналу конца итерации в единичное состояние ус-, танавливайтся оба триггера 46 и 51 то единичный сигнал длительностью одной итерации, соответствующий отрицательному приращению интеграла -1, появляется на выходе эле мента И 55 и поступает через выход 62 также на выход 30 цифрового интегратора. Если же оба триггера 46 и 51 оказываются в нулевом состоянии, то приращения на выход 30 не выдаются, что соответствует значению приращения интеграла, равному О . Одновременно в каждой итерации в цифровом интеграторе производится контроль хранения и передачи кодово информации в регистрах 7 и 12 и кон троль выполнения арифметических опе раций в сумматорах 2,8 и в блоке 4 Производится этот KOHTpojjb следу ющим образом.. Все выполняемые в интеграторе арифметические операции можно записать в виде .одной общей t 4 U-ti- bi4).olu-4V (1) faK как приращение переменной интегрирования ЛцХ может принимать значения +1, О, , (так как система кодирования приращений - тернарная), то в зависимости от значения &,х эта общая операция, подлежащая контролю, и соответ ственно алгоритм контроля имеют раз ный вид. Рассмотрим все три случая. В первом случае значение ЛцХ +1 тогда (.(v-0 и контроль выполнения арифметически операций сводится к контролю суммирования трех чиоел. Получим алгори1гм контроля. При контроле по модулю d контрольная характеристика Qо числа а определяется по формуле ( M-XNgUmod dl3 (mod d), где NQ - количество еЛиниц в коде двоичного числа а. В соответствии с правилом, справедливым при сложении чисел в двоичной системе исчисления, известно, что a b c nepj (3) где NQ и N -количество единиц в кодах чисел а и Ь; NC и N g-количество единиц в сумме и переносе, тогда в лашемслучае J lU-rt4,c4 c/Nnep (4) ,,, (5) где N и ЯПВРЧ количество единиц в сумме и переносе сумматора 2 подынтегральной функции; NC и количество единиц в сумме и переносе Ьумматора 8 остатка интегргша. Пqдctaвив эначеиие выражения (5) в вырс1жемие (4-) / получим 4HcH)NA y«Nc2 + Nnep2-N,,Nnep, тогда, - - , чи-чИ uk эоскч) , откуда i - - i«-o- 5o( ,Тпвр,4Ч„ер,). Переходя от выражения для чисел к выражению для их остатков по модулю, получим .,,.,,)MJ)-tNi,yMtnodd)} M(3)d-1- Ncj4Nne|,+Nnep,Mmodd)l (modd), ткуда Оч1и.«нво{ -4)1«Лу1}Х о 1 (modd) ; . 3 -1- (Мг Nnep2- Jnep,MrtodcJ) (modd) f6) Полученное выражение позволяет производить контроль выполнения общей операции (1) в случае, если АцХ +1, И происходит это следующим образом. Перед началом выполнения каждой новой итерации {т.е. в конце предыдущей итерации) на вход элемента задержки 15 поступает со входа 29 цифрового интегратора сигнал конца итерации, и, задержавшись на пол такта на этом элементе задержки 15, поступает на входы счетчиков 14, 17 и 18 ля установки их в начальное состояние. При этом счетчик 14 по модулю d, реализующий правую часть контрольного выражения (6), устанавливаемся в состояние, зависимое от значения приращения переменной интегрирования , и.так как в рассматриваемом случае +1, то счетчик 14 устанавливается в состояние (d-1); счетчик 18, который как уже отмечалось выше, вычисляет суммарную контрольну характеристику значений подынтеграль ной функции и остатка интеграла

ым) Q(k-ii также устанавливается состояние, равное (d-1);. а счетчик 17, реализующий левую часть контрольного выражения (6), устанавливается в начальное состояние, равнЪё значению счетчика 18 и представлюяте собой суммарнуюконтрольную характеристику подынтегральной функции и остатка интеграла, вычисленную на предыдущей итерации перед занесением этих величин в соответствукидие . . регистры 7 и 12 (для первой ите ации значение счетчика 18 представляет суммарную контрольную ха эактеристику начальных значений подынтегральной функции и остатка интеграла, которая вычисляется при вводе этих величин). При этом вычисление суммарной контрольной характеристики подынтегральной функции и остатка интеграла проводится до поступления, этих величин в регистры для тогО, чтобы обеспечить контроль хранения и передачи этих величин в регистрах 7 и 12, а группа элементов задержки 19 обеспечивает задержку на пол такта параллельного кода суммарной контрольной характеристики, вычисленной счетчиком 18, с целью записи ее в качестве начального значения в сч тчик 17, так как счетчик 18 одновременно устанавливается, по этому же сигналу, поступающему с выхода элемента задержки 15, тоже в начальное состояние, но равное (d-1). После установки счетчиков 14, 17 и 18 в начальное состояние/ выполняемой сигналом конца итерации, начинается процесс вычислений новых значений подынтегральной функции, приращения и остатка интеграла в новой итерации Одновременно счетчиками 14 17 и 18 производится вычис ение контрольных и проверочных характеристик в соответствии с контрольным выражением (6}, Причем, так как в рассматриваемом случае UK +1. то элементы И 71, 72 и 76 второго блока коммутации 13, на второй вход которых поступает со входа 25 через вход 91 единичный сигнал л случае, если Дц х - I, закрыты, кроме того, закрыт элемент И 65, так как на первый его вход с выхода элемента ИЛИ-НЕ 68 , единичный сигнал поступает лишь в том случае, когда на входах этого

элемента ИЛИ-НЕ отсутствуют единичные сигналы, что имеет место ли1«ь при & X О, а элементы И 64, 66 и 67 открыты. Так как элемент И 64 открыт при любом значении , элемент И 66 открывается единичнЬм сигналом, поступающим на второй вход его со входа 25 через вход 91 блока 13, при +1, а элемент И 67 открывается единичным сигналом, поступающим на первый его вход с выхода элемента НЕ 69, за счет того, что на его вход единичный сигнал поступает лишь при -1, а при А,х +1, или &цХ О на вход элемента НЕ 69 поступает нулевой сигнал. В то же время на первый вход элемента И 64, на первый вход элемента И 66 и на второй вход элемента И 67 поступают соответственно через второй вход 84, пятый вход 87 и шестой вход 88 блока 13 соответственно значение переноса (Nnep) с первого выхода сумматора 2 и переноса и суммы (Nnepj NC, ) с первого .и второго выхода сумматора 8. Одновременно на второй вход элемента И 64 и на третьи входы элементов И 66 и 67 в каждом такте поступают со входа 27 цифрового интегратора через вход 92 блока 13 стробирующие сигналы, подключающие последовательно в течение такта через первый элемент И 64, третий элемент И 66, четвертый элемент .И 67, через элемент ИЛИ 63 и через выход 93 к вычитающему входу первого счетчика 14 по модулю d соответствующие разряды значений переноса Nt)pp сумматора 2 и переноса NpppjH суммы NC сумматора 8. В результате этот счетчик 14 подсчитывает по модулю d количество единиц в этих величинах, реализуя тем самым правую часть контрольного выражения (6). I ,

В то Же время, так как в рассматриваемом случае, т.е. при +1, элемент И 76 закрыт (этот элемент И открывается единичным сигналом, поступающим со входа .25 через вход

91блока 13, лишь при х -1) , то Элементы И 74 и 75 тоже закрыты, а на выходе элемента НЕ 78 присутствует единичный сигнал, который открывает элемент И 79, на второй вход которого поступает через первый вход 83 блока 13 значение приращения подынтегральной функции с выхода масштабного блока 1. В результате по стробируимдему сигналу, поступающему в каждом такте на третий вход элемента И 79 со входа 21 через вход

92блока. 13, это значение 4,, у подается в каждом такте через открытый элемент И 79 и выход 94 блока 13 на вычитающий вход счетчика 17 по модулю d, который подсчитывает по модулю d количество единиц в величинел у реализуя тем самым левую конт рольного быражения (6) (суммарная контрольная характеристика значений подынтегральной функции и остатка интеграла Qy(v,-,5 (м) вычисленна на предыдущей итерации, заносится в счетчик 17 в качестве начального зн чения в конце предыдущей итерации) Одновременно счетчик 18 по модулю d ко-входу которого в каждом такте стробирующие сигналы со входа 27 через вход 92 подключают последовательно в течение такта через элемен И 81 и соответственно элемент И 82 соответствующие разряды значения подынтегральной функции и остатка интеграла, подсчитывает суммарную контрольную характеристику подынг тегральной функции и остатка интегт рала (,) для следующей итераци По окончании итерации через вход 29 поступает сигнал конца итерации, который поступает на вход блока сравнения 16 и разрешает сравнение значения счетчика 14, вычисляющего правую часть контрольного выражения (6), со значением счетчика 17/ который вычисляет левую часть контрольного выражения (6). И если значение счетчика 14 не совпада.ет со значением счетчика 17, что свидетел ствует об искажении иофрмации при вычислениях или при хранении и пере даче в регистрах, то блок сравнения 16 выдает на вход 31 контроля сигнал сбоя. Так производится контроль выполне:ния арифметических операций, хранения и передачи информации в цифровом интеграторе в случае, если ЬцХ +1. Во втором случае значение Лц х тогда контролируемая общая операция (1) имеет вид . 4&-(чи.)5(-,) . (Г) t Cu- l+ xylfcon -Sotv-i) где y K-iV+ K У1лоп дополнительный код суммы и . В соответствии с выражением (3) запишем NytiiH Ne,t Nnepi(8) Ь1е,(,.„ N,,ep,., (9) Но образование дополнительного кода в цифровом интеграторе при улножении нового значения подынтеграл ной функции на производится инвертированием значения прдынтегральной функции, с добавлением едини цы в младший разряд при суммировании со значением остатка в сумматора В, тогда с jAon П-NC +1 где п - количество разрядов в регист ре подынтегральной функции. Подставим значение lNc исходное выражение (9) получим n-N,-,4 If Nc Nc,-b N, Ci во(Ч) . В получившееся выражение подставим значение N из выражения .(8), тогда - .j-Nь,,.,, откуда .. ((K-()r i«tj 2 So{K-1) Nc i-Nnep,2-Mnepi- l J-n-2). Переходя от выражения для чисел к выражению для их остатков по модулю, получаем - iW- 4NyOi.)HmodV)(moda) + 4,,.,Umodd(™odd)tU-h-2V lmod))(,-Nnep)(dl(mo(Jd), ; откуда lQ4U:o 5oi,.,,4-N4,,,,,,(№o,}(})() t(d-n-2)(niodd) ч (Nc tNflep,-Nnep,) MdUMJ). Получившееся. выра.жение позволяет производить контроль вьтолнения общей операции (1) в случае, если I. Контроль достоверности.функционирования цифрового интегратора в этом случае производится так же, как и. в первом случае, когдал х +1, за тем исключением, что счетчик 14 устанавливается в исходное состояние, равное (d-п-2)(mod d), и стробирующие сигналы в каждом такте подключают последовательно. В течение такта к вычитающему входу этого счетчика соответствующий разряд значения переноса , сумматора 2 через элементы И 64 и ИЛИ 63 к суммирующему входу этого счетчика соответствующие разряды значений переноса суммы Ыс2 сумматора 8 через элементы И 71 и 72, открытые единичным сигналом со входа 91 (через этот вход в блок 13 поступает приращениеЛ х, равное в рассматриваемом случае ), и через элемент ИЛИ 70, а элементы И 65,. 66 и 67 закрыты, так как элемент И 65 открывается единичным сигналом с. выхода элемента ИЛИ-НЕ 68 лишь при &к X О, элемент И 66 открывается единичным сигналом со хода 91 лишь при &)( X +, элемент И 67 открывается .единичмьпл сигналом с выхода элемента НЕ 69 приАкХ +1 ИЛИ ЛкХ 0, а в рассматриваемом случае -1 и на вход этого элемента НЕ 69 поступает единичный сигнал. Кроме того, единичный сигнал со входа 91 открывает элемент И 76, на другой -вход которого через вход 90 поступает значение SQ..), и в отличии от первого случая, когда ЬцХ +1, счетчик 17 подсчитывает п модулю d количество единиц не только в приращении подынтегральной функции ЬкУ (как это было которое поступает в блок 13 через вход 83, но и в остатке интеграла 6(-1) которое поступает через вход 90 и «ереэ открытый элемент И 76,. реализуя тем самым выражение (2Soi.,.(mod d) , причем реализация Ьазности 28д,.-ЛцУ производитс в каждом такте с помощью элементов И 74, 75, 79 и элементов НЕ 77 и 7 При этом, если в i-том такте 1-Ы разряд остатка интеграла sj.x равен, нулю, а i-ый разряд приращения в1кУ равен единице, то на первых входах элемента НЕ 78 присутствует единичный сигнал, который открывает элемент И 79 и стробирующий сигнал со входа 92 пропускает в i-том единицу 1-го разряда приращения на вычитающий вход рчетчикаД7, реализуя выражение. 2 . sj..pu. 2 « О -1 -1; если же в 1-том так те, в 1-том разряде в. i-том разряде л 1 у будетединица, то на выходе элемента НЕ 78 присутствует нулевой сигнал, который закрывает элемент И 79, и на выходе элемента НЕ 77 - нулевой сйгнгш, который закрывает, элемент И 75, а на первый вход элемента И 74 поступает с выхода элемента И 76 единичный сигнал и стробирующий сигнал со входа 92 Пропускает в i-том такте эту единиц на суммирующий вход сч ргчика 17,, реализуя выражение ., 21-1 +1; если же в i-том такте в i-TOM разряде Sg(,.,j единица, а в i-TOM разряде л у нуль, то на выход элемента НЕ 78 появляется нулевой сигнал, который закрывает элемент И 79, а на выходе элемента НЕ 77 появится единичный сигнал, который открывает элемент И 75. Так как на первые входы элементов И 74 и 75 поступает единичный сйгнгш с выхода элемента И 76 (так как и i-тый разряд , равен единице), то стробирующие сигналы -со входа 92 в i-OM такте пропускают последовательно две единицы соответственно через элемент И 75 и элемент И 74, через элемент ИЛИ 73 и через выход 94 на суммирующий вход счетчика 17„ реализуя выражение 2sJ,.)-д у 2а- О - +2; если же в i-том такте в i-тых разрядах величин Sgj.i и Лц у нули, то на вхОд счетчика 17 в i-то такте ничего не поступает. Во всем же остальном контроль достоверности функционирования цифрового иитегратора при -1 проводится аиалргично первому случгио, когда ЛцХ бало равно +1 В третьем случае д,х О, тогда контролируемая операция (1) распадается на две операции: а)вычисление нового значения подынтегральной функции УК Угк-л- - «:У б)передача информации в регистр 12 остатка интеграла ок o(k.O В соответствии с выражением (3) записываем Nirtt-o- NM Мс,+Ы„,р,. VKM, Объединим эти два равенства, тогда , ч(, ld-i-N l,.,,,.,,-N4 -(VNnep c2VWM). Переходя от выражения для чисел к выражению для их остатков по модуЛю; -получаем d-1-iN(,UH)%(KM)()lmo Jdll ((i-1-(,tNc2)(modd)(), откуда Wyi«HUSoU-n-lN,(T.) - (i4-(Nc,nepi caU odd){wod(J). Полученное выражение позволяет производить контроль выполнения общей операции (1) в случае, если Дц X О. Контроль за достоверностью функционирования интегратора в этом случае производится тал же, как-и в первом случае (когда А х +1), за тем исключением, что в каждом такте к вычитающему входу счетчика 14 вместо значений N|,ep2, Nc и Nnepiблок 13 подключает значения N, т.е. приЛцХ О вместо значения переноса Vtnep с первого выхода GS MMaTOpa 8, подаваемого через элемент И 66 при &кХ +1, подается в каждом такте тем же стробирующим сигналом значение N со второго выхода сумматора 2 через вход 85 и через элемент И 65, открытый единичным сигналом с выхода элемента ИЛИ-НЕ 68, на входы которого при Лц х О поступают нулевые сигналы (единичные сигналы поступают.на входы элемента ИЛИ-НЕ 68 лишь при АцХ +1 или -1). Во всеи же остальном контроль за достоверностью функционирования при & X О проводится

аналогично первому случаю, когда Д..Х было равно .

Таким образом, в сравнении с известным в предлагаемом цифровом интеграторе для осуществления оперативного аппаратного контроля вместо сумматора по модулю d и трех блоков свертки (причем два из них еще с дополнительными буферными регистрами для промежуточного хранения контрольных характеристик подынтегральной функции и остатка интеграла и их разрядность равна logid, где

х1 - наименьшее целое число большее или равное х) введены два счетчика по модулю d и элементы задержки, число которых равно , что практически обеспечивает сокргицение затрат оборудования на аппаратный контроль.более чем HJ 35%, сохраняя его эффективность, т.е. на изменяя величину модуля контроля d, что очень важно для бортовых систем управления, к которым предъявляются жесткие требования по затратам оборудования и надежности.

й

Г 32

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| Цифровой интегратор | 1985 |

|

SU1365081A1 |

I. ЦИФРОВОЙ ИНТЕГРАТОР содержащий масштабный блок, сумматор подынтегральной функции, регистр подынтегральной функции, первый эле-, мент задержки, первый элемент ИЛИ, блок умножения, сумматор остатка -«нтеграла, регистр остатка интеграла, , второй элемент задержки, второй элемент ИЛИ, блок квантования, первый и второй блоки коммутации, первый счетчик по модулю d, третий элемент задержки и блок сравнения, причем выход переноса сумматора подынтегральной функции соединен через первый элемент задержки с входом переноса сумматора подынтегральной функции, выход суммы которого соединен . с первым уходом блока умножения и с первым входом первого элемента ИЛИ, второй вход которого соединеТй с первым выходом первого блока коммутации, выход регистра подынтегральной функции соединен с входом первого слагаемого сумматора подынтегральной функции, выход блока умножения соединен с входом первого слагаемого сумматора остатка инте.грала, выход переноса которого соединен через второй элемент задержки с входом переноса сумматора остаткаинтеграла, вход второго слагаемого которого соединен с выходом регистра остатка интеграла, а выход суммы соединен с первым входом блока квантования, первый выход которого соединен с первым входом второго Элемента ИЛИ, второй вход которого соединен с вторым выходом первого блока коммутации, первый, второй, третий и четвертый входы второго блока коммутации соединены с выходами переноса и суммы сумматора подынтегральной функции и сумматора остатка интеграла соответственно, первый и второй выходы второго блока коммутации соединены с вычитающим и суммирующим входами.первого i счетчика по модулю d, первый установочный вход которого соединен с (Л выходом третьего элемента задержки, а выход соединен .с первым входом блока сравнения, первый и второй входы масштабного блока соединены ,соответственно с входом приращения подынтегральной функции цифрового интегратора и входом масштабного сигнала цифрового интегратора, первый, второй и третий входы первого 4 to блока коь« утации соединены соответственно с входом выбора номера цифрового интегратора, с входом начального значения подынтегральной функции и входом начального значения Ьстатка интеграла цифрового интеграел тора, второй вход блока умножения, второй установочный вход первого счетчика по модулю d и пятый вход второго блока коммутации соединены с входом приращения переменной интегрирования цифрового интегратора, .второй вход блока квантования и.шестой входвторого блока коммутации соединены соответственно с входом сигнала выделения остатка цифрового интегратора и входом стробирующих сигналов цифрового интегратора,третий вход масштабного блока и входы сброса

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 0 |

|

SU328482A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (прототип). | |||

Авторы

Даты

1983-09-15—Публикация

1982-04-30—Подача