Изобретение относится к области автоматизированных систем для контроля и может быть использовано при контроле больших интегральных схем (БИС) и сверхбольших интегральных схем (СБИС). Известны устройства для контроля электрических параметров электронных схем 1.и 2, содержащие , коммутационную матрицу, источники тока и напряжения, измерительный блок, блок управления и индикации, блок согласования, в которых в соответствии с программой контроля, поступающей из управляюще .вычислительной машины УВМ, при помо щи коммутационной матрицы к соответ ствующим выводам контролируемой электронной cxeNbi подключаются, программные ист пякк напряжения, тока и измерительный блок. В результа те контроля формируются команды Годен, Не годен в зависимос ти от того, находится параметр в требуемых пределах или выходит из них. Недостаткалда таких устройств является жесткость программ контроля, большое число управляющих команд и низкая оперативность контроля интегральных схем. Наиболее близким техническим решением к изобретению является система контроля параметров интехральных схем, содержащая УВМ, первый выход которой соединен с первым входом блока памяти, второй выход - с первым входом счетчика аддаеса памяти, третий выход - с первым входом первого блока совпадения, четвертый выход через регистр выходных тестовых комбинаций - с Первым входом многоканального амплитудного дискриминатора и пятый выход через регистр тестовых комбинаций - с первым входом блока сравнения, второй вход которого соединен с первым выходом счетчика адреса памяти, а выход - с первым входом УВМ,одним входомвторого блока совпадений и вторьда входом многоканального амплитудного дискриминатора, выход которого подключен ко второму входу УВМ, и генератор тактовых импульсов, соединенный .через последовательно включенные второй блок совпадения и счетчик числа повторений тестовых комбинаций с третьим входом УВМ, вторым

входом счетчика адреса памяти, вторым входом блока памяти и вторым входом первого блока совпадения,третий вход которого соединен с выходом блока п.амяти, а выход - с другим входом счетчика числа повторений тестовых комбинаций 3.

В процессе производства схем бывает необходимо изменение очередности контроля параметров схем изза изменения соотношений между удельными весами параметров, по которым схе№1 оказываются негодными (в результате возможных изменений условий технологического цикла при производстве очередной партии и В11утри зтого цикла) . : „.«,.... Чтобы уменьшить потери времени При контроле негодных схем очередность контроля параметров схем должна быть такой, что в первую очередь должны контролироваться те параметры, по которым схегФ чаще всего оказываются негодными. Применение изЪестной системы автоматического контроля больших интегральных схем при крупносерийном производстве их оказывается малозффективным из-за того,

wo данная система производит коН троль пар ййётр6в инт егралШШ : схеМ и в очерёдности, которая соответствует очередности опроса счетчиком адреса памяти ячеек ЗУ и не может изме ййтЪея Вп6)оцессе контроля.

Целью изобретения является повышение быстродействия системы.

Эта цель достигается тем, что. В предложенную систему введены дешифtJaidp кода очерёднЪстй, блок-сче чйкбв тёстовйГх кб1м6инаций H KSStoytaTop тестошлх комбинаций, первый вход

кЬтЪрого с-оединен с выходом много1Га айьЙ€Ш й ДИскриминатора, выход через блок счётчиков тёстоЪых комбинаций - с четвёртым входЬм и шестым йыходЬм УВМ, а вход - со вторым выходом УВМ и первым входом дешифра тора кода очередности, второй вход которого подклю Чей кб Btdpot вЫ5ГОду счётчи ка адреса.памяти, а; выход - к третьему входу блока памяти,

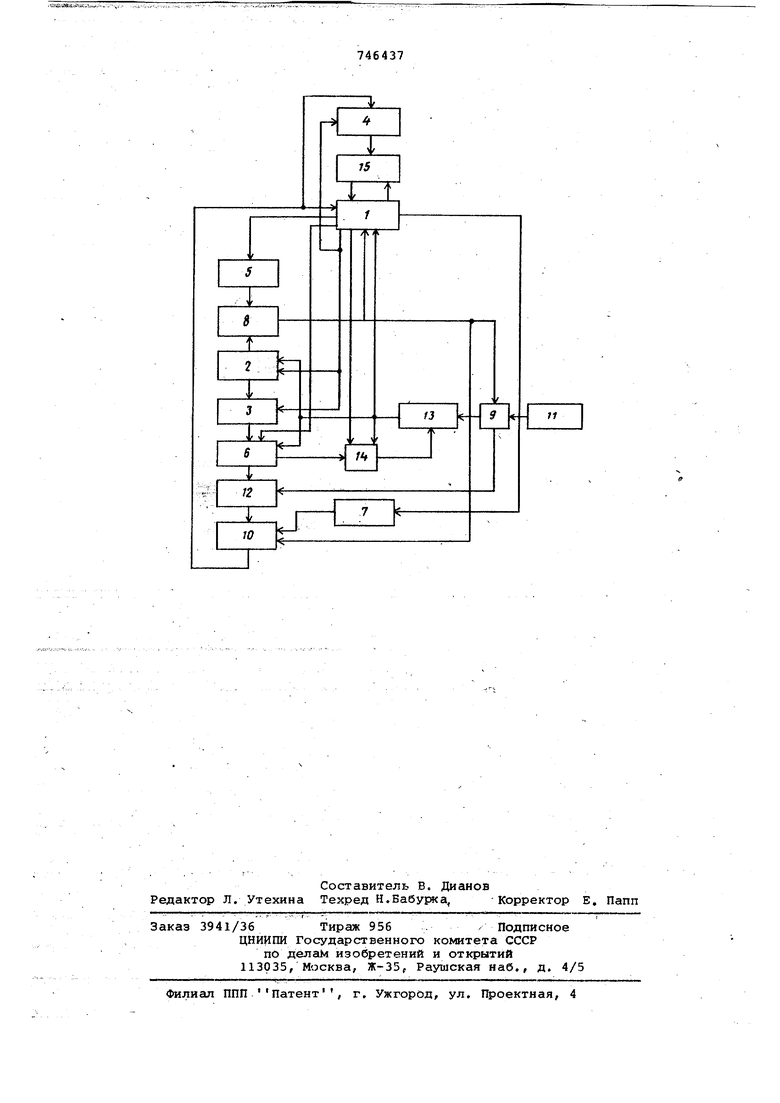

На « ёрТёЖё показана струТстурная

схема систекы.

Выходы УВМ 1 соединены со входаМИ счетчика адреса памяти 2, дешифратрра кода очередности 3, коммутатора тестовых кЬмёйнаций Т, рёгастра адреса тесто.вых комбинаций 5,блока памяти 6 и регистра выходных тестовых комбинаций 7 Входы блока сравнения 8 сЬ Дйнёкг&; с выходаШ регистра 5 и счетчика2, а выход с входами второго блока совпадения 9, fNfii61 6KeHaWb j 6 амплитудного дискригФснато а 1 0и $1вЙ 1. lf{p вход блока йЪёДйнёй и выходом генёратора тактовых импульсов И, )ДЫ - с контролируемой большой интегральной схемой 12 и счетным входом счетчика числа повторений тестовых комбинаций 13, Входы первого блока совпадений 14 соединены с выходами блока 6, УЕМ 1, счетчика 13 и входами счетчика 2, УВМ i и блока 6. Выход блока б соединен со схемой 12, Входы дискриминатора 10 соеДЙненй с выходами схемл 12 и регистра 7, а выход - с входами УВМ 1 и коммутатора 4. Счетный вход блока 15 счетчиков тестовых комбинащий соединен с выходом коммутатора 4,вход опроса и выход - с УВМ 1.Выход счетчика 2 соединен с дешифратором 3,а выход последнего - со входом блока 6.

Работа системы начинается с того, что по команде с УВМ 1 опрашиваются счетчики в блоке 15 и значения кодов записанных в них, переписываются в УВМ 1, которая по программе, заложенной в ней, по результатам опроса формирует команды очередности, поступающие на дешифратор 3 тайим образом, что первой поступает команда, соответствующая наибольшему коду, поступавшему из определенного счетчика блока 15, затем - команда соответствующая, меньшему по величине кеду и так в порядке убывания величины кодов до наименьшего (иначе УВМ 1 формирует команды очередности в соответствии с величиной кодов счетчиков в блоке 15 в порядке их убывания) . ЕСЛИ коды ряда счетчик ов или всех равны, то команды очередности формируются в определенной последовательности, определяемой программой, заложенной в УВМ 1.

УВМ 1 передает в счетчик 2 начальный адресномера последовательности тестовых комбинаций. В то же время на вход дешифратора 3 и коммутатора 4 из УВМ 1 поступает код очёрёднЬйтй, соответствующей той тестовой комбинации, которая должна контролировать схему первой. На выходе дешифратора 3 появится разрешение на считывание той ячейки блока б, в которой хранится тестовая комбинация входных воздействий, соответствующая коду очередности,поступившему из УВМ 1 на дешифратор 3, Коммутатор 4 подключает выход дискриминатора 10 к счетному входу того счетчика из блока 15, который соответствует проверяемой тестовой комбйнйции.Ъ регистр 5 записывается адрес номера тестовой комбинации на которой требуется зафиксировать выходные сигналы контролируемой схемы, В регистр 7 из блока памяти выйЬйныХ ®ётЬвых комбинаций, входящего в состав УВМ 1, поступает выходная тестовая комбингщия, соответствующая выходным сигналам схема 12 на указанном в регистре 5 номере тестовой комбинации.

На блок 6 из УВМ 1 поступает импульс запроса. В каждой ячейке блока 6 выделен ряд разрядов, и в последних записывается число циклов генератора 11, в течение которых на проверяемую схему должна подава- гГ я данная тестовая комбинация входных:„ воздействий. При считывании я чёйки блока 6 на входы схемы 12 подаются входные воздействия, а число циклов, в течение которых данные воздействия должнй подаваться на схему 12, переписывается в обратном коде в счетчик 13 через блок 14. На счетный вход счетчика 13 подаются импульол с генератора 11 через блок 9.

При заполнении счетчика 13 наращивается на содержимое счетчика 2 , и подается на УВМ 1 команда на смену кода очередности, поступающего на дешифратор 3. 3запрашивается блок 6 по следующему адресу, соответствующему коду очередности,формируемому УВМ 1, и открывается блок 14 для записи в счетчик 13 следующей тестовой комбинации. На требуемом номере цикла (при равенстве адресов в счетчике 2 и регистре 5) блок 8 запрещает про сождение тактовых импульсов на счетчик 13, закрырая блок 9, и подает стробирующий импульс на дискриминатор 10.

Если в ходе контроля интегральной схемы по какой-нибудь тестовой комбинации дискриминатор 10 .определит несоответствие выходных сигналов схемы 12 и выходных тестовых комбинаций регистра 7, он формирует импульс который через коммутатор 4 поступит на счетный вход того счетчика из блока 15, который соответствует данной контролируемой комбинации, и в нем код увеличится на .

Затем система переходит к контролю следующей интегральной схемы. Если импульс из дискриминатора 10 не поступает, контролируется следующий параметр схемы. Если все параметры cxeNSJ проходят контроль успешно, система переходит к контролю следующей схемл.

Таким образом, в процессе контроля интегральных схем в счетчиках блока 15 накапливается информация в виде кодов, записанных в них, о том, по каким параметрам схемы чаще всего оказываются негодными и УВМ 1, обрабатывая эту информацию, формирует код очередности контроля параметров интегральных схем. Если хотя бы один из счетчиков блока 15 полностью заполнится, все счетчики сбрасываются в нулевое состояние.

Использование данной системы для автоматического контроля больших интегральных схем позволит в 2-3 раза увеличить производительность операций контроля при крупносерийном

производстве интегральных схем и получить на заводах отрасли экономический эффект не менее 300 тыс.руб. в год.

Формула изобретения

Система контроля параметров интегральных схем, содержащая управляющую вычислительную машину, (УВМ), первый выход которой соединен с первым входом блока памяти, второй выход - с первым входом счетчика адреса памяти, третий выход - с первым входом первого блока совпадения,чет5вертый выход через регистр выходных тестовых комбинаций - с первым йхо|дом многоканального амплитудного дискриминатора и пятый выход через регистр адреса тестовых комбинаций 0с первым входом блока сравнения,второй вход которого соединен .с первым выходом счетчика адреса памяти, а выход - с первым входом УВМ,(одним входом второго блока совпадений и

5 вторым входом многоканального гмплигрудного дискриминатора,выходкоторого подключен ко второму входу УВМ и генератор тактовИх импульсов, соединенный через последовательнр включенные второй блок совпадений И

0 счетчик числа повторений тестовых комбинаций с третьим входом УВМ,вторым входом счетчика адреса памяти, вторым входом блока памяти и вторым входом первого блока совпадения,тре5тий вход которого соединен с выходом блока памяти, а выход -. с другим входом счетчика числа повторений тестовых комбинаций, о т л и чающаяся тем, что, с целью шения быстродействия системы, в и.ее введены дешифратор кода очередности блок счетчиков тестовых, комбинаций и коммутатор тестовых комбинаций, первый вход которого соединен с вы5ходом многоканального амплитудного дискриминатора, выходчерез блок счетчиковтестовых комбинаций - с .четвертым входом и шестым выходом / УВМ, а второй вход - со вторым вы0ходом УВМ и первым входом дешифратора кода очередности, второй вход которого подключен ко второму выходу счетчика адреса памяти/, а выход к Третьему входу блока-памяти.

5

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР :в , кл. & 01 R 31/28, 1970. .

0

2,Авторское свидетельство СССР t 416700, кл. G Об F 15/46, 1972.

3,Авторское свидетельство СССР № 377738, кл. G ОБ В 23/02, 1971

5

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для автоматического контроля больших интегральных схем | 1983 |

|

SU1124331A2 |

| Система для автоматического контроля больших интегральных схем | 1976 |

|

SU664178A1 |

| Система автоматического контроля параметров | 1977 |

|

SU746435A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Система автоматического контроля параметров электронных схем | 1981 |

|

SU985764A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| ОПИСАНИЕ ИЗОБРЕТЕНИЯ | 1973 |

|

SU377738A1 |

| Устройство для контроля интегральных схем | 1978 |

|

SU744579A1 |

| Устройство для контроля радиотехническихОб'ЕКТОВ | 1979 |

|

SU796859A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1608697A1 |

Авторы

Даты

1980-07-05—Публикация

1977-12-19—Подача