(54) МНОГОКАНАЛЬНОЕ ПРИОРИТЕТНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное приоритетное устройство | 1982 |

|

SU1038945A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

| Многоканальное приоритетное устройство | 1980 |

|

SU896624A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU824210A1 |

| Многоканальное приоритетное устройство для динамической памяти | 1981 |

|

SU1003087A1 |

| Многоканальное устройство приоритета | 1983 |

|

SU1119014A1 |

| Многоканальное устройство для управления очередностью запросов | 1982 |

|

SU1061143A1 |

| Приоритетное устройство | 1982 |

|

SU1027727A1 |

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1982 |

|

SU1068926A1 |

| Устройство для прерывания резервированной вычислительной системы | 1991 |

|

SU1824636A1 |

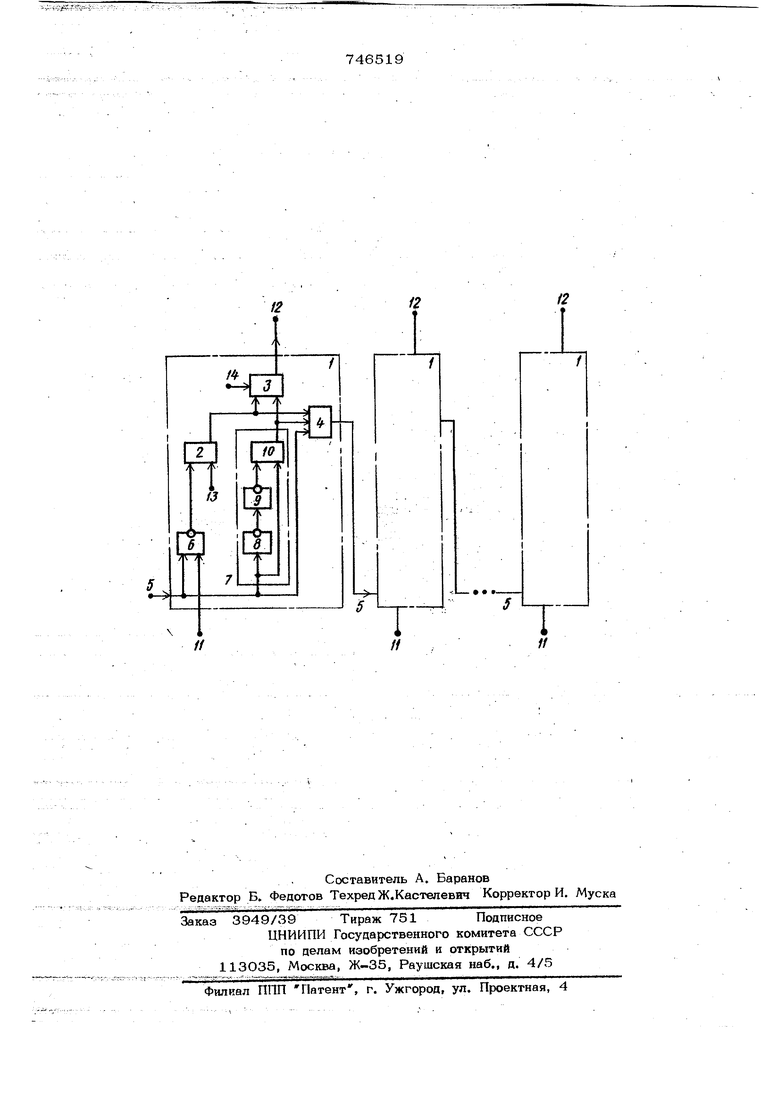

Изобретение относится к вычислитель|НЬй технике, может быть использовано в вычислительнь1 с системак, содержащих ряд блоков, подключеннык к устройству общего пользования, например, к общей информационно-адресной магистрали. Известно многоканальное устройство для подключения источников информации к общей магистрали 1 1 В этом устройстве сигнал опроса вырабатывается в одном иэ блоков и проходит последовательно по кольцу все блоки, участвующие в работе. Достигнув блока, в котором он выработался, сигнал кольцевого опроса при наличии заявок на общей шине регенерируется, а при отсутствии заявок исчезает. Недостатком устройства являет ся его повышенная сложность, связанная с обеспечением высокого быстродействия и равноприоритетной дисциплины обслужи- вания. Из известных устройств наиболее близким по технической сущности к пред-лагаемому является многоканальное приоритетное устройство 2. Оно содержит в каждом канале триггер запроса, выход Которого соединен с первым входом элемента подтверждения запроса и, через элемент передачи разрешения, - с входом следующего канала. Триггер запроса выполнен на двух элементах И-НЕ, соединенных по схеме RS- rparrepa, управляемого сигналами логических нулей, элемент передачи разрешения выполнен на инверторе, элемент подтверждения запроса - на двухвходовом логическом элементе И. У этого устройства низкая помехозащищенность и ограниченные функциональные возможности. Первый недостаток состоит в следующем. В всходное состояние, когда отсутствуют сигналы запросов и сигнал разрешения во всех последовательно соединенных блоках, в каждом из них RS - триггер на элементах И-НЕ уста нов- лен в запрещенное состояние при котором на входы установки и сброса одновременно подаются сигналы логических нулей, и на обоих плечах триггера за счет этого поддерживаются логические единицы. При работе устройства в реальной системе не исключена возможность одновременного поступлеНия на некоторый блок сигналов запроса и разрешения. В этом случае RS -триггер на запрещенного состояния переходит непосредственно к состоянию запоминания (входы установки и сброса бдноёремёнйо перёхбдйт из нулевого в единичное состояние), минуя стадию установки или сброса. Процесс перехода неуправляем и М(5к:етпротекать, в такой последовательности: спустя вре- мя задёржки элемецтов И-НЕ на их выхо дах формируются логические нули, которые по цепям обратной связи передаются на входы элементов И-НЕ,й7 в бйучае, если из двух элементов И-НЕ элемент, управляемый запросом, оказался более . быстрым, триггер переходит в устойг чивое состояние, при коТорОм на его пл.ече, Соединённом со входом ийвертора, хранится единица; Таким образом, , п:6ступйвший одноврёменнсГс разрВ шением, в конечном счете воспринимается и передается на выход подтверждения запроса в виде полоЖите; ьно{ о потенцка .ла. Однако одновременно с этим отрицательный импульс, формируемый на тригг8 ре, проходит через инвертор и и виде сиг нала разрешения поступает в Следующие блок(, что Может привести к бдноврёмен HOMjr выходу на магистр Ё двух активны устройств и, следовательно, к сбою сис темы, -.:- . -.-Гч :-;-.--..--: Отмеченный выше недостаток, связанный с ограниченными функциональнымивозможностями известного устройства обусловлен двумя факторами. Во-первых, при отсутствии сигнала разрешения триг гер запроса теряет запрос, если он имеет импульсный характер. Во-вторых, .за счет одновременного стробирования последовательно соединенных элементов . И-НЕ и И сигналом разрешения при от сутствии запроса на выводе элемента И формируются ложные кратковремеш ые импульсы, которые необхЬдимо компенсировать введением дополнительных элемен тов, например, интегрирующих RS -звеньев, подключаемых к выходам элементов И Цель изобретения - повышение помехо устойчивости и расширение функционалн ных возможностей устройства. Поставленная цель достигается тем, что в устройство введены элемент 74 9.4 первый и второй элементы НЕ, триггер Компенсации, причем первый вход элемента И-НЕ является четвертым входом каждого канала устройства, второй вход элемента И-НЕ, вход первого элемента НЕ. и первый вход триггера компенсации соединены со вторым входом элемента И, выход элемента И-НЕ соединен со вторым входом триггера запроса, выход первого элемента НЕ подключен ко вхо-ду второго элемента НЕ, выход которого соединен со вторым входом триггера компенсации, выход которог о подключен к третьему входу элемента И и третьему входу триггера подтверждения запроса. На, чертеже показана логическая схема предлагаемого многоканального прйори тетного устройства. Устройство содержит ряд по ледова . тельно включенных каналов 1, каждый из которых включает в себя триггер за проса 2, выход которого соединен с пер вым входом триггера подтверждения за проса 3 и через элемент И 4 - с треть им входом 5 следующего канала, эле- , мент Й-НЁ 6 и лшшя задержки 7, выполйеннукз 6 виде последовательно соединенных первого элемента НЕ 8, второго эле мента НЕ 9 4i триггера компенсации 10, выход KOTopot O соединен с третьим Бхо дом триггера подтверждения запроса 3 и с третьим входом элемента И 4. Второй вход элемента И 4 соединен со входом первого элемента НЕ 8, со входом элемента б, с установочным входом триггера Ю и со входом 5 соответствующего канала, выход элемента 6 соединён сОвходом триггера 2. Вход 11 каждого канала является входом приема запроса, выход 12 каждого канала является выходом подтверждения запроса, входы 13 и 14 каждого канала служат для установки в исходное состояние соответственно триггера 2 и триггера 3. Устройство может быть выполнено на различных типах логических элементов. Для определенности в дальнейшем предполагается, что элемент 6 прёдстав«ляет собой двухвходовый логический элемент типа ИЛИ-НЕ, элемент 4 - элемент типа И, элементы 2, 3 и 10-D- триг- . геры. Кроме того, предполагается, что пары элементов: 2 и 10, а также 6 и 8 выполнены на одних и тех же кристаллах интегральных схем. Это условие не обя аательно, однако оно автоматически (Обеспечивает гарантированные вр9мен1гь1е 57 .соогношения между информационными и .управляющими сигналами, а именно, превышение времени задержки распространения вкодногр сигнала разрешения по цепи над временем задержки по цепи . Ниже рассмотрен принцип действия многоканального приоритетного устройства. Устройство приводится в исходное сос .тонкие воздействием импульсных сигна.лов на входы устаповки 13 и 14, после чего на выходах триггеров 2 и 3 устана навливаются логические единицы, Сигна;™ лы разрешения в исходном состоянии отсутствуют, т. е. на входы 5 каждого блока поданы логические нули. Триггер 10под действием нулевого сигнала на установочном входе, связакном со входом 5, переведен в нулевое состояние. Сигнал запроса, поступающий на вход 11в виде логического нуля, при отсутст вий сигнала разрешения проходит через элемент 6 я подается на синхронизирующий вход D -триггера 2, переводя его в нулевое состояние, так как Ъ вход этого триггера подключен к шине логичес кого .нуля (например, при положнтель ной логике | щине земля ), Снгнап разрешения, поступающий на вход 5 в виде логической единицы, через элементы НЕ. 8 и 9 поступает на синхронизирующий вход 15-триггера 10, переводя его в единичное состояние, так как , Т) -вход этого триггера подключен к шине логической 8 диницы. Далее, в зависимости от состояния триггера запро сов 2, или срабатывает элемент И 4, пе редавая сигнал разрешения на вход 5 . следующего блока, или под воздействием фронта сигнала с выхода триггера 10 на синхронизирующий вход Т) - триггера 14 последний формирует на выходе 12 сигнал подтверждения запроса в виде логического нуля, так как на В -«ход это- го триггера подан логический нуль с . триггера 2. Запрос, поступающий на вход 11 при наличии сигнала рйзрешеиия на входе 5, блокируется элементом 6 на вре мя трансляции сигнала разрешения через данный блок; по окончании трансляции запрос запоминается на триггере 2. Ус тановка триггеров 2 и 3 а исходное состояние производится сигналами от устрой ства, получившего сигнал подтверждения запроса; конкретные временные соотно9шения между этими сигналами определяются принятым для данной системы интерфейсом. Использование предлагаемого много- канального приоритетного .устройства в .вычислительных системах позволяет повысить их помехоустойчивость и расширить функциональные возможности. Формула изобретения Многоканальное приоритетное устройство, содержащее в каждом канале трир,гер запроса, триггер подтверждения зап:роса, элемент И, причем первый вход .триггера запроса является первым входом каждого канала устройства, а выход триггера запроса соединен с первым входом триггера подтверждения запроса и первым входом элемента И, второй вход триггера подтверждения запроса является вторым входом каждого канала устройства, а выход триггера подтверждения запроса является выходом каждого канала устройства, второй вход элемента И является третьим входом каждого кайада устройства, d выход алемейта И coeRHHek с третьим входом следующего канала устройства, о т л и ч а ю щ е вея тем, что, с целью повышения помехоустойчйвости, в каждом канале введены ёпбмеят И-НЕ, первый и второй элементы НЕ, триггер компенсации, причем первый вход элемента И-НЕ является четвертым входом каждого канала устройства, второй вход элемента. И-НЕ, вход первого элемента НЕ и пе{жый вход триггера компенсации соединены со вхо- рым входом элемента И, выход алемен- та И-НЕ соединен со вторым входом триггера запроса, выход первого эле.мента НЕ подключен ко входу второго элемента НЕ, выход которого соединен со вторым входом триггера компенсации, выход которого подключен к третьему входу элемейта И и третьему входу триггера подтверждения запроса. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 394789, кл. G Об F 8/04, 197О. 2,Авторское свидетельство СССР № 544967, кл, G Об F 9/18, 1972 (прототип).

Авторы

Даты

1980-07-05—Публикация

1977-12-29—Подача