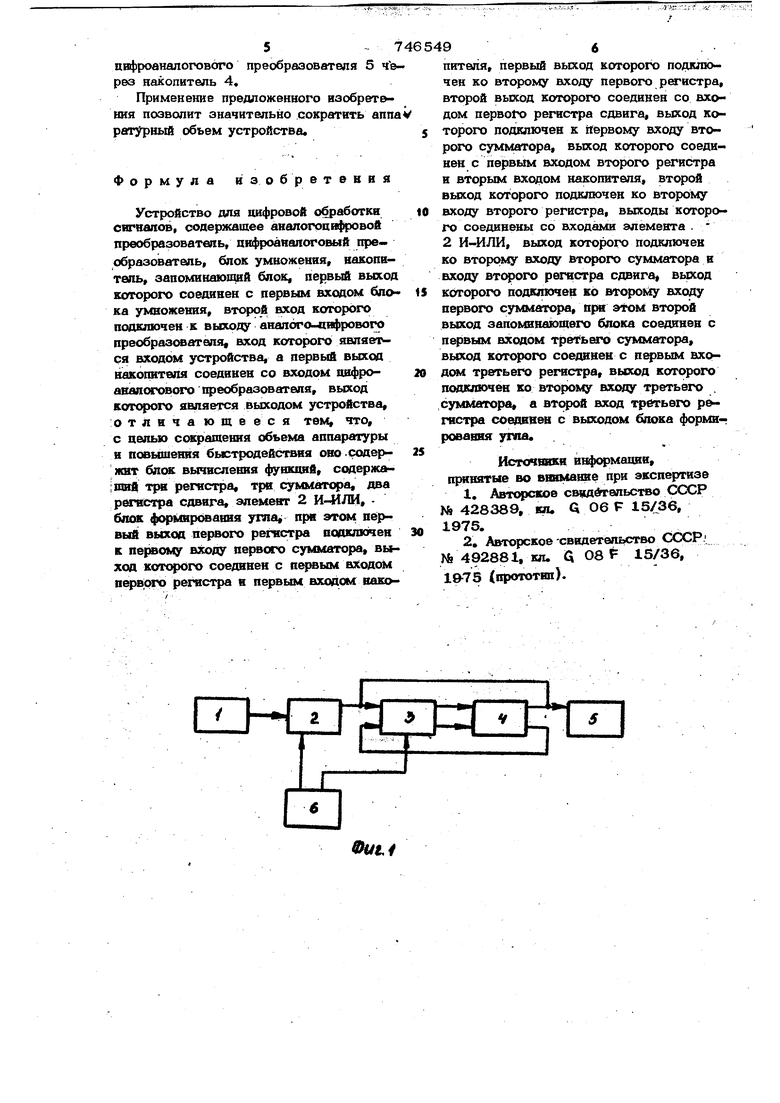

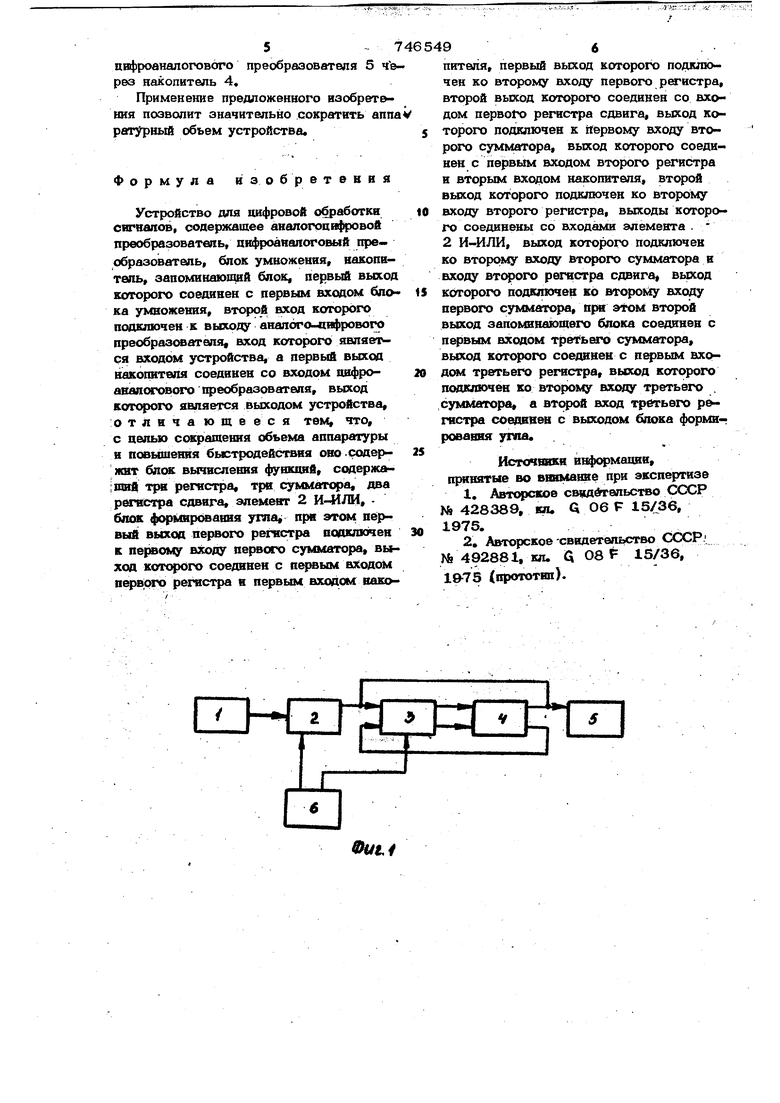

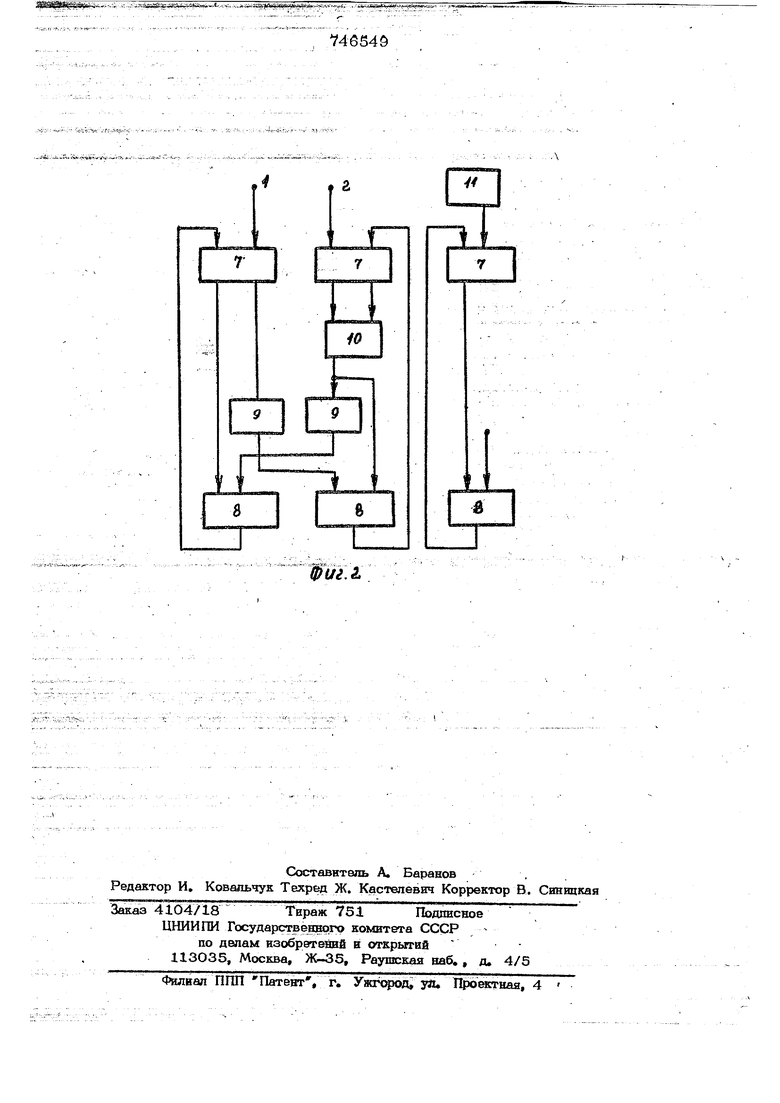

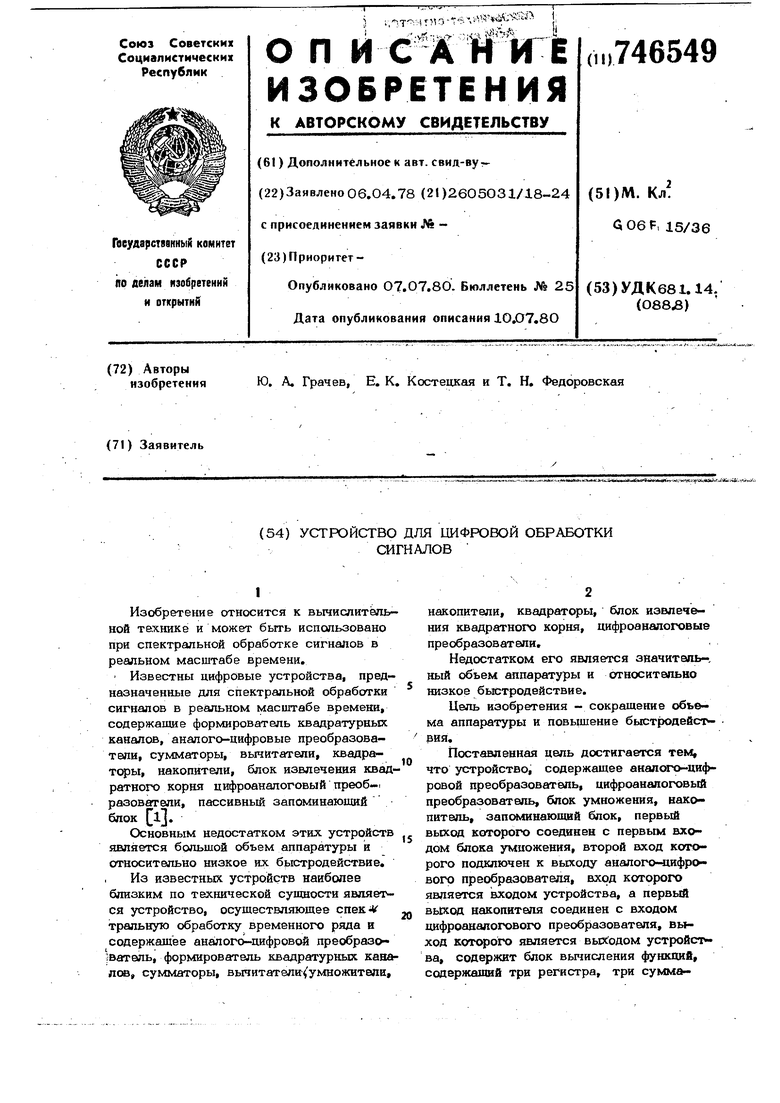

(54) УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ Изобретение относится к вычислительной технике и может быть использовано при спектральной обработке сигналов в реальном масштабе времени. Известны цифровые устройства, предназначенные для спектральной обработки сигналов в реальном масштабе времени, содержащие формирователь квадратурных каналов, аналого-цифровые преобразователи, сумматоры, вычитатели, квадраторы, накопители, блок извлечения квад ратного корня цифроаналоговый преоб-f разователи, пассивный запоминающий блок |l. Основным недостатком этих устрсэйств является большой объем аппаратуры и относительно низкое их бьютродействие. Из известных устройств наиболее близким по технической сущности являет, ся устройство, осуществляющее спек тральную обработку временного ряда и содержащее аналого-цифровой npeo6paat (Ваталь, формирователь квадратурных кана лов, сумматоры, вычитатели умнояситеяи. СИГНАЛОВ накопители, квадраторы, блок извлечения квадратного корня, цифроаналоговые преобразователи. Недостатком его является значитапь-, ный объем аппаратуры и относительно низкое быстродействие. Цель изобретения - сокращение объема аппаратуры и повышение быст|Х дейс1 вия. Поставленная цель достигается тем, что устройство, содержащее аналого-цифровой преобразователь, цифроаналоговый преобразователь, блок умножения, накопитель, запоминающий блок, первый выход которого соединен с первым входом блока умножения, второй вход которого подключен к выходу аналого-цифрового преобразователя, вход которого является аходом устройства, а первый выход накопителя соединен с входом дифроащалогового преобразователя, выход которого является вьсСодом устройства, содержит блок вычисления функций, содержащий три регистра, три сумматфа, два регистра сдвига, элемент 2 И-ИЛИ, блок формирования угла, при этом первый выход первого регистра,: подключен к первому аходу первого сумматора, выход которого соединен с первым входом первого регистра и первым входом накопителя, первый выход которого подключен ко второму входу первого регистра, второй вьсход которого сое дийен со входом первого, регистра сдвига вьрсод которого подключен к первому входу второго сумматора, выход которого со динен с первым входом второго регистра и вторым входом накопителя, второй которого подключен ко второму входу второго регистра, выходы которого со дйнены со входами элемента 2 И-ИЛИ, выход которого подключен ко второму входу второго сумматора и входу второго регистра сдвига, выход которого подключей ко второму входу первого сумматора, при этом второй выход запоминающего блока соединен с первым входом третьего сумматора, выход которого сое динен с первым входом третьего регист ра, выход которого подключен ко второ му входу третьего сумматора, а второй вход,третьего регистра соединен с выходом блока формирования угла. На фиг. 1 приведена функциональная схема устройства;, цифровой обработки сигналов на фиг. 2 - функциональная схема блока вычисления функций. В состав устройства входят .аналогоцифровой преобразователь 1, блок 2 умножения, блок 3 вычисления функций, накопитель 4, цифроаналоговый преобразователь 5, запоминающий блок 6, тр регистра 7, три сумматора 8, два регистра 9 сдвига, элемент 10 2И-ИЛИ, блок И формирования угла. . Устройство работает следующим образом. С выхода аналогоцифрового преобразо вателя 1 входная информация (код выборки) X(f ) поступает на один из входов блока умножения 2, на второй вход которого и это же время поступает с выхода запоминающего блока б значение огибающей импульсной реакции реала зуемого фильтра h (гп Т ) . Результат с выхода блока 2 умножения (mT).h(mT)3 (взвешенное значение кода выборки) поступает на первый вход блока 3 вычисления функций. На третий вход этого же блока поступает из запог мннающего блока 6 значение o(rclgi :(j -цюмер итерации, выполняемой в бло746549ке 3, вычисления функций, зависящий от заданной точности). Блок вычисления 3 функций на первом этапе работает по алгоритму Вопдера в поворота осей координат. При этом по значению угла, определяемого, круговой частотой настройки г -го фильтра сО . вычисляемому в блоке Ц формирования угла, и по взвешенному значению кода выборки на выходе блока 3 вычисления функций получаются следующие значения: на первом выходе - к(гоТ)-ь(тТ)-со«,() на втором выходе -X(mTVh(mT).4ir,{miOfc.l). С вьаодов блока 3 вычисления функций полученная информация поступает на входы накопителя 4. В блоке 11 формирования угла к этому моменту вычнсяяется новое значение m Т (для другого фильтра п ), по которому вновь в блоке 3 вычисления функций вычисляются значения косинусной и синусной составляюышх для этого фильтра. После получения данных для всех фильтров для одного значения выборки операция повторяет ся для всех фильтров по всем выборкам аналогично описанной вьшхе. После (п-гт) тактов в накопителе 4 находятся накопле Еые п значений для косинусней и для синусной составляющих сигнала А(п) и В (rt): () B(n)-S x(mTyh(mT).sin(mTcx После этого выполняется операдвя детектирования, т. е. вычисления квадратного из суммы квадратов составляюиих сигнала на выходе каждого фнльлграi((n)e() Эта операция вьтолняется в блоке 3 вычисления функций. Для этого информгнция (значения Аф) и В(п) ) с выходов накопителя 4 поступает на первый и второй входы блока 3 вычисления функций (на входы пёрвогх и второго регистров 7 соответственно). Блок 3 вьгаисления функции работает по алгоритму Вопдера в режиме от прямоугопьньк координат к полярным, что позволяет вычислить корень квадратный изсуммы квадратов двух составляющих сигнала. Результат вычисления & (п) с первого выхода блока вычисления функций (т. е. с выхода первого сумматора 8) поступйвт на вход цвфроаналогового преобразователя 5 чЪ реа накопитель 4, Применение предложенного нзобрет&ния позволит значительно сократить аппа ратурный объем устройства. Формула изобретения Устройство для цифровой обработки сягнапов, содержащее аналогрци1{ ровой преобразователь, дифроаналоговый преобразователь, блок умножения, накопитель, запомннаюпшй блок, первый выход которого соединен с первым входом бло ка умножения, второй вход которого подключен к выходу аналого-цифрового преобразователя, вход которого являет ся входом устройства, а первый выход накопителя соединен со входом цифроаналогового преобразователя, выход является выходом устройства, отлнчающееся тем, что, с целью сокращения объема аппаратуры н повышения быстродействия оно садержнт блок вычисления функций, содержа;0ш4 Т1Ж регистра, три сумматора, два регистра сдвига, элемент 2 И-ИЛИ, блок формйрсдаания угла при этом первый выход первого регистра подключен к первому взсоду первого сумматора, вы ход которого соединен с входом nepBptx) регистра и первым входом иако пятеяя, первый выход которого подключен ко второму входу первого регистра, второй выход которого соединен со входом первого регистра сдвига, выход которого подключен к первому входу второго сумматора, выход которого соединен с первым входом второго регистра и вторым входом накопителя, второй выход которого подключен ко второму входу второго регистра, выходы которого соединены со входами элемента . 2 И-ИЛИ, выход которого подключен ко второму входу второго сумматора и входу регистра сдвига, выход которого подключен ко второму вхсаду первого сумматора, ври этом второй выход запоминающего блока соединен с первым входом третьего сумматора, выход соединен с входсял третьего регистра, выход которого подключен ко второму входу третьего . сумматора, а второй вход третьего регистра соединен с выходом блока формирования yivia. Источники информации, принятые во вшивание при экспертизе 1,Авторское свидетельство СССР № 428389, кп. Q 06 F 13/136, 1975. 2,Авторское -свидетельство tAA-.r№ 492881, кл. л ОБ F 15/36, 19-75 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор спектра,ОСНОВАННый HA диСКРЕТНОМ пРЕОбРАзО-ВАНии фуРьЕ | 1978 |

|

SU807181A1 |

| Устройство для измерения частоты гармонического сигнала | 1991 |

|

SU1809394A1 |

| Устройство для вычисления дискретного спектра действительного временного ряда | 1974 |

|

SU525960A1 |

| Цифровой фильтр | 1979 |

|

SU860286A1 |

| ИЗМЕРИТЕЛЬ ПОТЕРЬ МОЩНОСТИ (ВАРИАНТЫ) | 2011 |

|

RU2467337C2 |

| Устройство для сжатия информации | 1982 |

|

SU1023378A1 |

| Цифровой коррелятор | 1980 |

|

SU894719A1 |

| Цифровой спектроанализатор | 1979 |

|

SU859950A1 |

| Ифровое устройство для оптимального измерения частоты сигнала | 1972 |

|

SU478261A1 |

| Цифровой анализатор спектра | 1979 |

|

SU798615A1 |

746549

//

d

Авторы

Даты

1980-07-05—Публикация

1978-04-06—Подача