(5) ЦИФРОВОЙ КОРРЕЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1979 |

|

SU842768A1 |

| Коррелятор | 1983 |

|

SU1130874A1 |

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

| Цифровой коррелятор | 1979 |

|

SU851412A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Цифровой коррелятор | 1986 |

|

SU1416980A2 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

I

Изобретение относится к вычислительной технике и может быть использована в измерительный технике, а также в системах автоматического управления и контроля, применяемых, например, в радио.пока1дии.

Известен цифровой коррелятор, предназначенный для вычисления значений корреляционной функции исследуемых случайных процессов x(t) и y(t+1;) множительным методом. Коррелятор содержит два аналого-цифровых преобразователя, два входных регистра,множительное устройство, сумматор произведений, а также входное и выходное запоминающие устройства, входы двух аналого-цифровых преобразователей являются входами цифрового коррелятора, а выходы соединены с соответствующими входами двух регистров, выходы регистров подключены к двум входам множительного устройства, выход которого соединен со входом сумматора произведений.

первым входной регистр и сумматор произведений дополнительно связаны с входным и выходным запоминающими устройствами, а выход сумматора произведений является выходом цифрового коррелятора l 1.

Недостаток данного коррелятора низкое быстродействие,обусловленное наличием умножителя.

Наиболее близким к предлагаемому

10 является устройство цифровой корреляции, предназначенное для определения степени связи между двумя временными рядами цифровых величин, представленных в виде двоичных чисел в

15 нормальной форме. Устройство цифровой корреляции содержит два запоминающих устройства, два блока выделения порядков, два блока хранения знаков, сумматор порядков, блок совпадения,

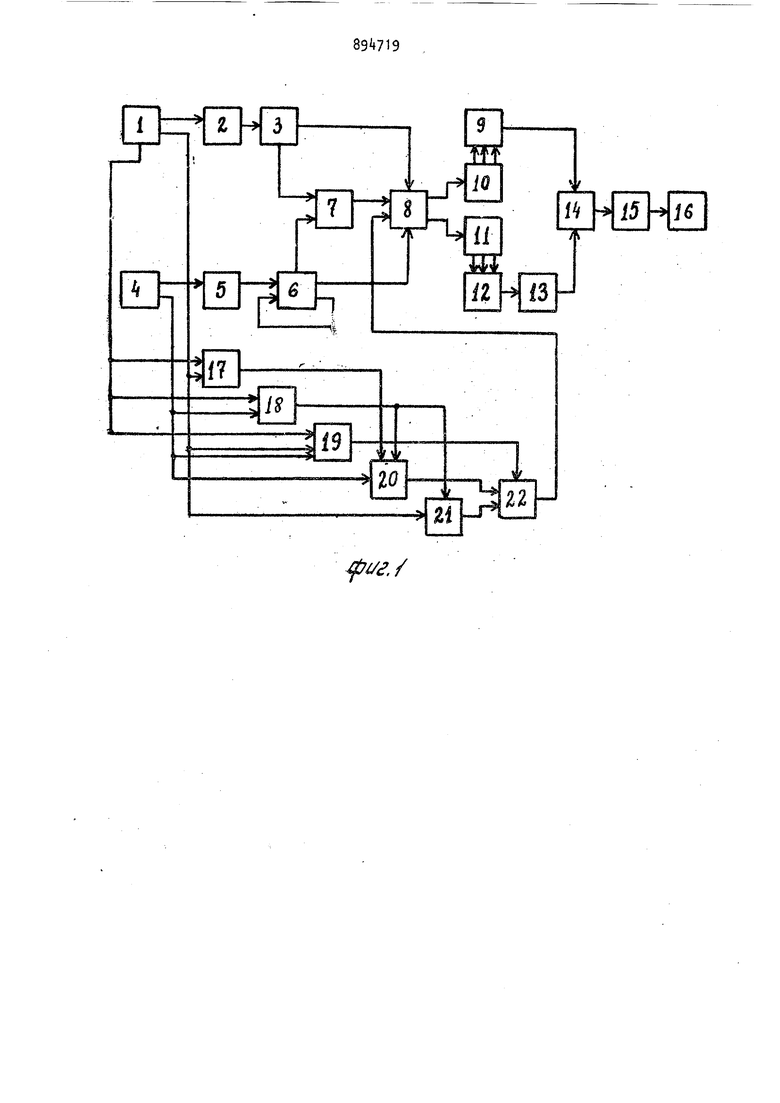

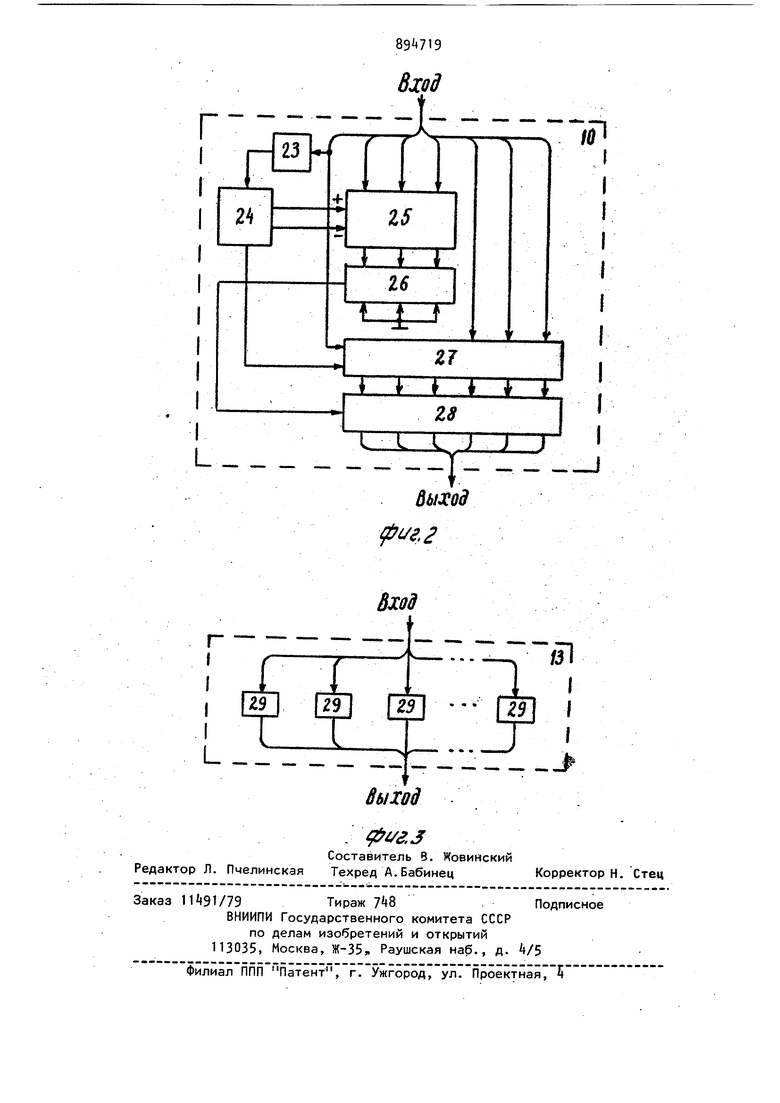

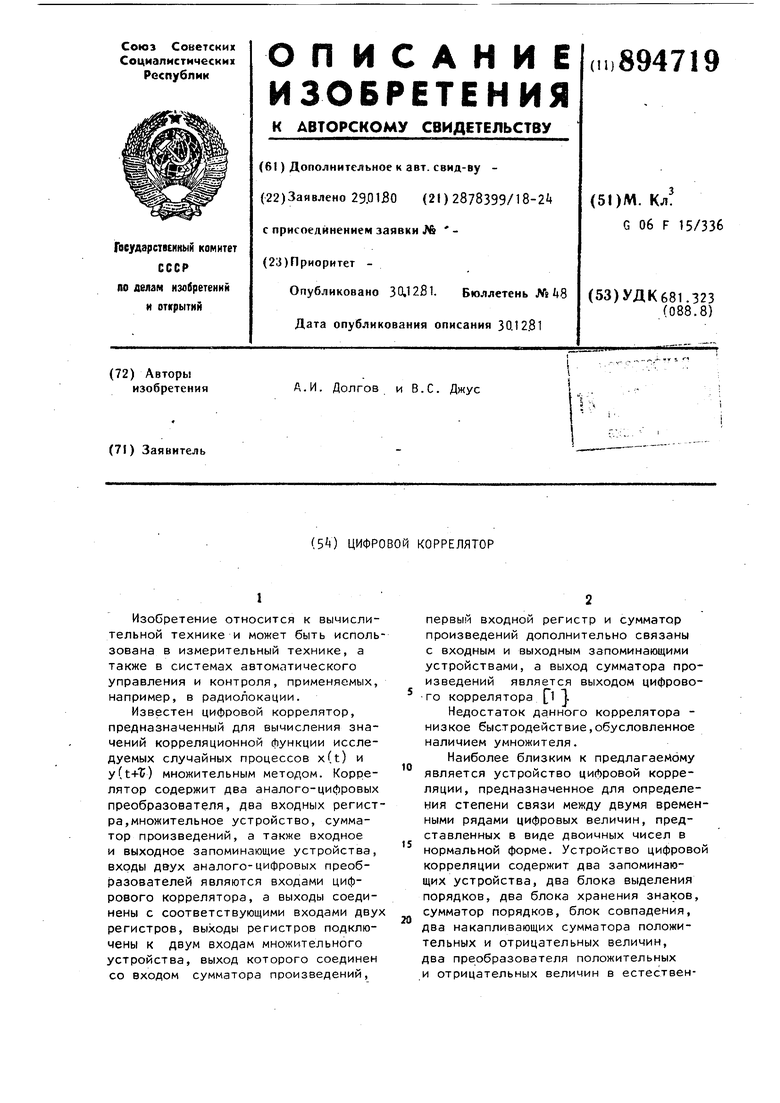

20 два накапливающих сумматора положительных и отрицательных величин, два преобразователя положительных и отрицательных величин в естественную форму, блок обращения кода, сумматор, цифроаналоговый преобразователь и коррелограф . Недостаток известного устройства цифровой корреляции - большая относительная статистическая погрешность корреляционной оценки при ограниченном числе выборок. Цель изобретения - повышение точности корреляционной оценки. Поставленная цель достигается тем, что в цифровой коррелятор, содержащий первый и второй блоки памяти, входы которых являются соответственно первым и вторым входами коррелятора, первые выходы первого и второго блоков памяти подключены ко входам соответствующих блоков выделе ния порядков, выход первого из которых подключен ко входу первого блока памяти знака, выход второго блока выделения порядков соединен с первым входом второго блока памяти знака, первый выход которого соединен с его BTopbtM входом, первый выход первого блока памяти знака и второй выход ет рого блока памяти знака подключены соответственно к первому и второму входам первого блока элементов И, третий вход которого соединен с выходом першого сумматора, входы которого подключены соответственно ко второму выходу первого блока памяти знака и к третьему выходу второго блока памяти знака, выходы блока эле ментов И подключены ко входам преобразователей положительных и отрицательных величин в естественную форму соответственно, выходы которых соеди нены с первым и вторым накапливающими сумматорами, выход первого из кот рых подключен к первому входу второг сумматора, второй вход которого подключен к выходу блока обращения кода вход которого соединен с выходом второго накапливающего сумматора, выход второго сумматора через цифроаналоговый преобразователь соединен со входом блока регистрации, введены три триггера, второй и третий блоки элементов И и блок сложения мантисс, выход которого подключен к четвертому входу первого блока элементЬв И, входы блока сложения мантисс соединены соответственно с выходами второ го и. третьего блоков элементов И и третьего триггера, второй выход . первого блока памяти подключен к первым входам триггеров, третий -вы|Ход первого блока памяти подключен ко вторым входам первого и третьего триггеров и к первому входу третьего блока элементов И, второй выход второго блока памяти соединен со вторым входом второго триггера, третьим входом третьего триггера и первым входом второго блока элементов И, второй и третий входы которого подключены соответственно к выходам первого и второго триггеров, второй вход третьего блока элементов И соединен с выходом второго триггера, выходы второго и третьего блоков элементов И подключены соответственно к первому и второму входам блока сложения мантисс, третий вход которого соединен с выходом третьего триггера. На фиг. 1 приведена схема цифрового коррелятора; на фиг. 2 - схема преобразователя положительных (отрица Тельных) величин в естественную форму; на фиг. 3 - схема блока обращения кода. Цифровой коррелятор содержит блок 1 памяти, блок 2 выделения порядков, блок 3 памяти знака, блок k памяти, блок 5 выделения порядков, блок 6 памяти знака, сумматор 7 порядков, блок 8 элементов И, накапливающий сумматор 9 для положительных величин, преобразователи 10 и 11 положительных и отрицательных величин в естественную форму, накапливающий сумматор 12 отрицательных величин, блок 13 обращения кода, сумматор 14, цифроаналоговый преобразователь 15, блок 16 регистрации, три управляющих триггера 17-19, два блока 20 и 21 элементов И и блок 22 сложения мантисс. - . Преобразователь положительных (отрицательных) величин в естествен- ; ную форму (фиг. 2) содержит блок 23 цифровой задержки, генератор 24 импульсов Сдвига, реверсивный счетчик 25, блок 2б поразрядного сравнения двух чисел, регистр 27 сдвига двоичного кода вправо и влево, блок 28 выходных элементов И. Блок 13 обращения кода (фиг. 3), предназначенный для преобразования прямого кода, в обратный, т.е. для замены нулей единицами и наоборот, представляет собой совокупность инверторов 29 число которых равно числу разрядов кода. Коррелятор работает следующим образом. Оцифрованные значения анализируе мых величин x(iut) и y{iut), представленные в нормальной форме (т.е. с помощью знака, порядка и мантиссы хранятся в блоках 1 и 3 памяти. Зна чения порядков (1), ( и ) через блоки 2 и 5 выделения порядко и блок 8 элементов И поступают на сумматор 7 порядков, где и вычисляет ся порядок произведения, знаки пере множаемых величин (sign , sign Му на блок элементов И, с помощью которого определяется знак произведения Полноразрядные модули мантисс / MX,-/ и |М. через блоки 20 и 21 элемен тов И поступают на блок 22 сложения мантисс, на котором вычисляется приближенная величина их произведения. Триггеры 17-19 вырабатывают соответственно три управляющих сигнала q ,, Яр и q Q . Управляющие сигналы сА. принимают единичные значег: ния в случае,-если соответствующие вторые старшие разряды модулей перемножаемых мантисс М V и М у не равны нулю, в противном случае q / 0 и . Управляющие сигналы q и qn, пос тупающие на управляющие входы блоков 20 и 21 элементов И, определяют вели чину т|эебуемого сдвига мантисс М«-соответственно. Кроме того, сигна qа поступает на второй управляющий вход блока 20 элементов И и указывает на то, в каком коде необходимо выдать остаток модуля мантиссы / чост/ остатком мантиссы здесь понимается полноразрядная мантисса без учета старшего значащего разряда.В случае / .|. передается через блок 20 элементов И в блок сложения мантисс в прямом коде. в обратном коде. Полуа при q ченные таким образом частичные произведения поступают на блок 22 сложе ния мантисс, где и формируется величина приближенного произведения. Дополнительный управляющий сигнал q вырабатывается управляющим триггером 19 и принимает единичное значение в случае, когда ни один из сомножителей или /М I не равен нулю. Так как любое двоичное число, не равное нулю, представленное в нормальной форме, всегда име-ет значащий старший разряд мантиссы, то условием выработки сигнала q(,1 является единичное значение старших разрядовдвух сомножителей (Mvv/ . Управляющий сигнал q поступает в блок 22 сложения мантисс и является разрешающим для формирования величины приближенного произведения мантисс. При совпадении знаков сомножителей значения приближенного произведения мантисс и их сумма порядков одновременно поступают через блок совпадения на вход преобразователя 10 положительных величин в естественную форму, в противном случае приближенное произведение и сумма порядков поступают на вход преобразователя 11 отрицательных величин в естественную форму. Преобразователь 10 работает следующим образом. С первого выхода блока 8 элементов И двоичный код положительных произведений через выходной регистр последнего поступает на вход преобразователя 10 положительных величин в естественную форму. При этом иеоб-, ходимо отметить, что знак произведения не поступает на преобразователь, так как он учитывается аппаратурно блоком элементов И. Разряды порядка двоичного кода яоступают на соответствующие входы двоичного реверсивного счетчика 25, а разряды мантиссы - на входы регистра 27 сдвига, отведенные для дробной части числа. Знак порядка поступает непосредственно на управляющий вход регистра сдвига двоичного кода (как управляющий сигнал, определяющий направление сдвига) и через блок 23 цифровой задержки - на вход генератора 2 импульса сдвига (как управляющий сигнал запуска последнего). Время зaдepжкиCTjJJ J) блока 23 определяется максимальным временем срабатывания уши двоичного реверсивного счетчика 25 или регистра 2 сдвига двоичного кода.Импульс знака порядка через Ti запускает генератор 2 импульса сдвига, который в зависимости от знака порядка выдает рибавляемые (+) или вычитаемые (-) игналы на соответствующие входы воичного реверсивного счетчика и дновременно с этим вырабатывает мпульсы сдвига, поступающие на ход регистра сдвига. В двоичном реверсивном счетчике 5 производится последовательное меньшение (увеличение) предварительо занесенного в него кода порядка. Выход двоичного реверсивного счётчи ка подключен к одному из входов схе мы поразрядного сравнения, на друго вход .которого поступает нулевой код, что эквивалентно подаче нулевого потенциала. В момент поразрядного совпадения нулевого кода с кодом реверсивного счетчика (иначе, в момент обнуления реверсивного счетчика), схеча поразрядного сравнений вырабатывает управляющий сигнал Чяыд в набор выходных элементов И. Последний предназначен для выдачи преобразованного кода произведения из нормальной формы в ,естественную под действием Чт,)л в накапливающий сумматор 9 положи- , тельных величин. На этом цикл перевода положитель ной величины произведения из нормал ной формы в естественную заканчивается. По структуре и работе преобразователь 11 совпадает с преобразовате лем 10, но его вход соединен со вторым входом блока 8 элементов И. С помощью преобразователей 10 и 11 осуществляется перевод вычисли тельных произведений из нормальной формы в естественную и передача их в соответствующие накапливающие сум маторы. Затем тактовым импульсом блока 1 памяти, осуществляющим выборку следующего сомножителя, произ водится обнуление триггеров 17-19, и устройство готово к обработке следующей пары сомножителей. После определения произведений всех сомножителей и их соответству щего накопления суммарная величина положительных величин непосредствен но, а отрицательных через блок 13 о ращения кода поступают на входы сум матора It. На последнем формируется окончательная оценка значения кор|реляционной функции R(k), которая после цифроаналогового преобразователя 15 отмечается на ленте корре Лографа блока 16 регистрации. Следующее значение оценки корреляционной функции определяется после осуществления требуемого сдвига k одной входной величины относительно друго Данный сдвиг производится с помощью цёШТ обратной связи, имеющейся в блоке 6 памяти знака. В дальнейшем работа цифрового Коррелятора протекает аналогично и на его выходе фор мируется приближенная оценка коррел 8 Гионной функции R(k), вычисленная огласно выражению 4t)-.(M .K) i ,.,nxi -nni4.)gryi Mx sig-nMv Ki, (.4)ocT у. 5/gUk) V Методами математического моделирования получены корреляционные оценки, вычисленные с помощью известного и предлагаемого цифровых корреляторов для -различных входных сигналов. В частности получены значения корреляционных функций (нормированные и ненормированные) для детерминированного сигнала синусоидальной формы, а также для случайных процессов экспоненциальными и экспоненциальнокосинусными корреляционными функциями. Сравнительный анализ результатов моделирования показывает, что точность корреляционной оценки для анализируемых сигналов, вычисленная, предлагаемым цифровым коррелятором, увеличивается в 1,3-1, раза по сравнению с известным. Такая точность позволяет использовать предлагаемый цифровой коррелятор, например, в системах автоматического управления радиолокационных устройств. В виду того, что в предлагаемом корреляторе операция приближенного умножения выполняется, в основном, за один шаг суммирования, а разрядность мантисс анализируемых сигналов выбирается равной разрядности порядков, то введение дополнительных блоков практически не приводит к снижению быстродействия. Проведенные расчеты показывают, что увеличение .точности корреляционной оценки пред(лагаемым. цифровым коррелятором обеспечивается за счет увеличения объема оборудования в среднем на 9,6. Таким образом, предлагаемый цифровой коррелятор способен обеспечить более высокую точность корреляционной оценки, чем известный, практически без снижения его быстродействия и существенного увеличения объема оборудования. Формула изобретения Цифровой коррелятор, содержащий первый и второй блоки памяти, входы которых являются соответственно первым и вторым входами коррелятора, первые выходы первого и второго блоков памяти подключены ко входам соответствующих блоков выделения порядков, выход первого из которых подключен ко входу первого блока памяти знака, выход второго блока выде ления порядков соединен с первым входом второго блока памяти знака, первый выход которого соединен с его вторым входом, первый выход первого блока памяти знака и второй выход второго блока памяти знака под ключены соответственно к первому и второму входам первого блока элементов И, третий вход которого соединен с выходом первого сумматора, вхо ды которого подключены соответственно ко второму выходу первого блока памяти знака и к третьему выходу второго блока памяти знака, выходы блока элементов И подключены ко входам преобразователей положительных .и отрицательных величин в естественную . форму соответственно, выходы которых соединены со входами соответственно первого и второго накапливающих сумматоров, выход первого из которых подключен к первому входу второго сумматора, второй вход которого подключен к выходу блока обращения кода вход которого соединен с выходом второго накапливающего сумматора, выход второго сумматора через цифроаналоговый преобразователь соединен 1910 со входом блока регистрации корреЛя тора, отличающийся тем, что, с целью повышения точности, в него введены три триггера, второй и третий блоки элементов И и блок сложения мантисс, выход которого подключен к четвертому входу первого блока элементов И, входы блока сложения мантисс соединены соответственно с выходами второго и третьего блоков элементов И и третьего триггера, второй выход первого блока памяти подключен к первым входам триггеров, третий выход первого блока памяти подключен ко вторым входам первого и третьего триггеров и к первому входу третьего блока элементов И, второй выход второго блока памяти соединен со вторым входом второго триггера, третьим входом третьего триггера и первым входом второго блока элементов И, второй и третий входы которого подключены соответственно к выходам первого и второго триггеров, второй вход третьего блока элементов И соединен с выходом второго триггера, выходы второго .и третьего блоков элементов И подключены соответственно к первому и второму входам блока сложения мантисс, третий вход которого соединен с выходом третьего триггера. Источники информации, принятые во внимание при экспертизе 1.Грибанов Ю.И. и др. Автоматические цифровые корреляторы. М., Энергия, 1971, с. 153. 2.Патент США If 3863058, Нки 235 152, опубл. 1970-(прототип J,

г./

дхаЗ

Авторы

Даты

1981-12-30—Публикация

1980-01-29—Подача