1

Изобретение относится к элемен-, там систем управления, а именно к корректирующим устройствам, применяелмм для повышения точности. j

Известны различные линейные и ; псевдолинейные корректирующие устройства, содержащие интегратор, сумматор, линейные фильтры и логический блок управления, состоящий из релей- JQ ных блоков и блоков умножения 1 .

Из известных наиболее близким по технической сущности является устройство 2 ; содержащее интегратор, последовательно соединенные первый фильтр, первое реле, первый блок ум-. ножения, первый однополуперйодный выпрямитель, второй блок умножения и первый сумматор, и последовательно соединенные второй фильтр и втЬрое 2Q реле,выход которого соединен с вторыми входами первого и второго блоков умножения,а входы интегратора,первого и втЬрого фильтров подключены ко второму входу первого сумматора. jj

Недостаток этого устройства заключается в его низкой точности.

Цель изобретения состоит в повышении точности псевдолинейного кор|ректирующего устройства.

Поставленная цель достигается тем, что устройство содержит третье реле, блок определения модуля и последовательно соединенные апериодическое звено, сравнивающий элемент, третий блок умножения, второй сднополупериодный выпрямитель и второй сумматор, второй вход которого через блок определения модуля соединен с выходом апериодического звена, вход которого через интегратор соединен со вторым входом элемента сравнения, а выход второго сумматора через последовательно соединенные второй блок умножения и третье реле соединен со вторым входом третьего блока умножения.

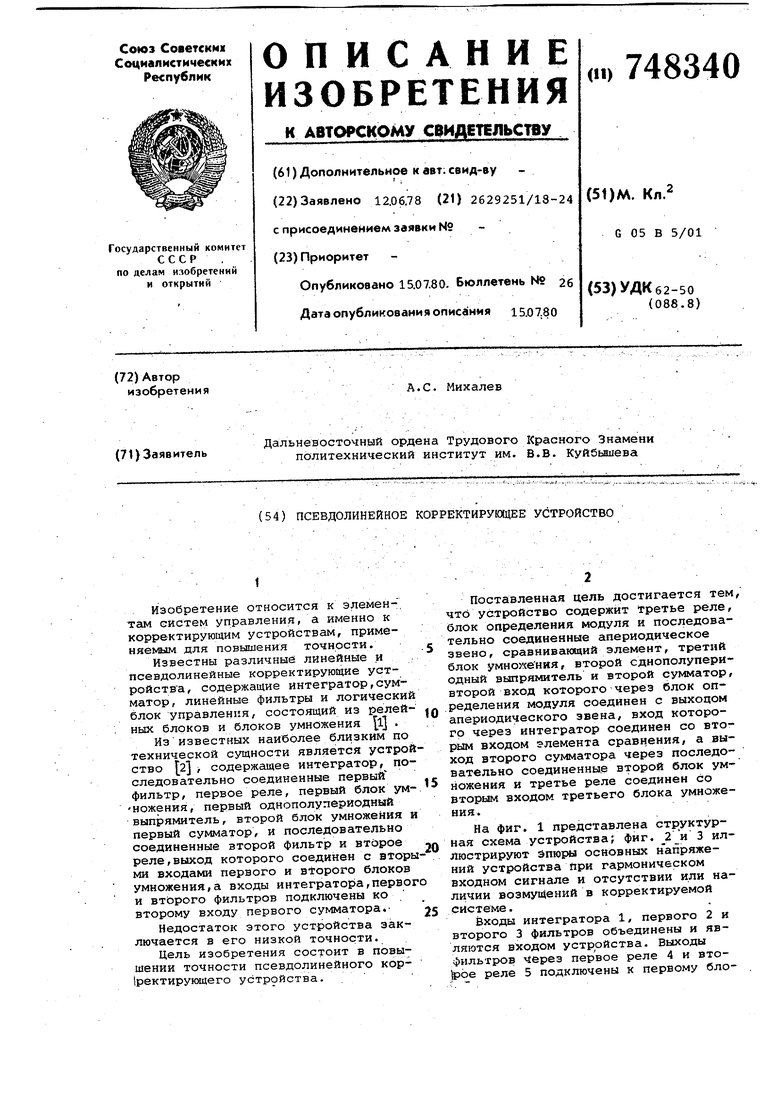

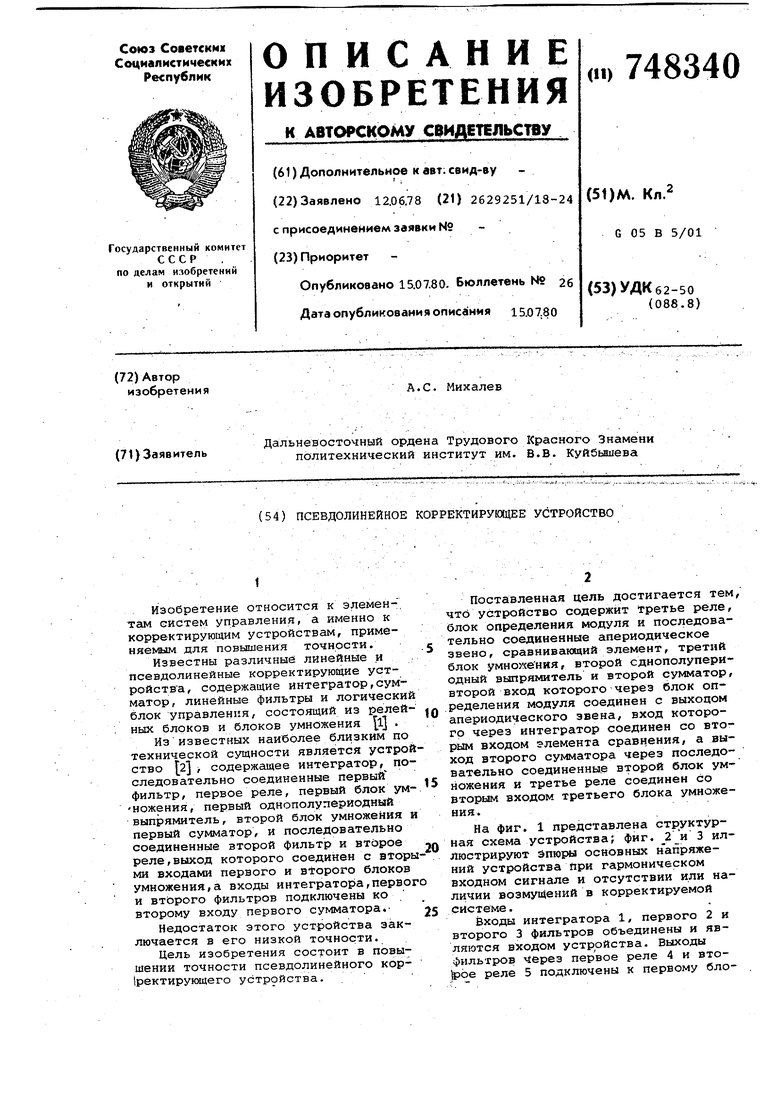

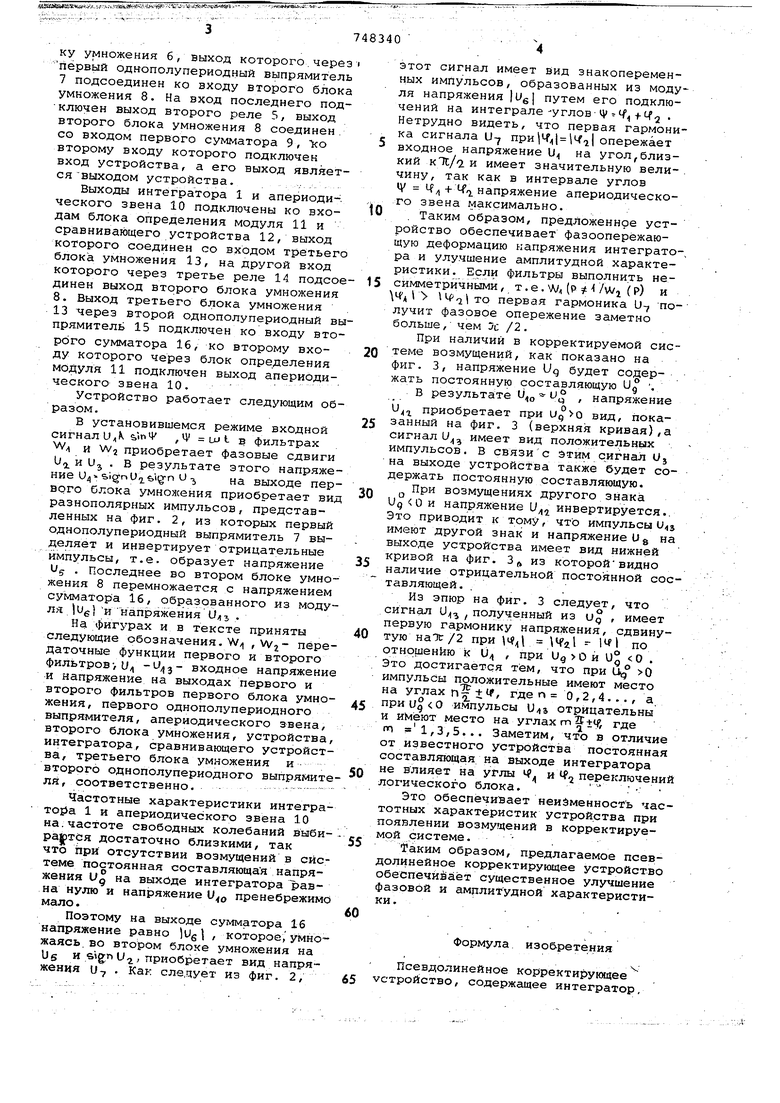

На фиг. 1 представлена структурная схема устройства; фиг. 3 иллюстрируют зпюры основных напряжений устройства при гармоническом входном сигнале и отсутствии или наличии возмущений в корректируемой системе.

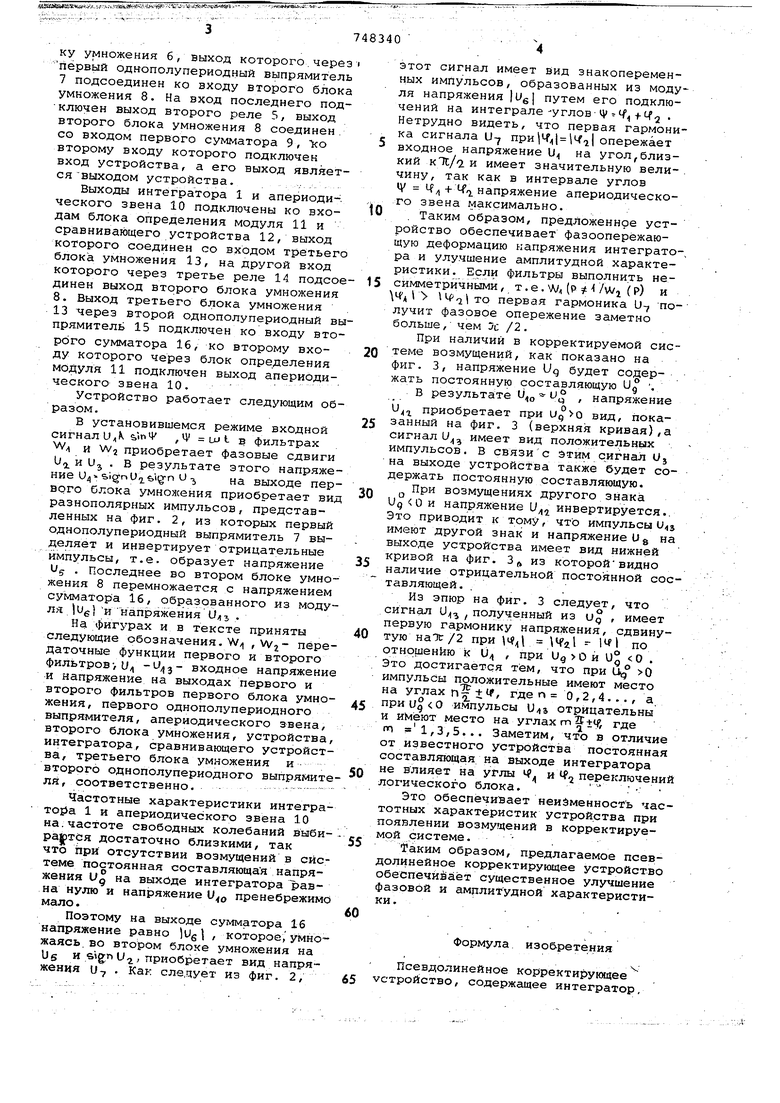

Входы интегратора 1, первого 2 и второго 3 фильтров объединены и являются входом устройства. Выходы фильтров через первое реле 4 и втоfc oe реле 5 подключены к первому блоку умножения б, выход которого.через первый однополупериодный выпрямитель 7 подсоединен ко входу второго блока умножения 8. На вход последнего подключен выход второго реле 5, выход второго блока умножения 8 соединен, со входом первого сумматора 9, Ко второму входу которого подключен вход устройства, а его выход является выходом устройства. V Выходы интегратора 1 и апериодического звена 10 подключены ко входам блока определения модуля 11 и сравнивающего устройства 12, выход которого соединен со входом третьего блока умножения 13, на другой вход которого через третье реле 14 подсое динен выход второго блока умножения 8. Выход третьего блока умножения 13 через второй однополупериодный вы прямитель 15 подключен ко входу второго сумматора 16, ко второму входу которого через блок определения модуля 11 подключен выход апериодического звена 10. Устройство работает следующим образом.. В установившемся режиме входной сигнал Ll;, ьтЧ ,U и t в фильтрах W и Wj приобретает фазовые сдвиги U и Uj . В результате этого напряжение U. bigT)U-z.eie-n О ,, на выходе первого блока умножения приобретает вид разнополярных импульсов, представленных на фиг. 2, из которых первый однополупериодный выпрямитель 7 выделяет и инвертирует отрицательные импульсы, т.е. образует напряжение Последнее во втором блоке умно женин 8 перемножается с напряжением сумматора 16, образованного из моду ля |Ug) инапряжения . На (фигурах и в тексте приняты следующие обозначения. W/t ,W2- пере даточные функции первого и второго фильтров-, и входное напряжение и напряжение на выходах первого и второго фильтров первого блока умно жения, первого однополупериодного выпрямителя, апериодического звена, второго блока умножения, устройства интегратора, сравнивающего устройст ва, третьего блока умножения и второго однополупериодного выпрямит ля, соответственно. Частотные характеристики интегра тора 1 и апериодического звена 10 на.частоте свободных колебаний выби ра)тся достаточно близкими, так что при отсутствии возмущений в сис теме постоянная составляюадая напряжения Ug на выходе интегратора равна нулю и напряжение пренебрежим мало. Поэтому на выходе сумматора 16 напряжение равно lUg , которое,умно жаясь, во втором блоке умножения на Us и sign U-j,, приобретает вид напряжения и7 Как следует из фиг. 2,

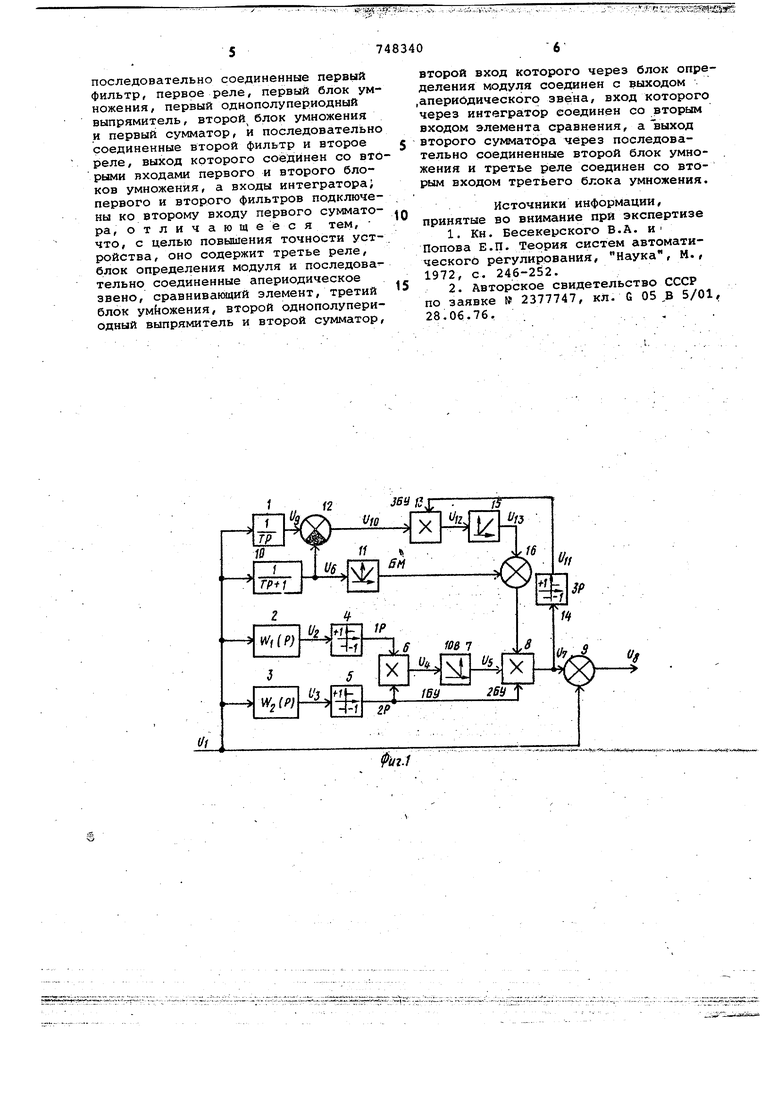

748340 тот сигнал имеет бид знакопеременых импульсов, образованных из моду я напряжения |Ug| путем его подклюений на интеграле-углов-ф / f Нетрудно видеть, что первая гармоника сигнала U- при 14 147 опережает входное напряжение и на угол,близкий KTt/i и имеет значительную вели- . чину, так как в интервале углов ly If + If/j напряжение апериодического звена максимально. Таким образом, предложенное устройство обеспечивает фазооперёжающую деформацию напряжения интеграто-, ра и улу.чшение амплитудной характеристики. Если фильтры выполнить несимметричными, т.е. W(P # w/i (Р) и Ч;( 1 1 то первая гармоника U- получит фазовое опережение заметно больше, чем jc /2 . При наличии в корректируемой системе возмущений, как показано на фиг. 3, напряжение Uq будет содержать постоянную составляющую U . В результате ° / напряжение и приобретает при и 0 вид, показанный на фиг. 3 (верхняя кривая),а сигнал и имеет вид положительных импульсов. В связи с Этим сигнал Uj на выходе устройства также будет содержать постоянную составляющую. При возмущениях другого знака Ug 0 и напряжение U инвертируется.. Это приводит к тому, что импульсы имеют другой знак и напряжение Ug на выходе устройства имеет вид нижней кривой на фиг. 3 (i из которойвидно наличие отрицательной постоянной составляющей. . . Из эпюр на фиг. 3 следует, что сигнал U;( полученный из Uq , имеет первую гармонику напряжения, сдвинутую Halt /2 при 42l l по отношению к и , при Ug 0 . Это достигается тем, что при U 0 импульсы положительные имеют место на углах п + , где о 0,2,4..., а приид 0 импульсы отрицательны и имеют место на углах где m 1,3,5... Заметим, что в отличие от известного устройства постоянная составляющая на выходе интегратора не влияет на углы Ч и if переключений логического блока. Это обеспечивает неизменность частотных характеристик устройства при появлении возмущений в корректируемой системе. . Таким образом, предлагаемое псевдолинейное корректирующее устройство обеспечивает существенное улучшение фазовой и амплитудной характеристики. Формула изобретения Псевдолинейное корректирующее устройство, содержащее интегратор.

последовательно соединенные первый фильтр, первое реле, первый блок умножения, первый однополупериодный выпрямитель, второй блок умножения и первый сумматор, и последовательно соединенные второй фильтр и второе реле, выход которого соединен со вторыми входами первого и второго блоков умножения, а входы интегратора; первого и второго фильтров подключены ко второму входу первого сумматора, отличающееся тем что, с целью повышения точности устройства, оно содержит третье реле, блок определения модуля и последовательно соединенные апериодическое звено, сравнивающий элемент, третий блок умйожения, второй однополупериС5дный выпрямитель и второй сумматор.

748340

второй вход которого через блок определения модуля соединен с выходом .апериодического звена, вход которого через интегратор соединен со вторым входом элемента сравнения, а выход второго сумматора через последовательно соединенные второй блок умножения и третье реле соединен со вторым входом третьего блока умножения.

Источники информации, принятые во внимание при экспертизе

1.Кн. Бесекерского В.А. И Попова Е.П. Теория систем автоматического регулирования, Наука, М., 1972, с. 246-252.

2.Авторское свидетельство СССР

по заявке 2377747, кл. G 05 ,В 5/01 28.06.76.,

| название | год | авторы | номер документа |

|---|---|---|---|

| Нелинейное корректирующее устройство | 1978 |

|

SU750421A1 |

| Нелинейное изодромное корректирующее устройство | 1978 |

|

SU767699A1 |

| Псевдолинейное корректирующее устройство | 1979 |

|

SU851332A1 |

| Нелинейное корректирующее устройство | 1977 |

|

SU708299A1 |

| Псевдолинейное корректирующее устройство | 1977 |

|

SU628457A1 |

| Псевдолинейное корректирующее устройство | 1978 |

|

SU750422A1 |

| Псевдолинейное корректирующее устройство | 1976 |

|

SU591809A1 |

| Следящая система | 1978 |

|

SU697969A1 |

| Нелинейное корректирующее устройство с фазовым опережением | 1988 |

|

SU1718182A1 |

| Самонастраивающаяся система комбинированного регулирования | 1987 |

|

SU1509828A1 |

Авторы

Даты

1980-07-15—Публикация

1978-06-12—Подача