(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСГВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1978 |

|

SU748509A1 |

| Буферное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU842973A1 |

| Буферное запоминающее устройство | 1981 |

|

SU991512A1 |

| Устройство для сдвига информации | 1979 |

|

SU1005034A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Регистр сдвига | 1978 |

|

SU771724A1 |

| Устройство для программного управления намоточным станком | 1990 |

|

SU1784942A1 |

| Устройство для задержки импульсов | 1982 |

|

SU1100723A1 |

| Счетное устройство | 1985 |

|

SU1256195A1 |

| Запоминающее устройство с само-КОНТРОлЕМ | 1979 |

|

SU809362A1 |

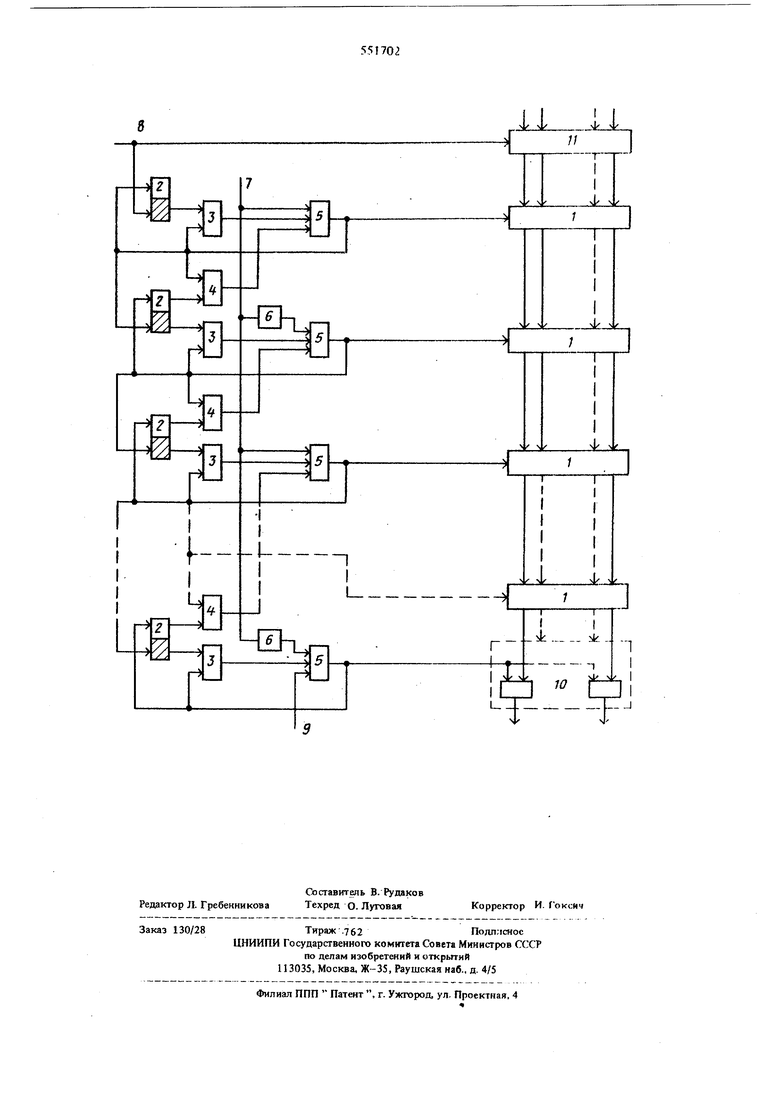

Известное буферное запоминающее устройство содержит поразрядно соединен 1ые регистры, ячейки управления считьшанием и записью, логические элементы И. Недостатками известного устройства являются невысока скорость работы и больише аппаратурные затраты. Наиболее близко к изобретению буферное запоминающее устройство, которое содержит п регистров, одноименные разрядные шины которых соединены последовательно, входы записи регистров, кроме первого, подключены к выходам элементов И, п триггеров, выходные элементы которых соединены с разрядными выходами п-го регистра и п-го элемента И, и шину тактовых импулЕсов. Однако это устройство обладает низким быстродействием, поскольку управление выполнено по многотактной схеме, а регистры выполнены на триггерах с пассивной записью. Цель изобретения - повышение быстродействия устройства. Это достигается тем, что буферное запоминающее устройство содержит п элементов ИЛИ первой груп{1Ы, п- 1 элементоп ИЛИ второй группы, элементы НЕ по числу четных регистров, единичные выходы триггеров подключены к первым входам одаоименных элементов ИЛИ первой группы, нулевые выходы триггеров, кроме первого,- к первым входам одноименных элементов ИЛИ второй группы, выходы элементов ИЛИ первой группы соединены с первыми входами одноименных элементов И, выходы элементов ИЛИ второй группы соединень: со вторыми входами предаадуищх элементов И, выходы элементов И подключены ко вторым входам одноименных элементов ИЛИ первой группы и, кроме П--ГО элемента И, - ко вторымвходам последующих элементов ИЛИ второй группы, третьи вТсоды нечетных элементов И соелинепы с шинойтактовых импульсов, подключенной через элементы НЕ к третьим входам четиьгх элементов И. На чертеже дана схема предлагаемого устройства. Устройсгао содержит п регистров 1, одноименные разряды которых соединены последовательно, п триггеров 2, элементов ИЛИ 3 первой группы, п-I элементов ИЛИ 4 Бтс1Х й группы, п элементрв И 5, элементы HF-, 6 по числу четных регистров

1, шину 7 тактовых импульсов, шину 8 записи информации.

Единичные выходы триггеров 2 подклняены к первым входам одноименных элементов ИЛИ 3 первой группы, нулевые выходы триггеров 2, крО ме первого (верхний на чертеже)., - к первым входам одноименных элементов ИЛИ 4 второй группы, выходы элементов ИЛИ 3 первой группы соединены с первыми входами одноименных элементо И 5, выходы элементов ИЛИ 4 второй группы соединены со вторыми входами предыдущих элементов И 5.

Выходы элементов И 5 подключены ко вторым входам одноименных элементов ИЛИ 3 первой группы и, кроме п-го элемента И (нижний на чертеже), - ко вторым входам последующих элементов ИЛИ 4 второй группы, третьи входы нечетных элементов И 5 соединены с шиной 7, подключенной через элементы НЕ 6 к третьим входам четных элементов И 5. Ко входу первого триггера 2 подключена шина 8, ко входу последнего элемента И 5 - шина 9 считьшания информавдй. Устройсгао также содержит выходные элементы И 10 для вывода информации и входрой регистр 11.

Устройство работает следующим образом.

На шину 7 постоянно гэступают тактовые импульсы, частота которых не ниже частоты записи информации. Для записи информации в запоминающее устройство на шину 8 поступает импульс, по которому первое слово записывается в регистр И, одновременно первый триггер 2 устанавливается в единичное состояние. Единичный потенциал с выхода первого триггера 2, проходя через первый элемент ИЛИ 3, открывает по первому входу первый элемент И 5. По второму входу элемент И 5 в этот момент открыт потенциалом с элемента ИЛИ 4. Тактовый .импульс, проходя первый элемент И 5, устанавливает первый триггер 2 в нулевое состояние, а второй триггер 2 - в единичное и переписывает ин opмaцию из регистра 11 в первый регистр 1. По заднему фронту тактового импульса срабатьшает второй элемент И 5, второй триггер 2 устанавливается, в нулевое состояние, третий триггер 2 - в единичное, и слово из первого регистра 1 переписывается во второй регистр 1.

Д альнейшее продвижение информации из регистра в регистр осуществляется аналогично.

Обратная связь между элементами И 5 и элементами ИЛИ 3 и 4 предотвращает обрезание нкшульсов на выходе элементов И 5, обешечивая

надежную перезапись информации из регистра в регистр и установку триггеров 2, Через тактовых импульсов (где п-количество регистров 1) первое слово окажется в последнем, п-ом регистре.

При считьша1шн информации на шину 9 считывания информации подается импульс и первое слово через элементы И 10 вьтодится из устройства. Если последующий регистр 1 занят, то сигнал с нулевого выхода триггера 2 поступает через одноименный

элемент ИЛИ 4 на вход элемента И 5 предыдущего разряда, блокируя перезапись информации в этот регистр. При освобождении последующего регистра происходит обнуление соответствующего триггера и разблокировка элемента И 5, служащего для перезаписи информации из предыдущего регистра.

По переднему фронту тактового импульса переписьшается информация из четного регистра 1 в нечетный, по заднему фронту происходит перезапись информации из нечетного регистра 1 в четный.

Формула изобретения

Буферное запоминающее устройство, содержащее п регистров, одноименные разрядные пшны которых соединены последовательно, а входы записи регистров, кроме первого, подключены к выходам элементов И, п триггеров, выходные элементы И, входы которых соединены с разрядными выходами п-го регистра и п-го элемента И, и шину тактовых импульсов, отличающееся тем, что, с целью згвеличения быстродействия, оно содержит п элементов ИЛИ первой группы, п-1 элементов ИЛИ второй группы, элементы НЕ по числу четных регистров, единичные выходы триггеров подключены к первым входам одноименных элементов ИЛИ первой группы, нулевые выходы триггеров, кроме первого, - к первым входам одноименных элементов ИЛИ второй группы, выходы элементов ИЛИ первой группы соединены с первыми входами одноиме1шых элементов И, выходы элементов ИЛИ второй группы соединены со вторыми входами предыдущих элементов И, выходы элементов И подключены ко вюрьп« входам одноименных элементов ИЛИ первой группы и, кроме п-го элемента И, -ко вторым входам последующих элементов ИЛИ второй группы, третьи входы нечетных элементов И соединены с ишной тактовых импульсов, подключенной через элементы НЕ к третьим входам

четных элементов И.

Авторы

Даты

1977-03-25—Публикация

1975-11-03—Подача