Изобретение относится к автоматике и вычислительной технике и предназначено для использования р запоми накмаих устройствах. В основном авт. свид. 652706 описан дешифратор, содержащий дешифраторную матрицу, к каждому столбцу которой подключены две одноименные входные шины, а к каждой строке две одноименные выходные шины, соединенные с соответствующей нагрузкой в котором в .каждом узле дешифратррной матрицы столбец соединен со стро кой при помощи двух резисторов, причем связь одного знака в узле дешифраторной матрицы осуществлена вк.шочением первого реьистора между перво i входной шиной столбца и первой выходной шиной строки и Btoporo резнетора между второй входной шиной столбца и второй выходной шяной стрю ки, а связь другого знака - вклк)чением первого резистора между второй входной шиной столбца с первой выход ной шиной строки и второго резистора маяду первой входной шиной столбца и второй выходной шиной строки. Недостатком данного дешиф|ратора является недостаточный коэффициент полезного действия и большие потери мощности в элементах. Целью изобретения является уменьшение потерь мощности в элементах дешифратора и повышение его КПД. Поставленная цель достигается тем, что в дешифратор, содержащий дешифраторную, построенную в соответствии с ортргональной матрицей Адамера матрицу, к каждому столбцу которой подключены две одноименные входные шины, а к каждой строке - две одноименные выходные шины, соединенные с соответствующей нагрузкой, в которой в каждом узле дешифраторной матрицы сто.лбец соединен со строкой при помощи двух резисторов, причем связь одного знака в узле дешифраторной матрицы осуществляется включением первого резистора между первой входной шиной ctoлбцa и первой выходной шиной строки и второго резистора между второй яходной шиной столбца и второй выходной шиной строки, а связь другого знака - включением первого резистора между второй входной шиной столбца и первой выходной шиной строки и второго резистора между перёоП входной шиной столбца и второй выходной шиной строки, последовательно с каждым резистором связи включены встречи друг другу два нелинейных элемента, имею1ДИХ в одном напраьлении вольт-амперную характеристику с участком отрицательного сопротивления, а в другом направлении - сопротивление блиэкое к нулю, fcanpHMep, -диоды.

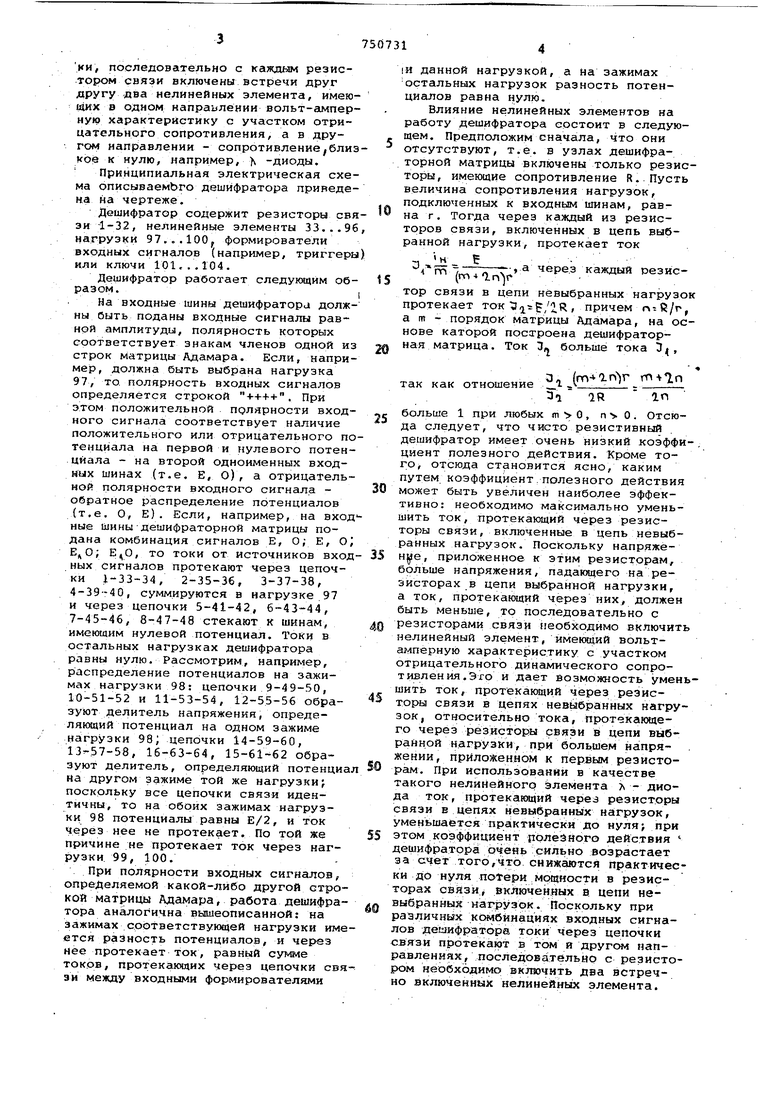

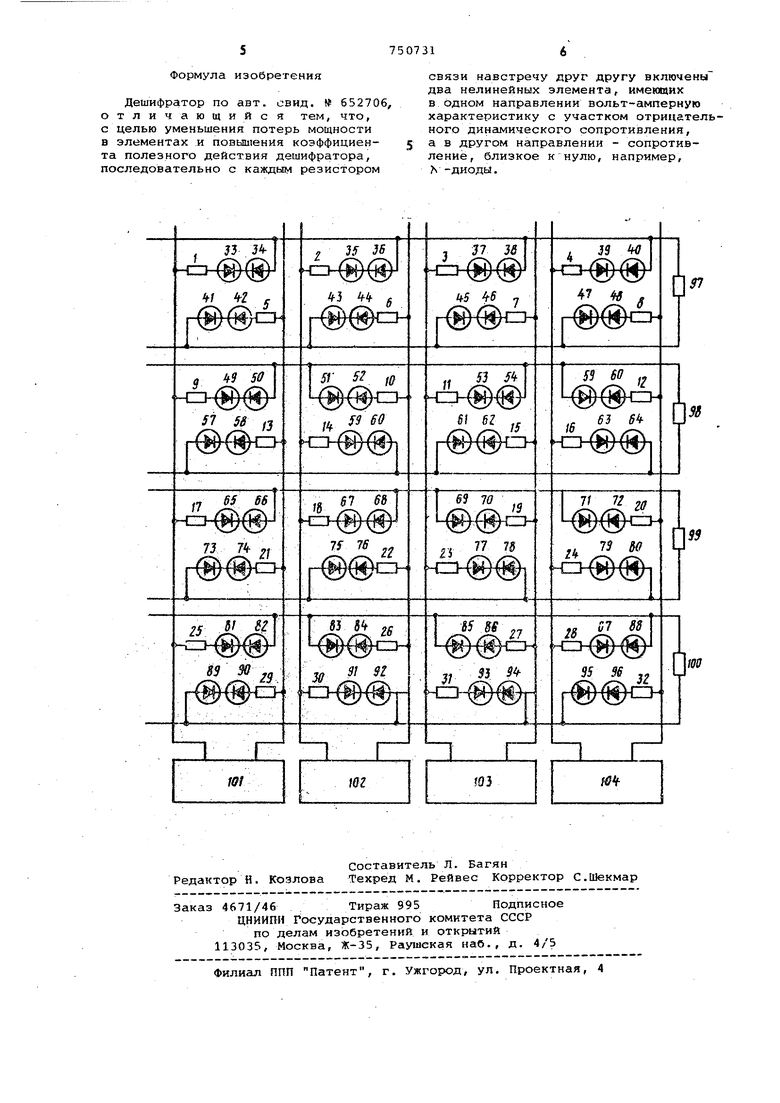

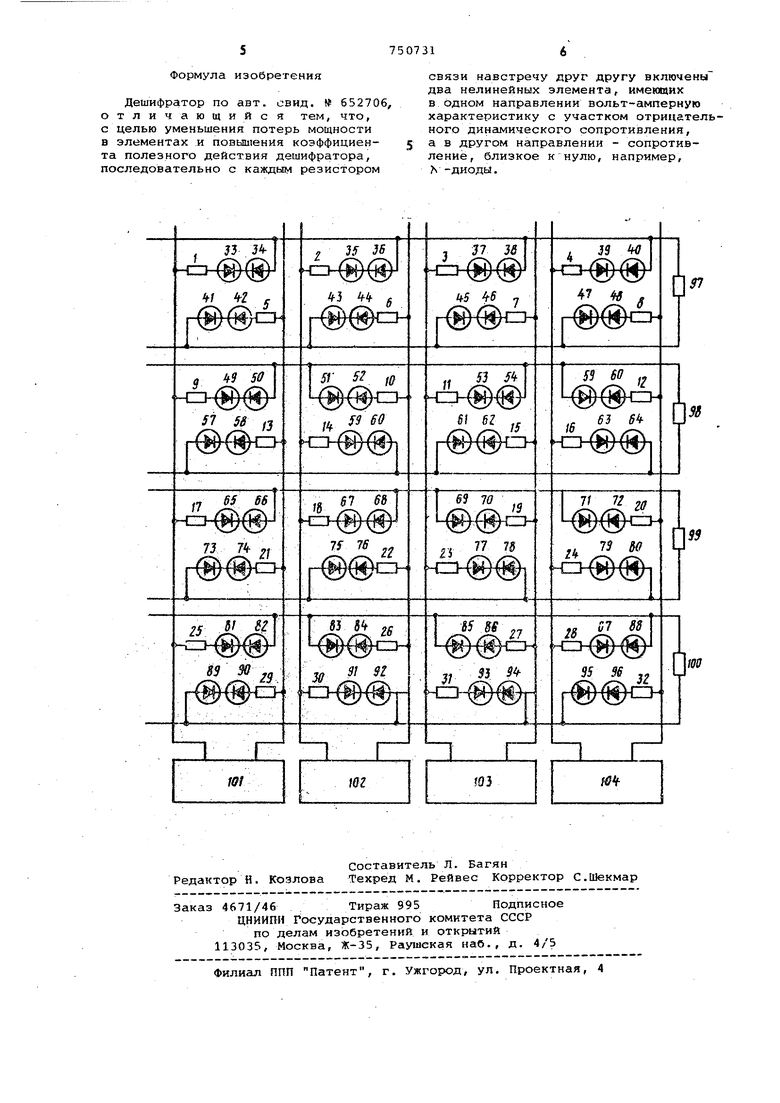

Принципиальная электрическая схема описываемЬго дешифратора приведена на чертеже.

Дешифратор содержит резисторы связи -1-32, нелинейные элементы 33... 96 нагрузки 97.0.100, формирователи входных сигналов (например, триггеры или ключи 101с..104.

Дешифратор работает следующим образом..

На входные шины дешифратора должны быть поданы входные сигналы равной амплитуды, полярность которых соответствует знакам членов одной из строк Матрицы АДамара. Если, например, должна быть выбрана нагрузка 97, то полярность входных сигналов определяется строкой ++++. При этом положительной прлярности входного сигнала соответствует наличие положительного или отрицательного потенциала на первой и нулевого потенциала - на второй одноименных входных шинах (т.е. Е, О), а отрицательной полярности входного сигнала обратное распределение потенциалов (т.е. О, Е). Если, например, на входные шины дешифраторной матрицы подана комбинация сигналов Е, О; Е, О ЕдО; Е,0, то токи от источников входных сигналов протекают через цепочки 1-33-34, 2-35-36, 3-37-38, 4-39-40, суммируются в нагрузке 97 и через цепочки 5-41-42, 6-43-44, 7-45-46, 8-47-48 стекают к шинам, имеющим нулевой потенциал. Токи в остальных нагрузках дешифратора равны нулю. Рассмотрим, например, распределение потенциалов на зажимах нагрузки 98: цепочки 9-49-50, 10-51-52 и 11-53-54, 12-55-56 образуют делитель напряжения, определяющий потенциал на одном зажиме нагрузки 98; цепочки 14-59-60, 13:-57-58, 16-63-64, 15-61-62 образуют делитель, определяющий потенциа на другом зажиме той же нагрузки; поскольку все цепочки связи идентичны, то на обоих зажимах нагрузки 98 потенциалы равны Е/2, и ток через нее не протекает. По той же причине не протекает ток Через нагрузки 99, 100.

При полярности входных сигналов, определяемой какой-либо другой строкой матрицы Аламара, работа дешифратора аналогична вышеописанной: на зажимах соответствующей нагрузки имеется разность потенциалов, и через нее протекает ток, равный сумме токов/ протекающих через цепочки связи между входными формирователями

|И данной нагрузкой, а на зажимах остальных нагрузок разность потенциалов равна нулю.

Влияние нелинейных элементов на работу дешифратора состоит в следующем. Предположим сначала, что они отсутствуют, т.е. в узлах дешифраторной матрицы включены только резисторы, имеющие сопротивление R. Пусть величина сопротивления нагрузок, подключенных к входньм шинам, равна т. Тогда через каждый из резисторов связи, включенных в цепь выбранной нагрузки, протекает ток

-, н В .

, через каждый оезис (m-t Iny

тор связи в цепи невыбранных нагрузо протекает ток , причем п R/r, а m - порядок матрицы Адамара, на основе каторой построена дешифраторная матрица. Ток 3 больше тока 3 ц ,

а« {m- lnjr m-vln так как отношение Т-- --:;

31 1R ас

больше 1 при любых m О , п . О . Отсюда следует, что чисто резистивный дешифратор имеет очень низкий коэффициент полезного действия. Кроме того, отсюда становится ясно, каким путем, коэффициент,полезного действия может быть увеличен наиболее эффективно: необходимо максимально уменьшить ток, протекающий через резисторы связи, включенные в цепь невыбранных нагрузок. Поскольку напряжен е, приложенное к этим резисторам, больше напряжения, падакяцего нарезисторах в цепи выбранной нагрузки, а ток, протекающий через них, должен быть меньше, то последовательно с резисторами связи необходимо включит нелинейный элемент, имекнций вольтамперную характеристику с участком отрицательного динамического сопротивления. Эгр и дает возможность уменшить ток, протекающий через резисторы связи в цепях невЫбранных нагрузок, относительно тока, протекающего через резисторы связи в цепи выбранной нагрузки, при большем напряжении, приложенном к первым резисторам. При использовании в качестве такого нелинейного элемента л - диода ток, протека евчий через резисторы связи Е цепях невыбранных нагрузок, уменьшается практически до нуля при этом крэффиииент полезного действия дешифратора очень сильно возрастает за счет того,что снижаются практически до нуля потери мощности в резисторах связи включенных в цепи невыбранных Hcsrj y3oK. Поскольку при различных комбинациях входных сигналов деыифратора токи через цепочки связи протекают в том и другом направлениях, последовательно с резистором необходимо включить два встречно включенных нелинейньсх элемента.

Формула изобретения

Дешифратор по авт. свид. № 652706, отличающийс я тем, что, с целью уменьшения потерь мощности в элементах и повышения коэффициента полезного действия дешифратора, последовательно с каждым резистором

связи навстречу друг другу включены два нелинейных элемента, имеющих в одном направлении вольт-амперную характеристику с участком отрицательного динамического сопротивления, а в другом направлении - сопротивление, близкое к нулю, например, -диоды.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1977 |

|

SU652706A1 |

| Дешифратор | 1987 |

|

SU1564732A1 |

| Матричный дешифратор для комбинаторного переключателя | 1977 |

|

SU696539A1 |

| ИНТЕГРАЛЬНЫЙ МАГНИТОТРАНЗИСТОРНЫЙ ДАТЧИК С ЦИФРОВЫМ ВЫХОДОМ | 2009 |

|

RU2437185C2 |

| Накопитель | 1989 |

|

SU1656595A1 |

| Устройство выборки адресов для блоков постоянной памяти | 1978 |

|

SU748506A1 |

| Устройство для индикации и считывания | 1984 |

|

SU1302316A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| МНОГОПОЗИЦИОННОЕ ПРОГРАММНОЕ УСТРОЙСТВО | 1971 |

|

SU320003A1 |

1

I Я 60 ,.

I л

15 Л

99

1100

fOt

iOtt

шз

Авторы

Даты

1980-07-23—Публикация

1977-11-21—Подача