1

Изобретение относится к области запо нающих устройств.

Известны устройства выборки адресов для блоков постоянной памяти. Одно из известных устройств выборки адресов содержит два дешифратора, подключенных к входам блока памяти соответственно по двум координатг1м 1 . Один из дешифраторов формирует положительные импульсы,а другой - отрицательные, что-и создает условия для протекания токов через запоминакнцие элементы по выбранному адресу.

Недостаток этого устройства выборки адресов состоит в низкой надеж-, ности, таккак отказ любого элемента приводит к выходу из строя всего устройства.

Из известных устройств наиболее близким техническим решением к данному изобретению является устройство выборки адресов для блоков постоянной памяти, содержахдее формирователи и матричный дешифратор комбинатор ного типа, выполненный на резистивных элементах связи в соответствии с матрицей Адамара и содержащий первую группу входяык шин, подключенных

к выходам одних из формирователей, и грух.лн выходных шин 1 .

Недостаток этого устройства состоит в том, что оно не может.быть использовано для выборки адресов из диодного блока постоянной памяти, так как этот блок памяти имеет одинарные входные шины, а устройство выборки адресов - парные выходные.

О Целью изобретения является упрощение устройства и расширение области его применения за счет обеспечения возможности использования устройства в диодных блоках постоянной памяти.

15 Поставленная цель постигается тем, чтр устройство содержит вторую группу входных шин, соединенных с выходами других формирователей, причем входные шины каждой группы соединены

20 резистивными элементами связи с .выходными шинами одноименной группы.

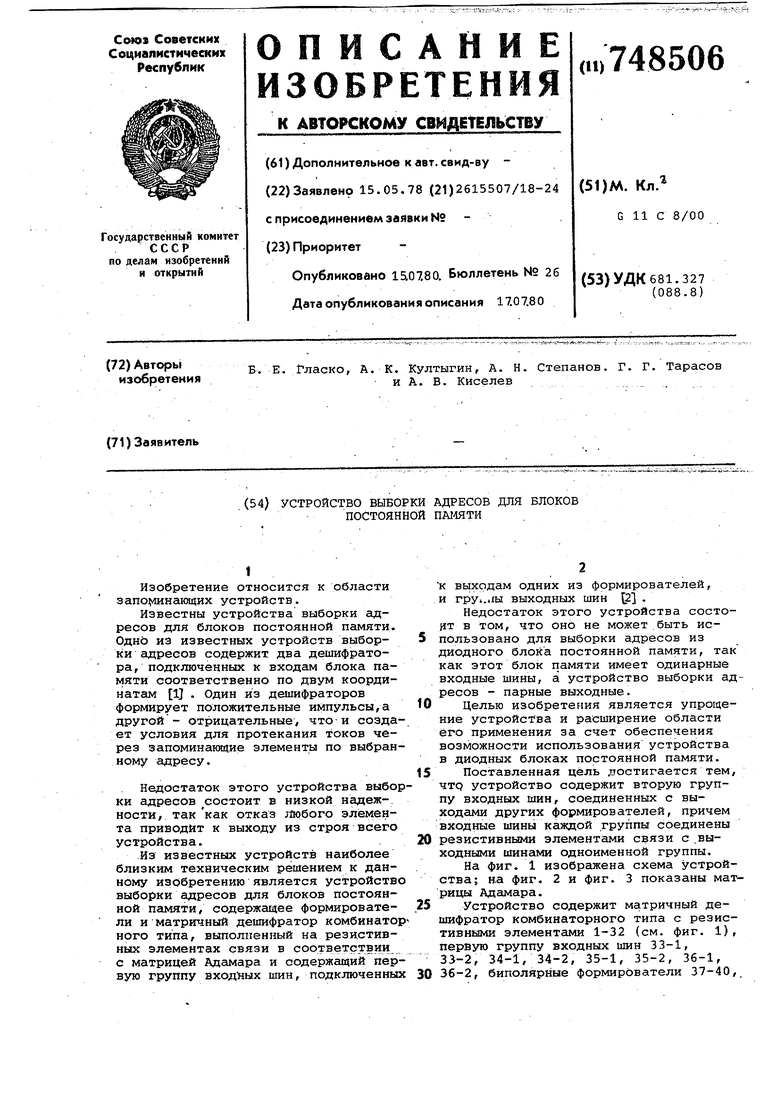

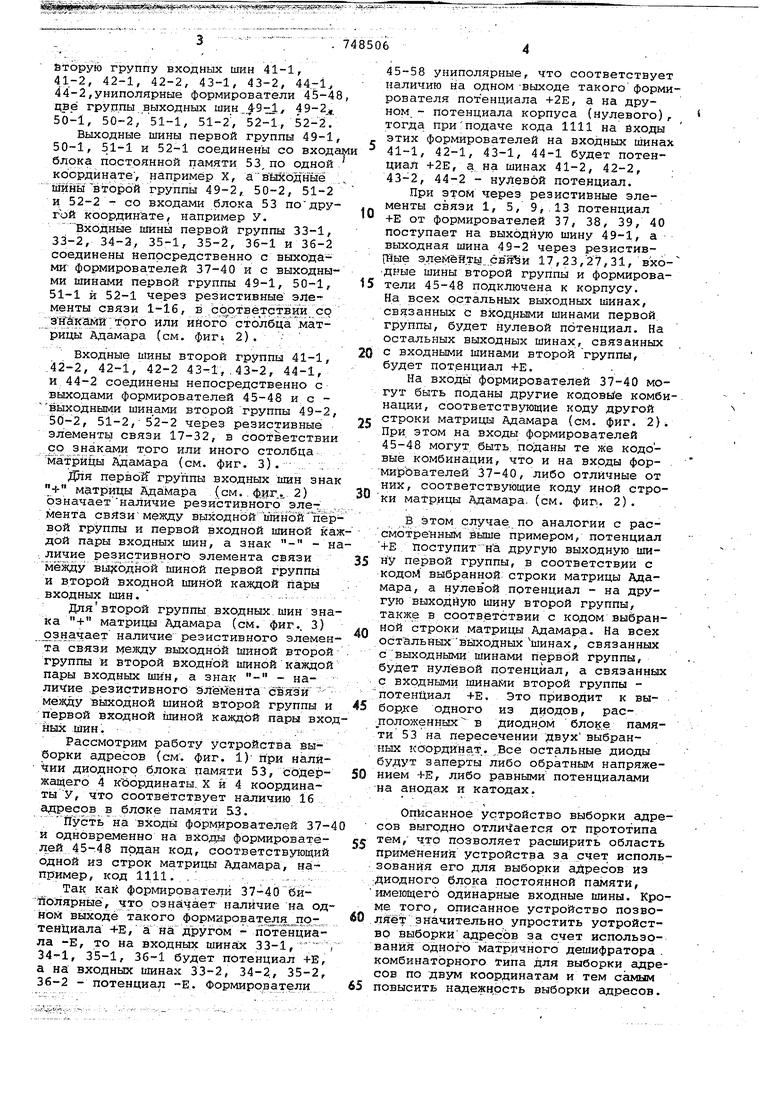

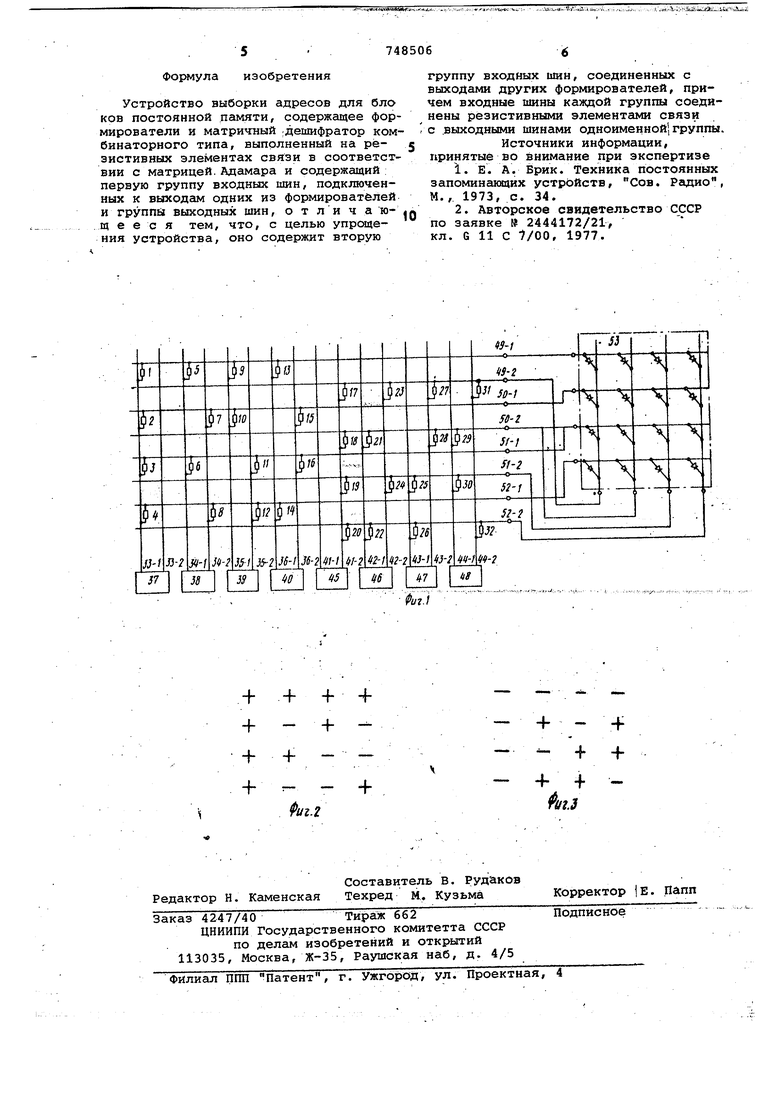

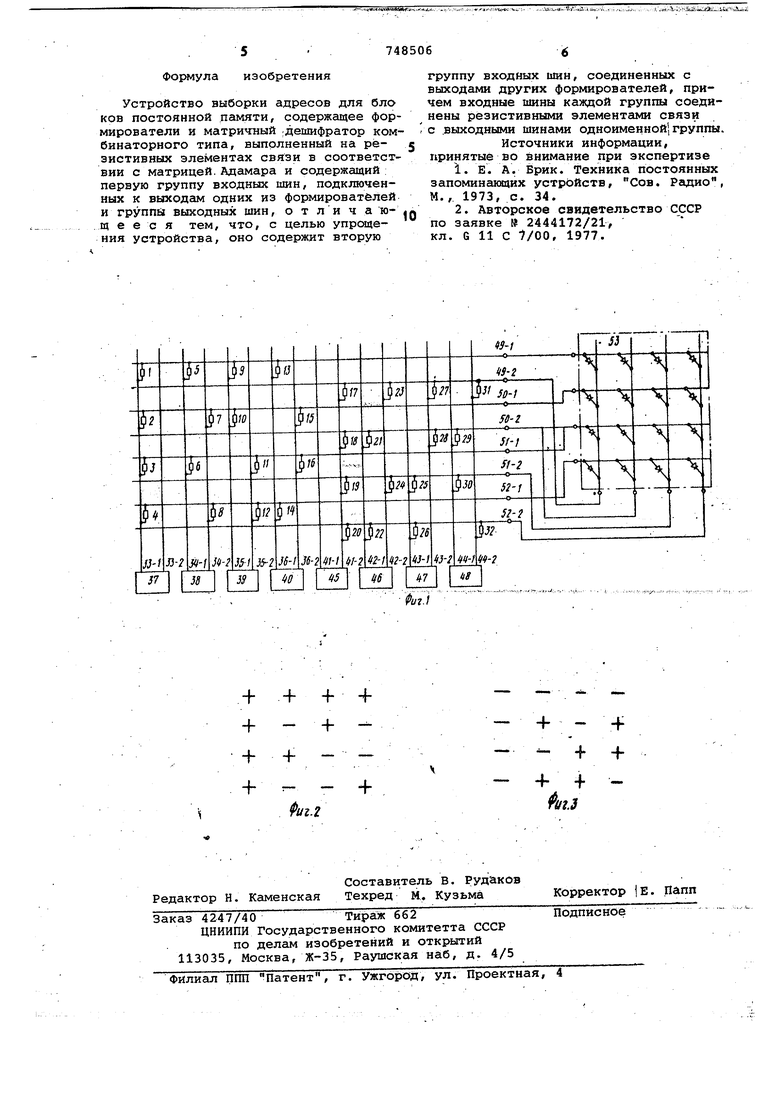

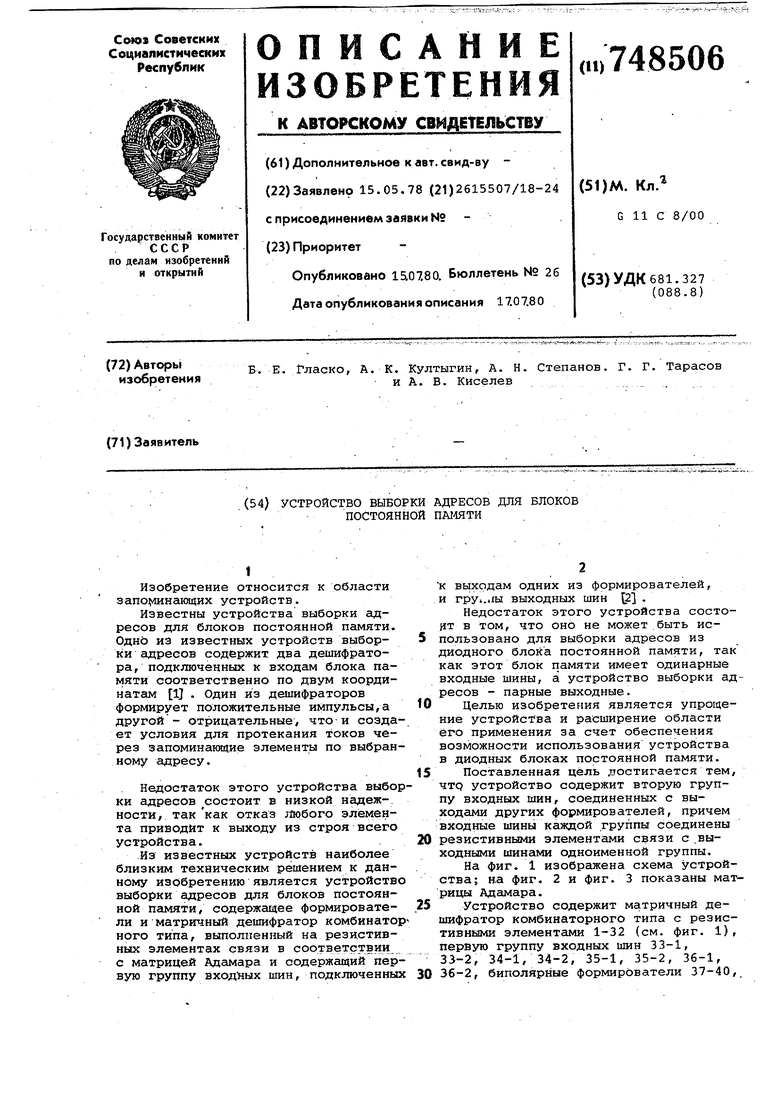

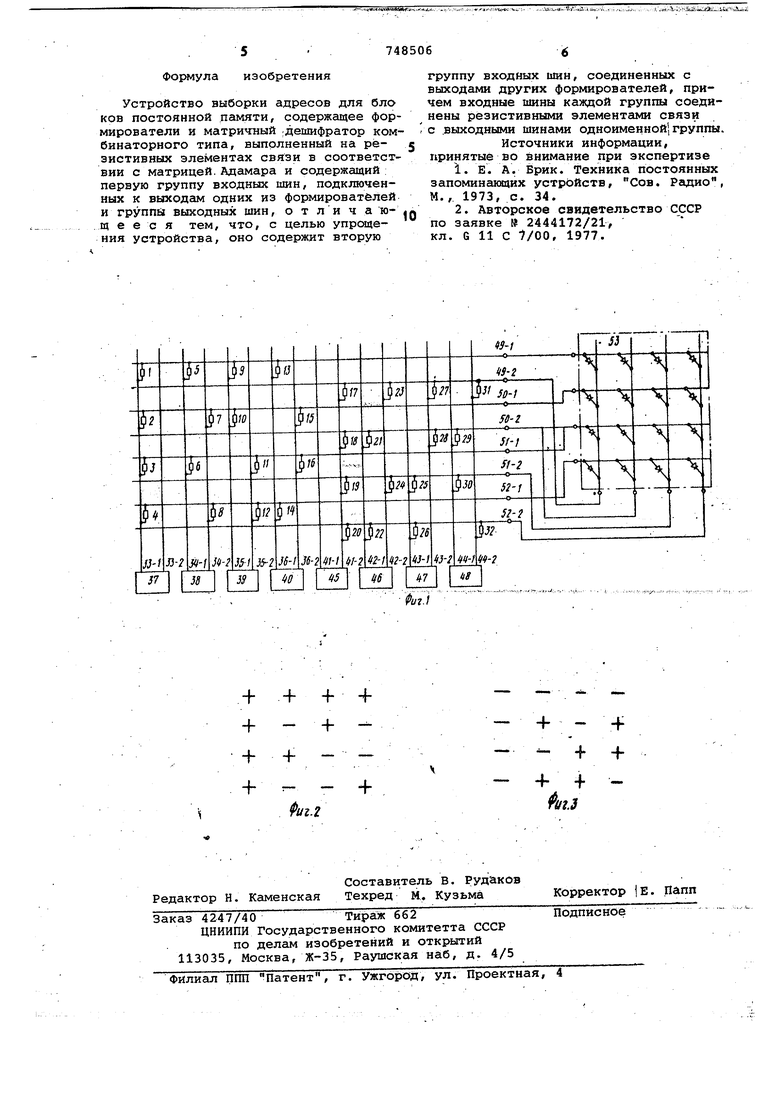

На фиг. 1 изображена схема устройства; н.а фиг. 2 и фиг. 3 показаны матрицы Адамара.

25 Устройство содержит матричный дешифратор комбинаторного типа с резистивными элементами 1-32 (см. фиг. 1), первую группу входных шин 33-1, 33-2, 34-1, 34-2, 35-1, 35-2, 36-1,

30 36-2, биполярные формирователи 37-40,.

748506 Вторую группу входных шин 41-1, 41-2, 42-1, 42-2, 43-1, 43-2, 44.г1 44-2,униполярные формирователи 45-48 цвё группы выходных шин 4-9-гДу 49-2 50-1, 50-2, 51-1, 51-2, 52-1, 52-2. Выходные шины первой группы 49-1, 50-1, 51-1 и 52-1 соединены со входа блока постоянной памяти 53, по одной координате , например X, а выхЬдныё шйны втор6й группы 49-2,. 50-2, 51-2 и 52-2 - со входами блока 53 подругой координате, например У. Входные шины первой группы 33-1, 33-2, 34-2, 35-1, 35-2, 36-1 и 36-2 соединены непосредственно с выходами- формирователей 37-40 и с выходными шинами первой группы 49-1, 50-1, 51-1 и 52-1 через резистивные элементы связи 1-16, в .содтветств ии. со знйКсМЙ того или ийого столбца матрицы Адамара (см. фиг 2) . Входные шины второй группы 41-1, .42-2, 42-1, 42-2 43-1,.43-2, 44-1, к 44-2 соединены непосредственно с выходами формирователей 45-48 и. с выходными шинами второй группы 49-2, 50-2, 51-2,52-2 через резистивные элементы связи 17-32, в соответствии со знаками того или иного столбца. матрйДы Адамара (см. фиг. 3). ... .; Для первой группы входных шин зна Ч- матрицы , (см.. фиг... 2) означаетналичие резистивногр эле-г,. .мента СВЯЗИмежду выходной шйнойпер вой группы и первой входной шиной ка дой пары входных шин, а знак - н . личие резистивного элемента связи между вы бдной шиной первой группы и второй входной шиной каждой пары входных шин. - Длявторой группы входных.шин зна ка + матрицы Адамара (см. фиг.. 3) о значает наличие резистивного элемен та связи между выходной шиной второй группы и второй входной шиной каждой пары входных шин, а знак - - наличие .резистивногб элементасвязй ; меаду выходной шиной второй группы и первой входной шиной каждой лары вхо ных .шин.. -. . Рассмотрим работу устройс1ва выборки адресов (см. фиг. 1) при налйЧии диодного блока памяти 53, содержащего 4 координаты, X и 4 координатыУ, что соответствует наличию 16 адресов в блоке памяти S3. Пусгьн.а ВХОДЫ формирователей 37и одновременно на входы формирователей 45-48 подан код, соответствующий одной из строк матрицы Адамара, например, код 1111. .Так как формирователи 37-40биЙолярныё, что рзнс1ча:ет наличие на од ном выходе такого формирователя,..по-, тенциала -fE, а на другом потенциала -Е, то на входных шина 33-1, 341, 35-1, 36-1 будет потенциал -fE, а на входных шинах 33-2, 34-2., 35-2, 36-2 - потенциал -Е. Формиро.ватели 45-58 униполярные, что соответствует наличию на одном -выходе такого формирователя потенциала +2Е, а на друном - потенциала корпуса (нулевого), тогда при:подаче кода 1111 на йходы этих формирователей на входных шинах 41-1, 42-1, 43-1, 44-1 будет потенциал +2Е, а на шинах 41-2, 42-2, 43-2, 44-2 - нулевой потенциал. При этом через резистивные элементы связи 1, 5, 9.13 потенциал +Е от формирователей 37, 38, 39,40 поступает на выходную шину 49-1, а выходная шина 49-2 через резистив Ные э.лемёЯты. 17,23,27,31,вхо- дные шины второй группы и формирователи 45-48 подключена к корпусу. На всех остальных выходных шинах, связанных с вход; ыми шинами первой, группы, будет нулевой потенциал. На остальных выходных шинах, связанных с входными шинами второй группы, будет пот.енциал +Е. На входы формирователей 37-40 могут быть поданы другие кодовы е крмби- . нации, соответствующие коду другой строки матрицы Адамара (см. фиг. 2), При. этом на входы формирователей 45-48 могут, быть. поДаны те же кодовые комбинации, что и на входы фор- . мирйвателей 37-40, либо отличные от них, соответствующие коду иной стро1си матр.ицы Адамара. (см. фиг. 2) . В этом случае, по аналогии с рассмотренным йыше примером, потенциал +Е Поступит на другую выходную шину первой группы, в соответствки с кодом выбранной строки матрицы Адамара, а нулевой потенциал - на другую выходную шину второй группы, также в соответствии с кодом выбранной строки матрицы Адамара. На всех ост альныхвь1хоДныхшинах, связанных с выходными, шинами первой, группы, будет нулевой потенциал, а связанных с входными шинами второй группы потенциал +Е. Это приводит к вы6opj e одного из дцодов, рас положенных в диодном блок.е. памяти53 на пересечении двух выбранных координат,. ...Все остальные диоды будут заперты либо обратным напряжением -НЕ, либо равными потенциалами на анодах и катодах. Описанное устройство выборки адресов выгодно отли Еается от прототипа тем, что позволяет расширить область применений устройства за счет использования его для выборки аДресов из :Диодного блрка постоянной памяти, имеющего Одинарные входные шины. Кроме того, описанное устройство позволяет значительно упростить устройство Выборки адресов за счет использования одного матричного дешифратора . комбинаторного типа для выборки адресов по двум координатам и тем самым повысить надежность выборки адресов. Формула изобретения Устройство выборки адресов для бло ков постоянной памяти, содержащее формирователи и матричный :дешифратор комбинаторного типа, выполненный на рёэистивных элементах связи в соответствии с матрицей. Адамара и содержащий : первую группу входных шин, подключенных к выходам одних из формирователей и группа выходных шин, о т л и ч а ющ е е с я тем, что, с целью упрощения устройства, оно содержит вторую

748506 группу входных шин, соединенных с выходами других формирователей, причем входные шины каждой группы соединены рёзистивными элементами связи с .выходными шинами одноименной , группы. Источники информации, принятые во внимание при экспертизе 1.Е. А. Брик. Техника постоянных запоминающих устройств, Сов. Радио, М., 1973, с. 34. 2.Авторское свидетельство СССР по заявке № 2444172/21, кл. G 11 С 7/00, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Дешифратор | 1977 |

|

SU750731A2 |

| Трансформаторный дешифратор комбина-ТОРНОгО ТипА C СуММиРОВАНиЕМНАпРяжЕНий | 1979 |

|

SU824301A1 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Шифратор | 1985 |

|

SU1298801A2 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU930656A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Тестер контроля и диагностики электронных модулей | 1986 |

|

SU1396099A1 |

| Устройство для регенерации информации в динамической памяти | 1983 |

|

SU1193729A1 |

Авторы

Даты

1980-07-15—Публикация

1978-05-15—Подача