О)

00

«

со

11437913

Изобретение относится к вычислиельной технике, в частности к интегальным биполярным схемам оперативой памяти.

Целью изобретения является повышеие надежности и увеличение быстроействия усилителя.

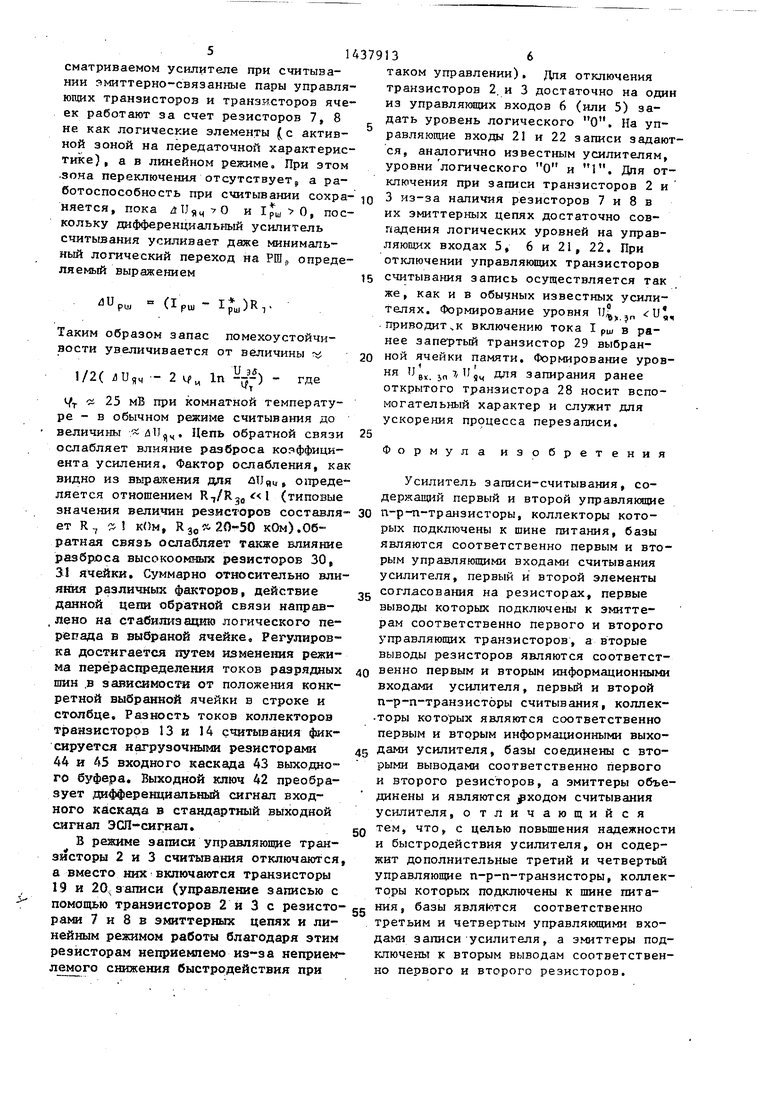

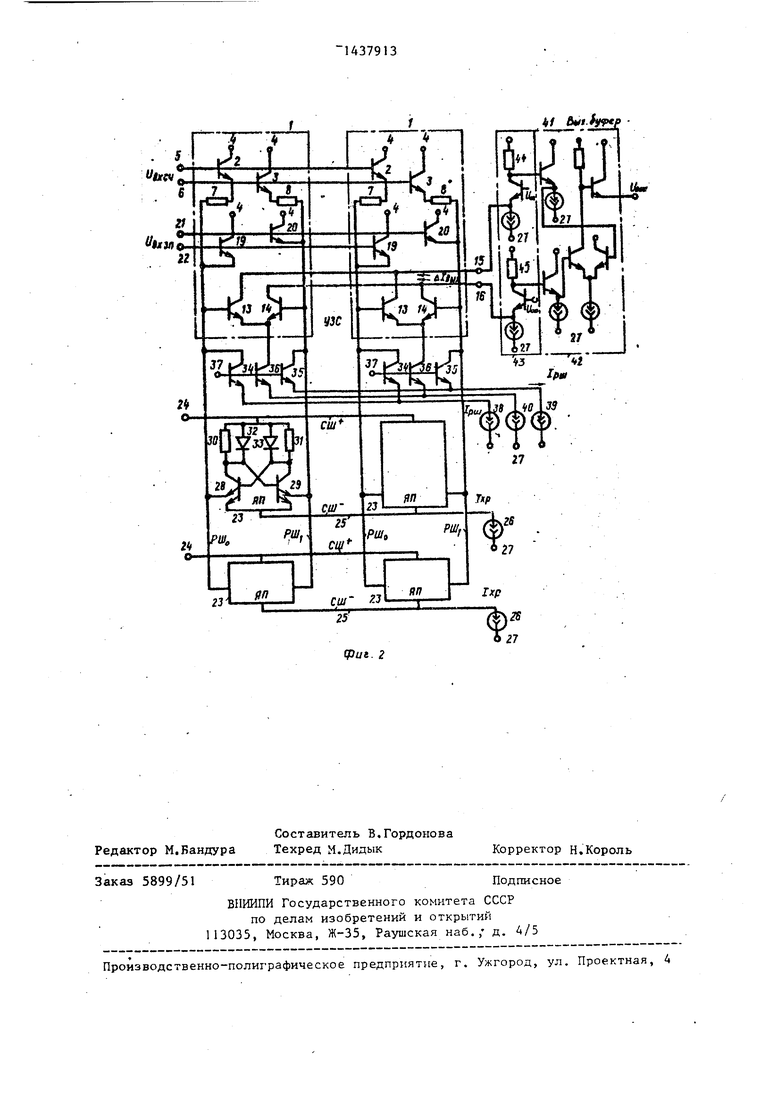

На фиг,I представлена принципиальая электрическая схема предлагаемо- jg о усилителя; на фиг,2 - электричесая схема усилителя с частью накопиеля и выходного буфера для пояснеия его работы.

к го

пр ща ны в ве ши вт ди ры ко сл ны не от яч вт 28 ля ра вт ва ро со ми во сл об по не во во ро це ти и со ря му не ра

Усилитель записи-считывания (фиг. содержит группу разрядных элементов I, каждый разрядный элемент 1 включает первый 2 и второй 3 управляющие п-р-п-транзисторы, коллекторы которых подключены к шине А питания, базы, объединенные соответственно с базами одноименных транзисторов остальных разрядных элементов 1, являются соответственно первым 5 и вторым 6 управляюпщми входами считывания усройства, первый 7 и второй 8 резисторы, первые выводы которых подключены к эмиттерам соответственно первого и второго 2 и 3 управляющих транзисторов, вторые их выводы являются соответственно первым 9 и вторым 10 информационными входами данного разрядного элемента 1, подключенными соответственно к первой 11 и второй 12 разрядным шинам соответствующего разряда накопителя, первый 13 и второй 14 п-р-п-транзисторы считывания, коллекторы которых, объединенные соответственно с коллектора В1 одноименных транзисторов остальных разрядных элементов 1, являются соответственно первым 15 и вторым 16 информационными выходами устройства, базы

g

0

5

5

5

0

0

к вторым выводам соответственно первого 7 и второго 8 резисторов.

На фиг,2 совместно с усилителями приведена часть накопителя, содержа-, щая матрицу ячеек памяти 23, разрядные первые и вторые выводы которых в каждом столбце объединены соответственно первыми и вторыми разрядными шинами 11 и 12, словарные первые и вторые выводы в каждой строке объединены соответственно первыми и вторыми 24 и 25 словарными шинами, из которых первые являются также входами словарной выборки, а вторые подключены к выходам источников 26 тока хранения, входы которых подключены к отрицательной шине 27 питания, каждая ячейка памяти 23 включает первый и второй двухэмиттерные транзисторы 28 и 29, первьге эмиттеры которых являются соответственно первым и вторым разрядньтми вьгеодами, а объединенные вторые эмиттеры являются вторым словарным выводом, а также первый и второй резисторы 30 и 31, шунтированные соответственно первым и вторым диодами 32 и 33, объединенные первые выводы и аноды которых являются первым словарным выводом, а соответственно объединенные вторые выводы и катоды подключегЫ соответственно к объединенным базе второго и коллектору первого транзисторов 29 и 28 и базе первого и коллектору второго транзисторов 28 и 29, в каждом разряде (столбце) содержатся первый, второй и третий коммутирующие транзисторы 34,35 и 36, коллекторы которых подключены соответственно к первой и второй разрядным шинам П и 12 и шине.18 коммутирующего тока считывания, объединенные базы являются входом 37 разрядной выборки, а эмиттеры, соот

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1111204A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1991 |

|

RU2020614C1 |

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Элемент памяти | 1989 |

|

SU1679552A1 |

Изобретение относится к вычислительной технике, в частности к интегральным биполярным схемам оперативной памяти. Целью изобретения является повышение надежности и увеличение быстродействия усилителя. Усилитель записи-считывания содержит группу разрядных, элементов I, каждый из которых включает управляющие транзисторы 2 и 3 п-р-п-типа, шину 4 питания, резисторы 7,8, разрядные шины 11,12, п-р-п-транзисторы 13,14 считывания, управляющие п-р-п-транзисторы 19 20. 2 ил.

50

подключены к вторым выводам соответст-45 ветственно объединенные с эмиттерами венно первого 7 и второго 8 резисторов, а объединенные эмиттеры являются входом 17 считывания данного разрядного элемента 1, подключенным к шине 18 коммутируемого тока считывания, третий 19 и четвертый 20 управляющие п-р-п-транзисторы, коллекторы которых подключены к шине 4 питания, базы, объединенные соответственно с базами одноименных транзисторов остальных разрядных элементов 1, являются соответственно третьим 2 и четвертым 22 управляющими входами записи устройства, эмиттеры подключены

55

одноименных транзисторов других разрядов, подключены к выходам соответственно первого и второго источников разрядного тока и тока считывания 38, 39 и. 40, входы которых подключены к отрицательной шине питания. Приведенная часть выходного буфера 41 содержит выходной ЭСГ1-ключ 42 с дифференциальным входом и входной каскад 43, включающий первый н второй резисторы 44 и 45 нагрузки, первые выводы которых подключены к шине 4 питания , вторые выводы подключены к входам выходного ЭСЛ-ключа 42.

ветственно объединенные с эмиттерами

одноименных транзисторов других разрядов, подключены к выходам соответственно первого и второго источников разрядного тока и тока считывания 38, 39 и. 40, входы которых подключены к отрицательной шине питания. Приведенная часть выходного буфера 41 содержит выходной ЭСГ1-ключ 42 с дифференциальным входом и входной каскад 43, включающий первый н второй резисторы 44 и 45 нагрузки, первые выводы которых подключены к шине 4 питания , вторые выводы подключены к входам выходного ЭСЛ-ключа 42.

314

Усилитель работает следующем образом.

В режиме считывания он взаимодействует с ячейкой, расположенной в выбранной строке с высоким потенциалом по шине 2А и в выбранном разряде, в разрядные шины которого по сигналу по шине 37 разрядной выборки транзисторами 34, 35 коммутируются разряд ные токи, В выбранный разряд аналогично коммутируется также и ток считывания . На управлякщие входы 5 и 6 считывания задается высокий логический уровень Uj, (., , равный высокому логическому уровню И.сц, выбранной словарной шины 24, На управляющие входы записи 21 и 22 задается некоторый средний уровень П. о ср , который выбирается в пределах

L «,ьп..сч

в рассматриваемом режиме считывания в соответствии с приведенным неравен- ством управляюгцие транзисторы 19 и 20 записи в статическом со стоянии заперты. Включаются они только в переходном режиме (смене адресов строк или столбцов, йереход к режиму запи- си или обратно) при появлении отрицательных выбросов по разрядным шинам. При включении данные транзисторы фиксируют потенциал разрядных шин и предотвращают снижение его ниже уровня Uj.jn. ср- Uj,,, (Здесь и далее И 5, „- прямое падение напряжения на эмиттер- ном переходе транзистора с номером позиции на чертеже, соответствующим индексу). Логические уровни 1 на словарных шинах 24 и управляющих входах 5 и6 считывания Uj, не требуют стабилизации, поскольку задаются от стабильного потенциала шины 4 питания (со сдвигом уровня на эмиттерном пов- торителе).В соответствии с приведенным равенством ток Т., одной из РШ (например, второй 12, в выбранной ячейке соответственно транзистор 28 открыт, а 29 - закрыт) протекает в управляющий транзистор 3. Ток другой разрядной шины П делится между управляющим транзистором 2 и транзистором 28 ячейки. Величина тока 1 , протекающего в ячейку, определяется соотношением

,,t(tv.- О 5зм Г;г1

где RJ, Rj - величина резисторов с

номером позиции на чертеже, соответствующим индексу; р„ - коэффициент усиления

транзисторов.

С учетом этого ссютнощения, пренебрегая разностью величин U, , завися03

щих от тока, и принимая во внимание Pf,7 l, логический перепад в выбранной ячейке будет выражаться как

U

«ч

и;. - и,%

и

R 7 I РШ

АИ-З

1 +

R

30

где падение напряжения на открытом ijMKCnpyK 5eM диоде 32 в ячейке. В обычном известном режиме выборки,

используемом и в приведенных аналогах

и прототипе, логический перепад в

ячейке

UA I pui R 51 сильной степени зависит от разброса сопротивления в ячейке R и технологического разброса и температурного ухода коэф циента усиления р. Управляю1 щй транзистор считывания и транзистор ячейки в этом случае работают как эмиттерно-связанная пара в ЭСЛ-ключе. Ток одной из РШ полностью протекает в ячейку, другой - в управляющий транзистор. Такое распределение токов достигается соответствукяцим выбором потенциала .cv относительно потенциалов в ячейке. Корректирующий резистор в эмиттерной цепи управляющего транзистора (типовое значение 0,1 кОм) не изменяет данного распределения токов, а только немного-увеличивает ширину активной зоны переключения в упомянутых эмиттерно-связан ньдх парах и уменьшает крутизну передаточной характеристики в этих зонах. Запас помехоустойчивости, определяемой величиной AUj, за вычетом щири- ны активной зоны с учетом зависимости от разброса R, и /ь , имеет существенно меньшее значение, чем в стандартных ЭСЛ, и на надежность считывания оказывает влияние soпротивление шин металлизации и другие факторы, зависящие от положения выбранной ячейки в строке и столбце. В рассматриваемом усилителе при считывании эмиттерно-связанные пары управляющих транзисторов и транзисторов ячеек работают за счет резисторов 7, 8 не как логические элементы (с активной зоной на передаточной характеристике) , а в линейном режиме. При этом зона переключения отсутствует5 а работоспособность при считывании сохра- Q 3 из-за наличия резисторов 7 и 8 в

их эмиттерных цепях достаточно совладения логических уровней на управляющих входах 5, 6 и 21, 22. При отключении управляющих транзисторов считывания запись осуществляется так

таком управлении). Для отключения транзисторов 2, и 3 достаточно на один из управляющих входов 6 (или 5) задать уровень логического О. На управляющие входы 21 н 22 записи задают ся, аналогично известным усилителям, уровни логического О и 1. Дпя отключения при записи транзисторов 2 и

няется, пока и , поскольку дифференциальный усилитель считьшания усиливает даже минимальный логический переход на РШд определяемый выражением

15

ли

PLU

(I рш Ipuj) 7

Таким образом запас помехоустойчивости увеличивается от величины

и Э5ч

1/2( лияя - 2 „ In -) где

-

t/T- 25 мВ при комнатной температуре - в обычном режиме считывания до величины «ДПд. Цепь обратной связи ослабляет влияние разброса коэффициента усиления. Фактор ослабления, как видно из вьфажения для Пяц, определяется отношением (типовые значения величин резисторов составляет R-, кОм, R3(1% 20-50 кОм).Обратная связь ослабляет также влияние разбрдсз высокоомных резисторов 30, 31 ячейки. Суммарно относительно влияния различных факторов, действие данной цепи обратной связи направлено на стабилизацию логического перепада в выбракой ячейке. Регулировка достигается путем измене1шя режима перераспределения токов разрядных шин .в зависимости от положения конкретной выбранной ячейки в строке и столбце. Разность токов коллекторов транзисторов 13 и 14 считывания фик- онруется нагрузочными резисторами 44 и 45 входного каскада 43 выходного буфера. Выходной ключ 42 преобразует дифференциальный сигнал входного каскада в стандартный выходной сигнал ЭСП-сигнал,

В режиме записи управляющие транзисторы 2 и 3 считывания отключаются, а вместо них включаются транзисторы 19 и 20. записи (управление записью с

25

. Wi запирания ранее открытого транзистора 28 носит вспо могательный характер и служит для ускорения процесса перезаписи.

Формула изобретени

Усилитель записи-считывания, содержащий первый и второй управляющи

30

35

п-р-п-транзисторы, коллекторы которых подключены к шине питания, базы являются соответственно первым и вт рым управляющими входами считывания усилителя, первый и второй элементы согласования на резисторах, первые выводы которых подключены к эмиттерам соответственно первого и второг управляющих транзисторов, а вторые выводы резисторов являются соответс

40 венно первым и вторым информационны входами усилителя, первый и второй п-р-п-транзист6ры считывания, колле торы которых являются соответственн первым и вторым информационными вых

45 дами усилителя, базы соединены с вт рыми выводами соответственно первог и второго резисторов, а эмиттеры об динены и являются уходом считывания усилителя, отличающийся тем, что, с целью повьш1ения надежно и быстродействия усилителя, он соде жит дополнительные третий и четверт управляющие п-р-п-транзисторы, колл торы которых подключены к шине пита

50

помощью траизисторов 2 и 3 с резисто- gg ния, базы является соответственно

рами 7 и 8 в змиттериых цепях и линейным режимом работы благодаря этим резисторам неприемлемо из-за неприемлемого снижения быстродействия при

третьим и четвертым управляющими вх дами записи усилителя, а эмиттеры п ключены к вторым выводам соответств но первого и второго резисторов.

3 из-за наличия резисторов 7 и 8 в

таком управлении). Для отключения транзисторов 2, и 3 достаточно на один из управляющих входов 6 (или 5) задать уровень логического О. На управляющие входы 21 н 22 записи задаются, аналогично известным усилителям, уровни логического О и 1. Дпя отключения при записи транзисторов 2 и

же, как и в обычных известных усилителях. Формирование уровня ц приводит,к включению тока Iрш в ранее запертый транзистор 29 выбранной ячейки памяти. Формирование уров . Wi запирания ранее открытого транзистора 28 носит вспомогательный характер и служит для ускорения процесса перезаписи.

Формула изобретения

Усилитель записи-считывания, содержащий первый и второй управляющие

п-р-п-транзисторы, коллекторы которых подключены к шине питания, базы являются соответственно первым и вторым управляющими входами считывания усилителя, первый и второй элементы согласования на резисторах, первые выводы которых подключены к эмиттерам соответственно первого и второго управляющих транзисторов, а вторые выводы резисторов являются соответственно первым и вторым информационными входами усилителя, первый и второй п-р-п-транзист6ры считывания, коллек- торы которых являются соответственно первым и вторым информационными выходами усилителя, базы соединены с вторыми выводами соответственно первого и второго резисторов, а эмиттеры объе- динены и являются уходом считывания усилителя, отличающийся тем, что, с целью повьш1ения надежности и быстродействия усилителя, он содержит дополнительные третий и четвертый управляющие п-р-п-транзисторы, коллекторы которых подключены к шине пита

ния, базы является соответственно

третьим и четвертым управляющими входами записи усилителя, а эмиттеры подключены к вторым выводам соответственно первого и второго резисторов.

. 5 rj

Wlrcvl

(li,M

(put. 2

/jfttrtj J V

| Патент ОПА 4078261, кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| IEEE J | |||

| of Solid-state Circuits, 1984, V | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПРИСПОСОБЛЕНИЕ ДЛЯ УСТРАНЕНИЯ СКОЛЬЖЕНИЯ КОЛЕС АВТОМОБИЛЕЙ | 1920 |

|

SU292A1 |

| (прототип). | |||

Авторы

Даты

1988-11-15—Публикация

1986-12-10—Подача