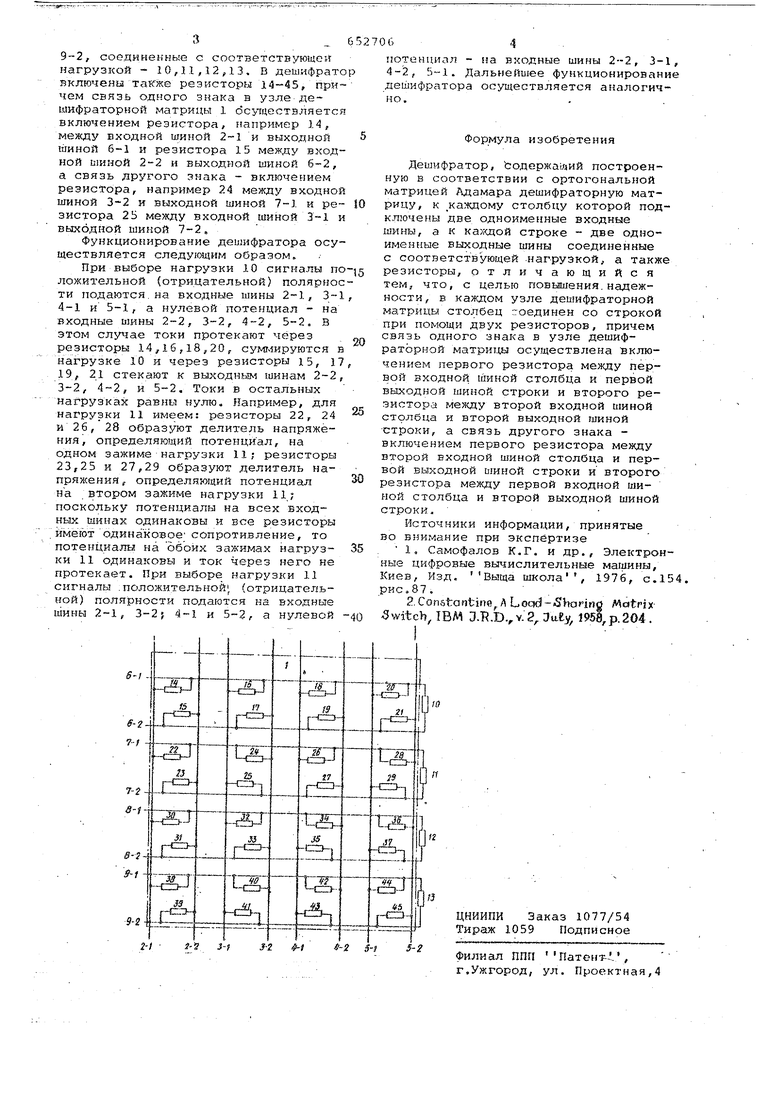

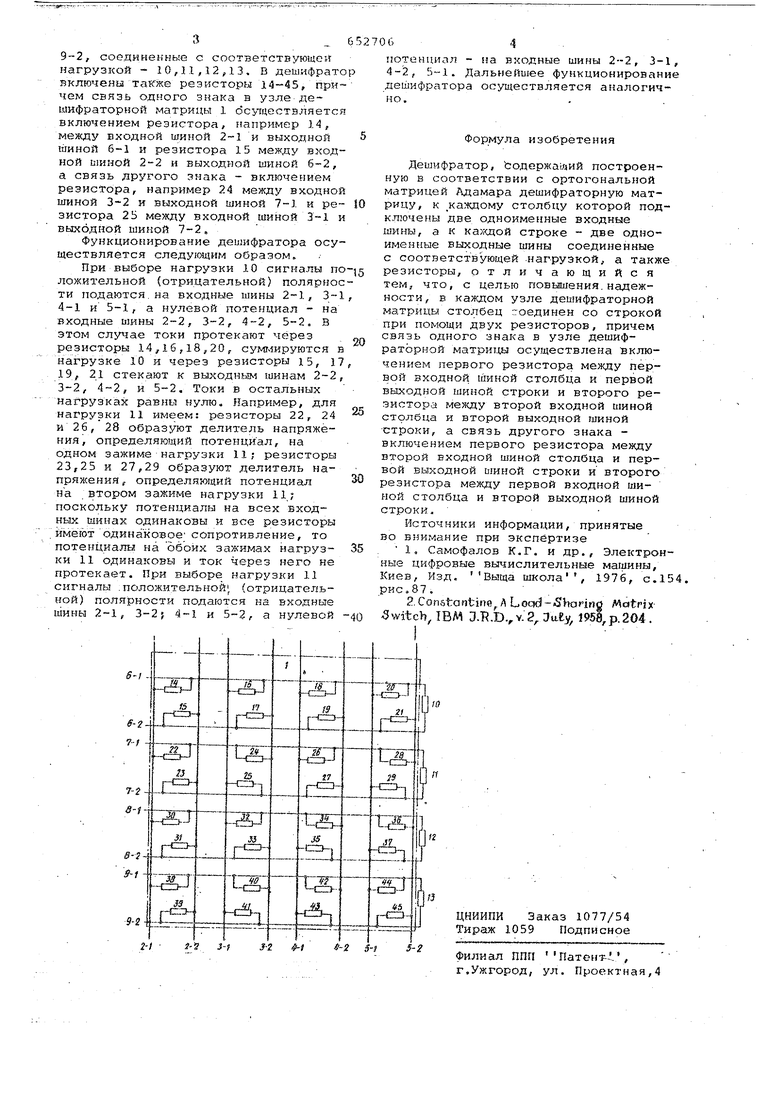

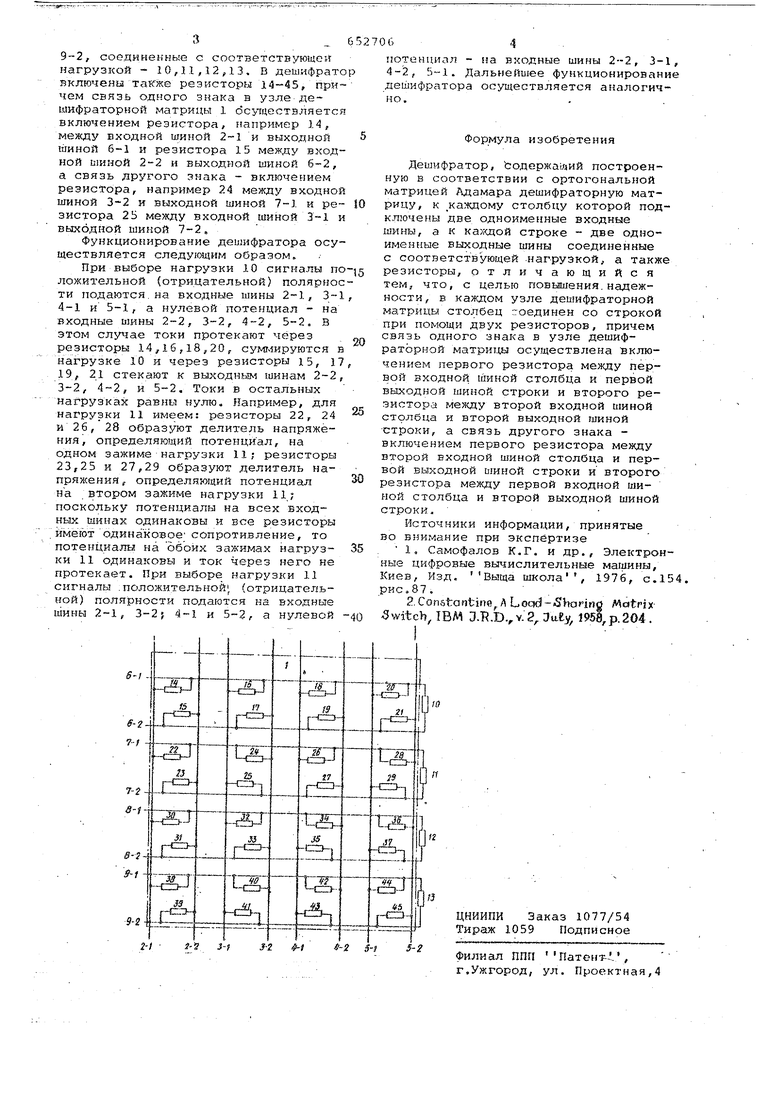

Изобретение относится к области автоматики и вычислительной техники и предназначено для использования в запоминающих устройствах. Известны дешифраторы, в которых связи между входными и выходными ши нами дешифраторнойматрицы осуществ ляются при помоади диодов 1. К недо1гтаткам этих дешифраторов относится низкая надежность. Наиболее близким техническим решением к изобретению яйляетсйдешифратор, содержащий построенную в соответствии с ортогональной матрицей Адамара дешифраторную матоицу .к каждому столбцу которой подключены две одноименные входные шины, а к каждой строке - две одноименные выходные шины, соединенные с соотве ствующей нагрузкой, а также резисто ры 2. Недостатком их также являет ся низкая надежность. Цель-изобретения - повышение надежности дешифратора. Указанная цель достигается тем, что в дешифраторе, содержащем построенную в соответствии с ортогональной матрицей Адамара дешифраторную матрицу, к каждому столбцу которой подключены две одноименные входные шины, а к каждой строке две одноименньзе выходные шины, соединенные с соответствующей нагрузкой, а также резисторы, в каждом узле дешифраторной матрицы столбец соединен со строкой при помощи двух резисторов, причем связь одного знака в узле дешифраторной матрицы осуществлена включейием первого резистора между первой входной шиной столбца и первой выходной шиной строки и второго резистора между второй входной шиной столбца и второй выходной шиной строки, а связь другого знака - включением первого резистора между второй входной шиной столбца и первой выходной шиной строки и второго резистора между первой входной шиной столбца и второй выходной шиной строки. Принципиальная схема дешифратора представлена на чертеже и содержит дешифраторную матрицу 1, построенную в соответств,ии с ортогональной матрицей Адамара, к каждому столбцу которой подключены две одноименные входные шины: 2-1, 2-2, 3-1, 3-2, 4-1, 4-2, 5-1, 5-2, а к каждой строке - дре одноименные выходные шины 6-1, 6-2, 7-1, 7-2, 8-1, 8-2, 9-1, 9-2, соединенные с соответствующей нагрузкой - 10,11,12,13. В дешифрато включены также резисторы 14-45, причем связь одного знака в узле де шифраторной матрицы 1 ос 1цествляется включением резистора, например 14, между входной 2-1 и выходной шиной 6-1 и резистора 15 между входной тиной 2-2 и выходной шиной 6-2, а связь лругого знака - включением резистора, например 24 между входной шиной и выходной шиной 7-1 и резистора 25 между входной шиной 3-1 и выходной шиной 7-2, Функционирование дешифратора осу ществляется следующим образом. При выборе нагрузки 10 сигналы no ложительной (отрицательной) полярнос ти подаются, на. входные шины 2-1, 3 4-1 и 5-1, а нулевой потенциал - на в.ходные шины 2-2, 3-2, 4-2, 5-2. В этом случае токи протекают через резисторы 14,16,18,20, сумг-шруются в нагрузке 10 и через резисторы 15, 1 19, 2Д стекают к выходным шинам 2-2 3-2, 4-2, и 5-2. Токи в остальных Нагрузках равны нулю. Например, для нагрузки 11 имеем: резисторы 22, 24 и 26, 28 образуют делитель напряжения, определяющий потенциал, на одном зажиме нагрузки 11; резисторы 23,25 и 27,29 образуют делитель напряжения, определяющий потенциал на втором зажиме нагрузки 11; поскольку потенциалы на всех входных шинах одинаковы и все резисторы . ймёгот одинаковое сопроти.вление, то потенциалы на обоих зажимах нагрузки 11 одинаковы и ток через него не протекает. При выборе нагрузки 11 сигналы .положительной; (отрицательной) полярности подаются на входные шины 2-1, 3-2f и 5-2, а нулевой потенциал - на входные шины 2--2, 3-1, 4-2, 5-1. Дальнейшее функционирование дешифратора осуществляется аналогично. Формула изобретения Дешифратор, Ьодержа1 дий построенную в соответствии с ортогональной матрицей Адамара дешифраторную матрицу, к каждому столбцу которой подключены две одноименные входные шины, а к ка)адой строке - две одноименвше выходные шины соединенные с соответствующей .нагрузкой, а также резисторы, отличающийся тем, что, с целью повышения, надежности, в каждом узле дешифраторной матрицы столбец соединен со строкой при помощи двух резисторов, причем связь одного знака в узле дешифраторной матри1.1Ы осуществлена включением первого резистора между первой входной шиной столбца и первой выходной шиной строки и второго резистора между второй входной шиной столбца и второй выходной шиной -строки, а связь другого знака включением первого резистора между второй входной шиной столбца и первой В.ЫХОДНОЙ шиной строки и второго резистора между первой входной шиной столбца и второй выходной шиной строки. Источники информации, принятые во внимание при экспертизе 1о Самофалов К.Г. и др.. Электронные цифровые вычислительные машины, Киев, Изд. Выща школа , 1976, с.154. рис.87, 2. Consirantine A Load-«Sbaring MatrjX Switch, ША Э.Т.В.,-.г aiiRy, 1958,p.204.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1977 |

|

SU750731A2 |

| Устройство выборки адресов для блоков постоянной памяти | 1978 |

|

SU748506A1 |

| Дешифратор | 1987 |

|

SU1564732A1 |

| Трансформаторный дешифратор комбина-ТОРНОгО ТипА C СуММиРОВАНиЕМНАпРяжЕНий | 1979 |

|

SU824301A1 |

| АНАЛИЗАТОР ФУНКЦИЙ УОЛША | 2000 |

|

RU2203504C2 |

| Матричный дешифратор для комбинаторного переключателя | 1977 |

|

SU696539A1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЙ УОЛША (ЕГО ВАРИАНТЫ) | 2000 |

|

RU2203506C2 |

| УСТРОЙСТВО ДЛЯ ОБРАТНОГО ПРЕОБРАЗОВАНИЯ УОЛША (ЕГО ВАРИАНТЫ) | 2000 |

|

RU2203505C2 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Устройство для контроля и сигнализации | 1990 |

|

SU1795494A1 |

Авторы

Даты

1979-03-15—Публикация

1977-01-17—Подача