1

Предлагаемое изобретение относится к автоматике и вычислительной технике, может быть использовано в запоминающих и других устройствах цифровых вычислительных машин.

Известны матричные дешифраторы, содержащие входные формирователи, подк.шоченные ко входным шинам дешифраторной матрицы, и нагрузки, подключенные к выходным шинам 1.

Наиболее близок к предлагаемому матричный дешифратор, содержащий формирователи токов и m дешифраторных матриц 2,

В каждой из нагрузок этого дешифратора складывается энергия только некоторой части входных формирователей, что понижает надежность схемы.

Цель изобретения - повышение надежности дешифратора.

Поставленная цель достигается тем что в матричный дешифратор введено п дополнительных дешифраторных матриц, входы которых соединены с соответствующими выходами формирователей токов, а выходы каждой дополнительной матрицы соединены с соответствующими входами основных матриц.

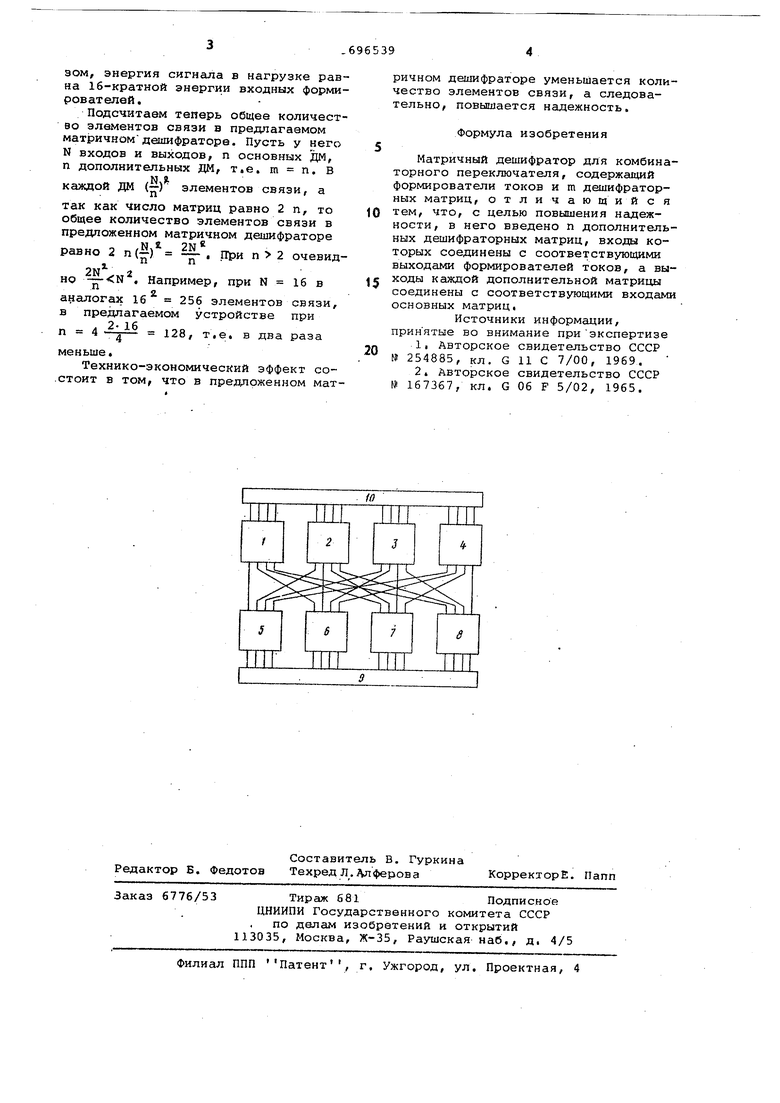

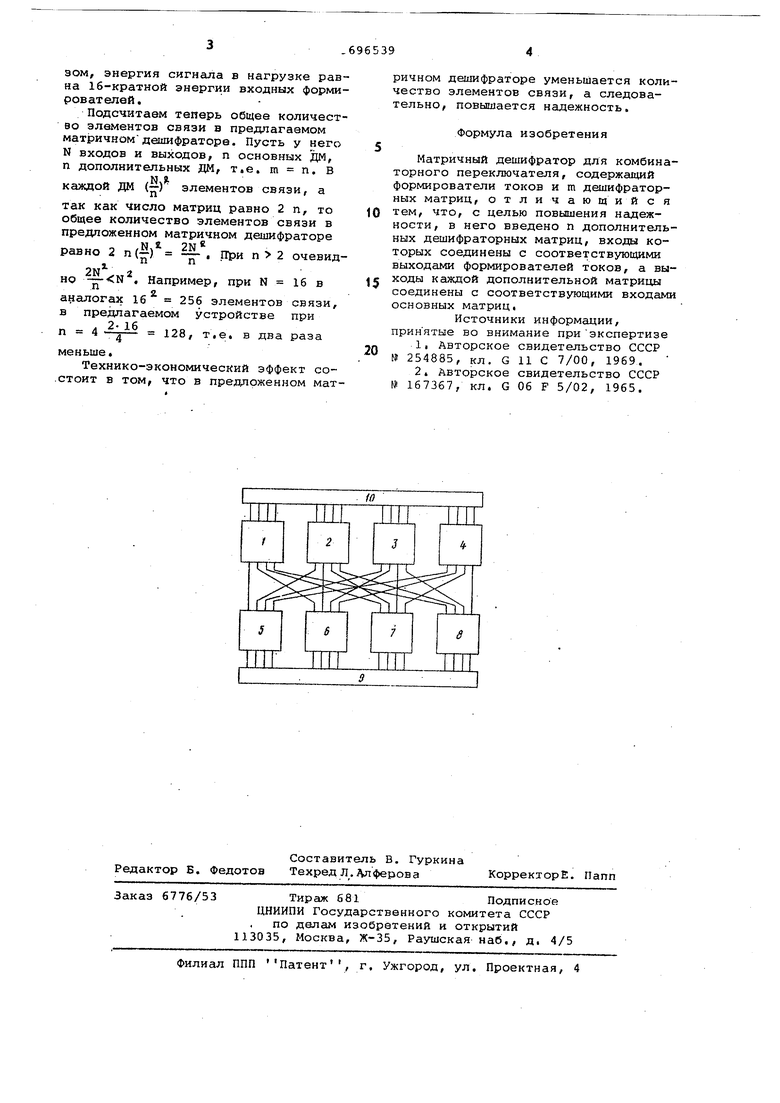

На черт-еже приведена структурная электрическая схема устройства.

Матричный дешифратор содержит основные дешифраторные матрицы 1-4, дополнительные дешифраторные матрицы Ь-8, формирователи токов 9,блок нагрузок 10.

Предположим, каждая дешифраторная матрица имеет четыр.е входа и выхода. Тогда ко входам каждой из дополнительных матриц подключены четыре

0 входных формирователя, а общее их количество равно 16. К выходам каждой основной дешифраторной матригул (ДМ) подклюгтены 4 нагрузки, а всего к выходам основных ДМ подключено 16

5 нагрузок.

Входные форм111рователи формируют на входных шинах дополнительных ДМ соответствующие сигна.лы, так что их энергия складывается на одноименных

0 выходах каждой из матриц.

Поскольку все эти выходы соединены со входами каждой из основных ДМ, каждый входной сигнал этой матрицы объединяет энергию четырех ЕХОДНЫХ

5 формирователей. Полярность входных сигналов выбранной основной ДМ должна быть при этом такова, чтобы энергия всех входных сигналов сложилась в одной из нагрузок, подк.пюченных к

0 ыходам данной матрицы. Таким обраэом, энергия сигнала в нагрузке равна 16-кратной энергии входных формирователей.

Подсчитаем теперь общее количество элементов связи в предлагаемом матричном дешифраторе. Пусть у него N входов и выходов, п основных ДМ, п дополнительных ДМ, т.е. m п. В

N каждой ДМ (-) элементов связи, а

так как число матриц равно 2 п, то общее количество элементов связи в предложенном матричном деишфраторе

N t 2N равно 2 пф . Прк п 2 очевид2м 2 но , Например, при N 16 в

аналогах 16 256 элементов связи, в предлагаемом устройстве при

2« 16 П 4 128, т.е. в два раза

меньше.

Технико-экономический эффект со.стоит в том, что в предложенном матричном дешифраторе уменьшается количество элементов связи, а следовательно, повышается надежность.

Формула изобретения

Матричный дешифратор для комбинаторного переключателя, содержащий формирователи токов и m дешифраторных матриц, отличающийся тем, что, с целью повышения надежности, в него введено п дополнительных дешифраторных матриц, входы которых соединены с соответствующими выходами формирователей токов, а выходы каждой дополнительной матрицы соединены с соответствующими входами основных матриц.

Источники информации, принятые во внимание при экспертизе

1I Авторское свидетельство СССР № 254885, кл. G 11 С 7/00, 1969.

2. Авторское свидетельство СССР № 167367, кл. G 06 F 5/02, 1965.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1977 |

|

SU750731A2 |

| Дешифратор | 1977 |

|

SU652706A1 |

| Дешифратор | 1987 |

|

SU1564732A1 |

| Устройство выборки адресов для блоков постоянной памяти | 1978 |

|

SU748506A1 |

| Коммутационное устройство | 1985 |

|

SU1307573A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА СИГНАЛОВ КОМАНДНОЙ МАТРИЦЫ | 2011 |

|

RU2487393C1 |

| МАТРИЧНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 2016 |

|

RU2727767C1 |

| Формирователь матричных команд | 2018 |

|

RU2707913C1 |

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

Авторы

Даты

1979-11-05—Публикация

1977-05-12—Подача