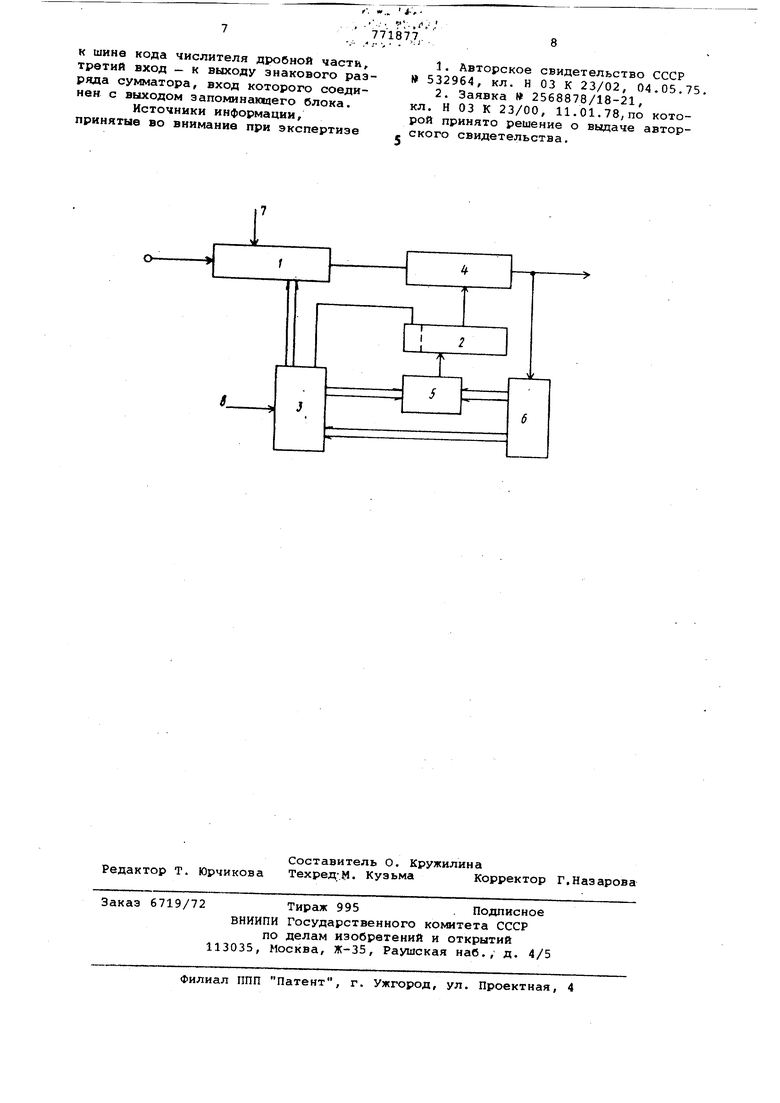

Изобретение относится к импульсно технике и может использоваться в аппаратуре времени и эталонных частот, в синтезаторах частот радиоприемных радиопередающих устройств. Известно устройство, содержащее делитель с целочисленным коэффициентом и блок статистических испытаний Щ Недостатком данного устройства яв ляется его сложность и вследствие этого низкая надежность. Известно также устройство для деления частоты следования импульсов с дробным коэффициентом деления, содер жащее делитель частоты с переменным коэффициентом деления, установочные входы которого подключены к шине вво да кода целой части коэффициента деления, а выход - к входу считывания элемента сравнения кодов, первый выход которого подк.шочен к входу считы вания первого сумматора и к входу ус тановки нуля второго сумматора, второй выход - к входу установки нуля первого сумматора, к входу считывания второго сумматора и к входу делителя частоты с переменным коэффициентом деления, счетный вход которого соединен с входной шиной, при этом выход первого сумматора подключен к первому входу делителя сравнения кодов и к первому информационному входу второго сумматора, а вторые информационные входы первого и второго сумматоров подключены к шинам ввода соответственно кода числителя дробного коэффициента деления и кода разности знаменателя и числителя дробного коэффициента деления, выход делителя частоты с целочисленным коэффициентом деления подключен к входу блока квантованной задержки, вход включения которого соединен с его выходом, а первый и второй установочные входы соединены соответственно с выходами первого и второго сумматоров 23 . Недостатком описанного устройства является его относительно низкая надежность, вызванная его сложностью. Так, например, если коэффициент деления устанавливается с шагом 0,001 ( Jb 1000) , то сумматоры должны быть 12 разрядными {для хранения чисел в пределах от -1500 до +1500), элемент сравнения кодов и сумматор блока квантованной задержки должны быть 11 разЕ ядными.кроме того,дробная часть коэффициента деления выражается обычно десятичной дробью и ее необходимо преобразовать в двоичный код,что также ус 1ожнявт устройство. Сложность каждого указанного элемента с уменьшением шага перестройки коэффициента деления возрастает. Так, при уменьшении шага в 10 раз количество разрядов «гикдого сумматора и элемента сравнения возрастает на четыре единицы. Дополнительно возрастает сложность схемл преобразования дробной части коэффициента деления в двоичный код. Целью изобретения является повышение надежности делителя частоты. С этой целью в уст1 ойств6, содержащее делитель частоты с целочисленным коэффициентом деления, установочные входы которого подключены к шине кода целой части, олок квантованной задержки, информащюнный вход которо го соединен с выходом делителя частоты с целочисленным коэффициентом деления, сумматор, выход которого со единен с устанрвочным входом блока квантованной задержки и блок совпадения, первая группа выходов лсоторого соединена с управляющим входом делителя частоты с целочисленным коэффициентом деления, введены запоминакяций блок и датчик микрокоманд, вход которого соединен с выходом бло ка квантованной задержки, первая группа выходов - с первой группой входов запоминающего блока, вторая Группа входов которого подключена к второй группе выходов блока совпадения, а вторая группа выходов - с пер вой группой входов блока совпадения, второй вход при этом блока совпадения подключен к шине кода числителя дробной части, третий вход - к выход знакового разряда сумматора, вход ко торого соединен с выходом запоминающего устройства. На чертеже изображена структурная электрическая схема устройства. Оно содержит делитель частоты 1 с целочисленным коэффициентом, сумматор 2, блок 3 совпадения, блок 4 ква тованной задержки, запоминающий блок 5, датчик 6 микрокоманд, шину 7 кода целой части, шину 8 кода числителя дробной части. Дпя реализации дробного коэффици ента К А +(//&, где А - целая часть коэффициента; о - числитель дро(;ной части; J2 - знг1менатель дробной час ти, устройство работает циклами. В каждом из циклов за время поступле ния на вход устройства А«/Ь 4-сХ импульсов на выходе выдается Jb импуль сов. При этом -0 выходных импуль сов формируется при коэффициенте де ления, равном А исХ импульсов - при коэффициенте деления, равном А + 1. При срабатывании с коэффициентами А и А 1 мгновенная частота выходных импульсов делителя оказывается оответственно больше и меныие идельной, т. е. Р f ь-у -ftY ьх А- и. ij п А А Av-vl Отсюда получают соответствующее величение и уменьшение реальной ыходной последовательности делителя астоты 1 по сравнению с периодом деальной (гипотетической) выходной оследовательности 0 J --oL-t-, Ц) П)( 2 де tp-1/ -fg (3J- параметр, имекяций азмерность времени (квант временной адержки). Как видно из выражений (1)и (2), изменение периода всегда ыражается целым числом квантов. Даее интервалы времени выражают в коичестве квантов. Значение кванта ри необходимости может быть кратно (или равно) единице времени. Наприер, при ;ь 10, fg 1 МГц из выажения (3) находят, что tp 1 не. Блок 4 реализует задержку, задавамую в количестве квантов. Кроме тоо , все вычисления, выполняемые суматором 2, также производятся в коичестве квантов. Из выражений (1) и (2)находят, что при одном срабатывании делителя частоты 1 с коэффициентом А или А + 1 происходит соответственно опережение реального импульса относительно идеального на оС квантов или отставание- на Jb - оС квантов. При чередовании срабатываний делителя частоты с коэффициентами А и А + + 1 сдвиг после каждого срабатывания дТ о-1-(уг.-с/).3 , квантов (4) где i, j - количество срабатываний соответственно с коэффициентами А и А +1, подсчитанное от начала цикла. При этом в пределах каждого цикла Так как период входных импульсов соответствует., квантам ( /Ь ) , то при выборе очередного коэффициента деления проверяется, при каком из них значение дТ в формуле (4) не превосходит по абсолютной величине Д) /2. Это значение и выбирается на очередной шаг. Вычисленное значение & Т может быть в пределах от до + Jb/2. Для реализации двусторонней задержки кгикдое вычисленное значение ЛТ складывается с константой, равной + jJ/2. Полученное значение каждый раз вводится в блок 4 (это значение может быть в пределах от О по Jb}-. Описанные процессы происходят пос ле каждого выходного импульса, кото рый, проходя на выход, одновременно запускает датчик 6. Микропрограмма, реализуемая устройством, включает смесь микрокоманд. По нулевой микрокоманде, поступаю щей из датчика 6 в запоминающий блок 5, из последнего считывается код чис ла - jb/2 в сумматор 2. По первой микрокоманде происходит занесение кода числа +с в сумматор с одновременным преобразованием его из двоично-десятичного в двоичный . Эта микрокоманда состоит из микроопе раций, количество которых зависит от наибольшей возможной разрядности чис j;a сА . Импульсы микроопераций поступают от датчика 6 на блок 3 и через него (при совпадении с соответствующими разрядами кода числа ot , подаваемого на вход устройства) на входы запоминающего блока 5. При этом из запоминающего блока считываются в сум матор 2 двоичные эквиваленты десятичных разрядов. По второй микрокоманде в буферную память делителя частоты 1 заносится единица. По третьей микрокоманде в сумматор из запоминающего блока считы вается код числа + Jb/2, если записанное в сумматоре число меньше нуля, и код числа , если в сумматоре записано число, большее нуля. Знак числа, записанного в сумматоре, опознается в блоке 3 по содержанию знаково го разряда сумматора. Если при выполнении третьей микрокоманды число в сумматоре изменит знак от положительного к отрицательному, то сигнал переброса знакового разряда сумматора поступает через блок 3 в буферную память делителя частоты 1, записывая там ноль (в противном случае в буферной памяти останется единица, записанная при выполнении второй микрокоманды) . По четвертой микрокоманде фиксируется содержимое буферной памяти делителя частоты 1. Пятая микрокоманда аналогична по содержанию третьей микрокоманде, но при этом содержание буферной памяти делителя частоты изменено быть не может. Шестая микрокоманда считывает из запоминающего блока 5 код числа + jb/2 в сукиатор 2. В результате выполнения микропрограмма в сумматоре образован код положительного числа, выдаваекий в виде потенциалов на установочные входы блока 4, а в буферной памяти делителя частоты 1 записан ноль или единица. В первом случае делитель частоты срабатывает с коэффициентом А, во втором - с коэффициентом А + 1. После выщачи делителей частоты очередного импульса с коэффициентом А или А + 1 его положение корректируется в блоке 4 после чего импульс приходит на выход устройства и на вход датчика б. Далее все процессы повторяются. Разрядность сумматора 2 выбирается, исходя из того, что числа, которые лю гут в нем оказаться в процессе работы устройства, находятся в пределах от - SjJ до +fj& . Квант задержки блока А выбирается по формуле (3), а количество задерживающих секций выбирается с учетом того, что реализуемая задержка находится в пределах от О до jb квантов. Количество делительных декад в делителе частоты 1 зависит от разрядности целой части реализуемого коэффициента. В большинстве практических случаев, в том числе при применении устройства в составе синтезатора частот с кольцом фазовой автоподстройки,целая часть коэффициента деления составляет сотни и тысячи. Поэтому от всех эле1 юнтов устройства, кроме делителя частоты, не требуется высокого быстродействия. Повышение надежности в предлагаемом устройстве достигнуто за счет того, что все вычисленные операции вьлполняются в одном сумматоре. При этом блок 4 управляется непосредственно суыматором и не содержит каких-либо элементов памяти. Тот же сумматор решает задачу преобразования десятичного числа d в двоичный код (в прототипе требуется специальная схема преобразования кодов). Формула изобретения Делитель частоты следования импульсов с дробным коэффициентом деления, содержащий делитель частоты с целочисленным коэффициентом деления, установочные входрл которого подключены к шине кода целой части, блок квантованной задержки, информационный вход которого соединен с выходом делителя частоты с целочисленным коэффициентом деления , сумматор, выход которого соединен с установочным входом блока квантованной задержки, и блок совпадения, первая группа выходов которого соединена с управляющим входом делителя частоты с целочисленньм коэффициентом деления, отличающийся тем, что, с целью повьгиения надежности, в него введены запоминающий блок и датчик микрокоманд, вход которого соединен с выходом блока квантованной задержки, первая группа выходов - с первой группой входов запоминающего блока вторая группа входов которого подключена к второй группе выходов блока совпадения, а вторая группа выходов - с первой группой входов блока совпадения, второй вход которого подключен

К шина кода числителя дробной части, третий вход к выходу знакового разряда сумматора, вход которого соединен с выходом запоминаквдего блока.

Источники информации, принятые во внимание при экспертизе

. .. .-,. .,f,771877,.

8

1.Авторское свидетельство СССР

532964, кл. Н 03 К 23/02, 04.05,75

2.Заявка 2568878/18-21,

кл. Н 03 К 23/00, 11.01.78;по которой принято решение о выдаче авторского свидетельства.

Авторы

Даты

1980-10-15—Публикация

1978-10-04—Подача