ды которого являются вкодами синхронизации синхронного канала, а выход подключен ко входу элемента задержки, первые входы счетчика и дешифратора соединены с информационным входом синхронного канала, и элемент согласо- -вания с линией, выход которого является выходом синхронизации синхронного канала, причем первый вход триггера соединен с выходом дешифратора, подключенного вторым входом к выходу счетчика и первому информационному выходу синхронного канала, а выход - со входом мажоритарного элемента и вторым информа-ционным выходом синхронного канала, введен элемент И, причем первый вход элемента И соединен с выходом мажоритарного элемента, а второй вход с выходом элемента задерхски и вторыми входами счетчика и триггера, выходы дешифратора и элемента И соединены с соответствующими входами элемента ИЛИ, выход которого подключен ко входу элемента согласования с линией.

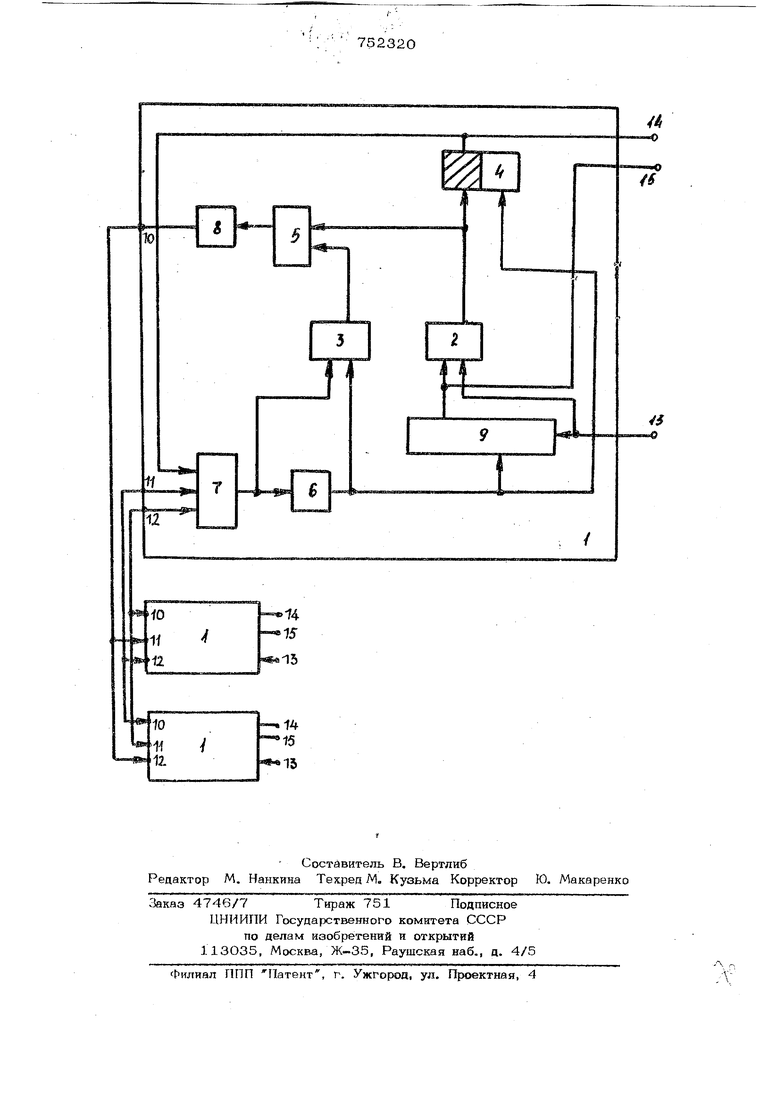

На чертеже представлена блок-схема устройства.

Устройство содержит в каждом синхронном канале 1 дешифратор 2, элемент 3 И ,триггер 4, элемент 5 ИЛИ, элемент 6 задерлски, мажоритарный элемент 7, элемент 8 согласования с линией, выполненный в виде, например, трансформаторной гальванической развязки, счетчик 9, вукод 10 синхронизации, входы 11 и 12 группы входов синхронизации, информационные вход 13 и выходы 14 и 15,

Устройство работает следзющим образом.

Перед началом работы счетчик 9 в каждом канале 1 находится в исходном состоянии, а триггер 4 - в нулевом. Работа устройства начинается с подачи импульсных сигналов по входу 13. Эти сигналы поступают на первые входы счетчика 9 и дешифратора 2. Счетчик 9 ме няет свое состояние по окончании казкдо- го входного импульса. После накопления счетчиком 9 количества импульсов, которое контролируется дешифратором 2, и при поступлении по входу 13 очередного входного сигнала с выхода дешифратора 2 сигнал, равный по длительности. входному, устанавливает в единичное состояние триггер 4 н через элемент 5 ИЛИ поступает через элемент 8 и выход 1О на мажоритарные элементы 7 двух других каналов 1.

Сигнал с единичного выхода триггера 4 поступает на один из входов мажоританого элемента 7 своего канала. При поступлении хотя бы на один из входов 11 и 12 сигналов обмена из других каналов мажоритарный элемент 7 срабатывает и сигнал с его выхода поступает на входы элемента 6 задержки и элемента 3 И.

Пока отсутствует сигнал на выходе элемента 6 задержки на второй вход элемента 3 И поступает разрешающий сигнал, при наличии которого сигналс выхода мажоритарного элемента 7 через элемент 3 И и элемент 5 ИЛИ дублирует сигнал обмена на выходе Ю.

Время задержки элемента 6 должно быть больше длительности импульсов на входе 13 любого канала. По окончании входного сигнала на входе 13 в счетчике 9 устанавливается код, на единицу больше того, который контролируется дешифратором 2. Выходным сигналом с элемента 6 задерхски в счетчик 9 устанавливается или подтверждается код, на единицу больше того, который контролируется дешифратором 2, триггер 4 возвращается в нулевое состояние и запрешается прохождение через элемент 3 И во внешнюю цепь обмена сигнала с выхода мажоритарного элемента 7.

Счетчик 9 в каждом канале продолжает вести счет числа импульсов, поступающих по входу 13.

В том случае, если произойдет рассин хронизация всех трех каналов, работа усройства происходит следующим образом.

Когда в счетчике 9 одного из каналов устанавлийается код, контролируемы дешифратором 2, триггер 4 устанавливается в единичное состояние и по выходу 10 сигнал обмена передается на мажоритарные элементы 7 других каналов. В этих каналах сигнал обмена не производит никаких переключений, так как на мажоритарные элементы 7 поступает сигнал только по одному входу.

По каждому импульсу, поступающему на вход 13, код в счетчиках 9 каналов 1 изменяется на одну единицу до тех пор, пока счетчик хотя бы еще одного из каналов не установится в состояние контролируемое дешифратором 2.

Очередной входной импульс по входу 13 в этом канале устанавливает триггер 4 в единичное состояние и, как сигнал обмена, через элемент 5 ИЛИ по выходу ДО поступает на входы мажоритарных элементов 7 других каналов. В первом

канапе (нумерация каналов условная, каналы названы в том порядке, в котором после рассинхронизации в них набирается код, контролируемый дешифратором 2 в котором триггер 4 был установлен в

единичное состояние ранее, сигнал обмена с выхода мажоритарного элемента 7 поступает на элемент 6 задержки и на вход элемента 3 И, с выхода которого через элемент 5 ИЛИ и элемент 8 воз- вращается в цепь внешнего обмена. На входы третьего канала поступает два сигнала обмена, мажоритарный элемент срабатывает,и сигнал поустпает на вход элемент 6 задержки и через элементы 3 И, 5 ИЛИ и элемент 8 - на выход 10. Выходными сигналами с элементов 6 задержки в первом и третьем каналах в счетчиках 9 устанавливается код, на единицу больше того, .который контролируется дешифратором 2, а во втором / канале его состояние подтверждается, триггеры 4 в первом и втором каналах возвращаются в нулевое состояние. Все три канала синхронизовались между собой, .для чего на вход счетного устройства из каналов достаточно подать число импульсов, равное числу состояний счетчика. При выходе из строя одного канала два оставшихся канала работают синхронно. При выходе из строя двух каналов третий продолжает работать самостоятельно, так как входные сигналы поступают непосредственно на вход счетчика 9, а наличие элемента 8 трансформаторной гальванической развязки исключает влияние неисправных каналов на канал, работающий по цепям обмена.

Таким образом, устройство обеспечивает повышение скорости синхронизации синхронных каналов, что приводит к снижению времени пребывания устройства в состоянии отказа и повышению надежности устройства.

Форм у.л а изобретения Устройство для обмена информацией синхронных каналов, содержащее группу синхронных каналов, причем выход синхронизации каждого синхронного канала соединен с соответствующим входом синхронизации всех других синхронных каналов, информационные вход и выход каждого синхронного канала являются соответствующими входом и выходами устройства, причем каждый синхронный канал содержит счетчик, дешифратор, триггер, элемент ИЛИ, мажоритарный элемент, входы которого являются входами синхронизации синхронного канала, а выход подключен ко входу элемента задержки, первые входы счетчика и дешифратора соединены с информационным входом синхронного канала, и элемент согласования с линией, выход которого является выхо дом синхронизации синхронного канала, причем первый вход триггера соединен с выходом дешифратора, подключенного вторым входом к выходу счетчика и первому информационному выходу синхронного канала, а выход - со входом мажоритар)- ного элемента и вторым информационным выходом синхронного канала, отличающееся тем, что, с целью повышения пропускной способности синхронных каналов, в каждый синхронный канал введен элемент И, причем первый вход элемента И соединен с выходом мажоритарного элемента, а второй вход - с выхдом элемента задержки и входами счетчика и триггера, выходы дешифратора и элемента И соединены с соответствующими входами элемента ИЛИ, выход которого подключен ко входу элемента согласования с линией.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 4891О1, кл. G 06 F 3/О4, 1974.

2.Авторское свидетельство СССР по заявке М 2496238/18-24,

кл. G 06 Р 15/ОО, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией синхронных каналов | 1977 |

|

SU679974A1 |

| Устройство для обмена информацией синхронных каналов | 1982 |

|

SU1072037A1 |

| Устройство обмена информацией синхронных каналов | 1976 |

|

SU643860A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU824210A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

| Адаптивное резервированное устройство | 1983 |

|

SU1174929A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Устройство для синхронизации сигналов | 1977 |

|

SU669347A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-24—Подача