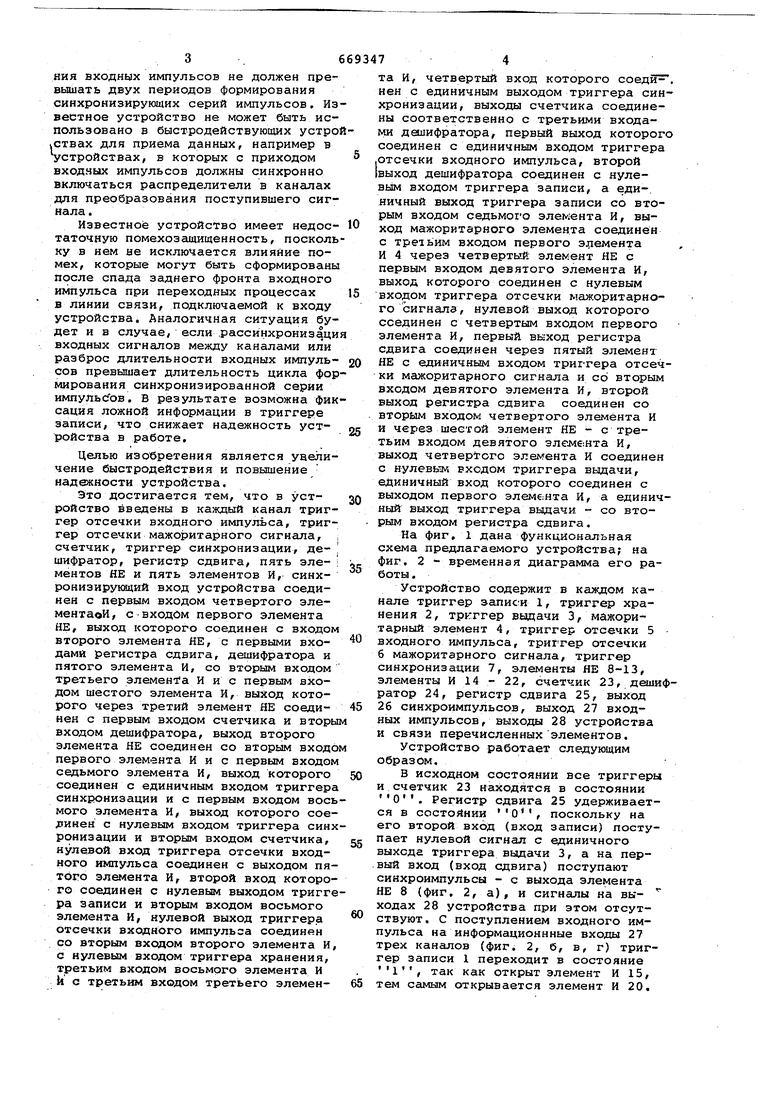

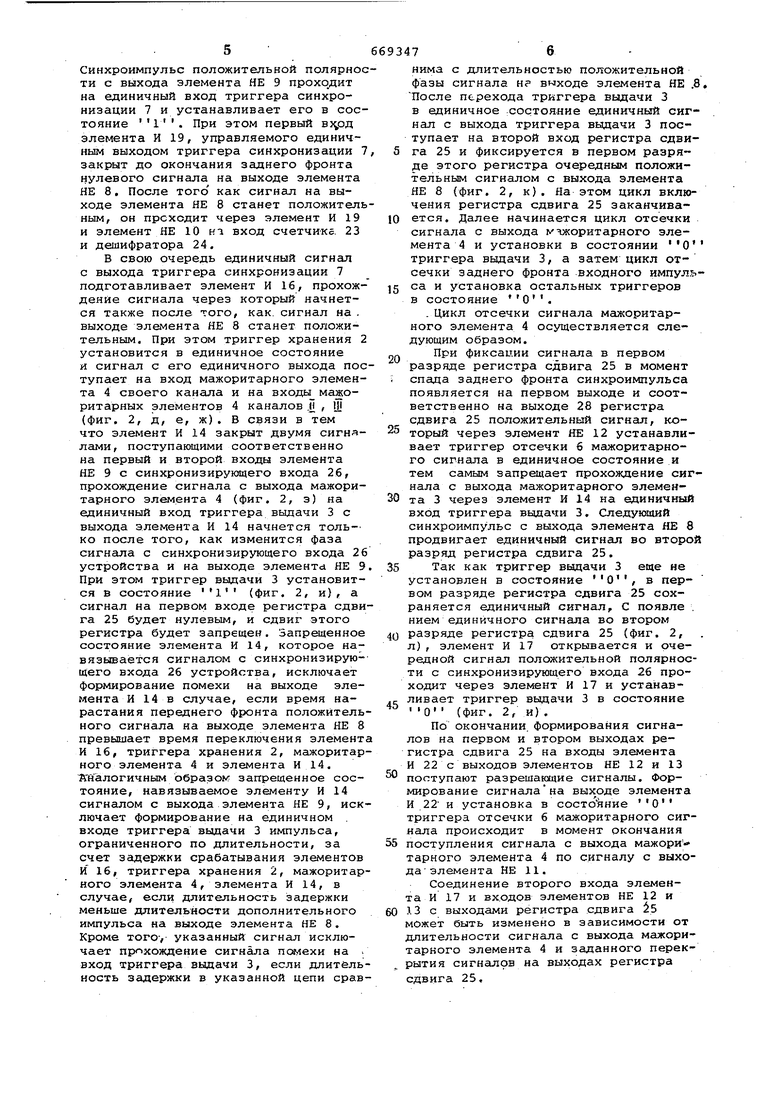

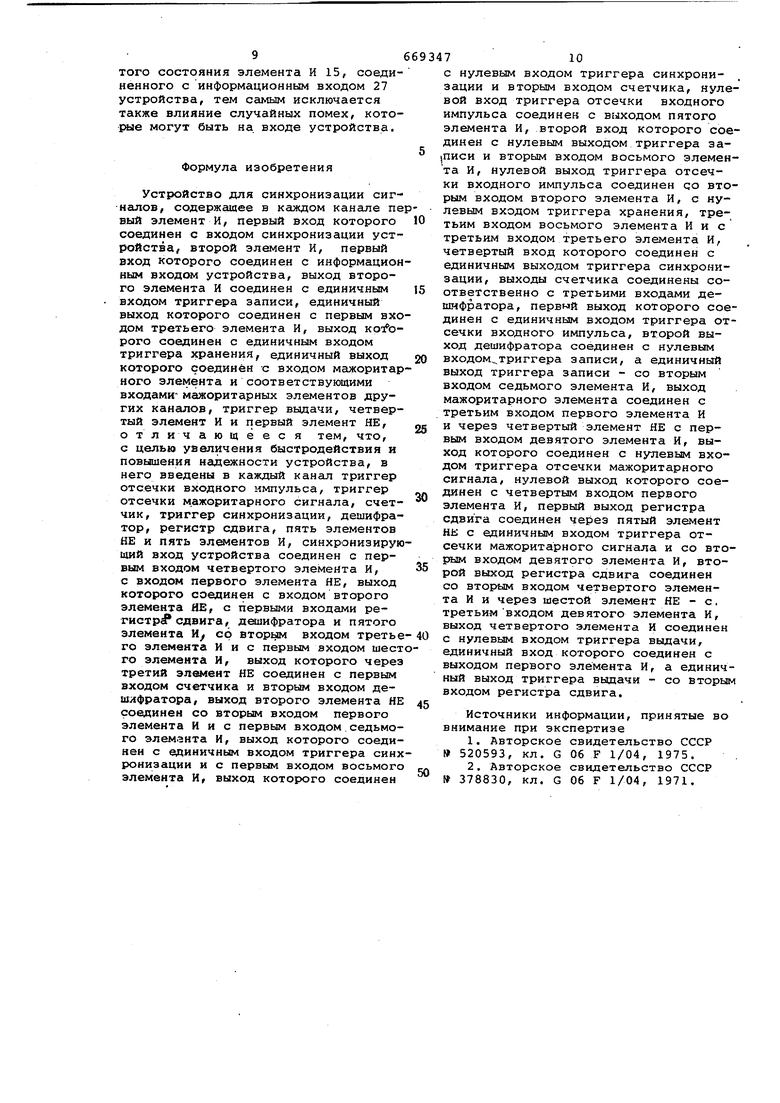

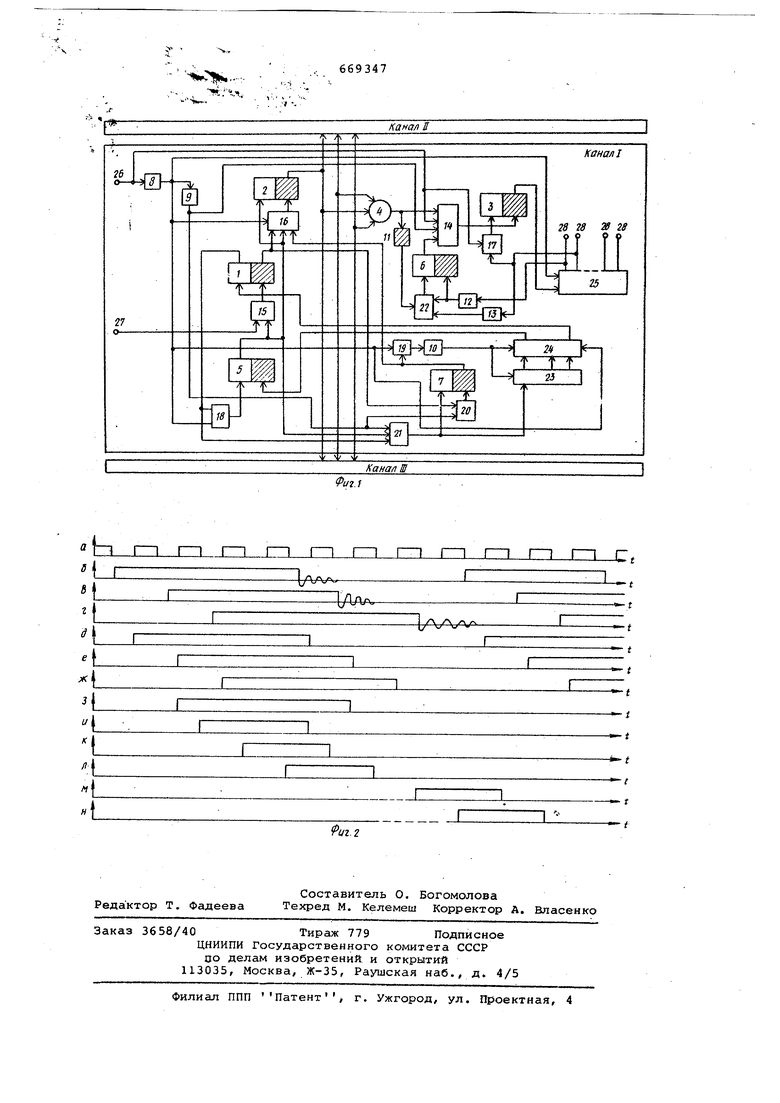

Изобретение относится к автоматике и вычислительной технике и может использоваться в многоканальных устройствах повышенной надежности, например в устройствах для приема данных, во внешних устройствах ЭВМ для синхронного включения распределителей импульсов. . Известно устройство для синхронизации несинхронно поступающих сигналов в каналах, содержащее в каждом канале триггеры со счетным входом дл приема и хранения информации, триггер выдачи, мажоритарный элемент, эл менты И и элементы ИЛИ, шины синхроимпульсов и шину входных импульсов Такое устройство имеет ограниченное &лстродейс.твие. Это обусловлено тем, что для синхронизации входных импульсов используется циклическая формируемая группа из трех синхроимпульсов, разнесенных во времени. В связи с зтим период поступления входных импульсоа в каналах не долже превышать времени двух циклов формирования синхроимпульсов. Кроме того, в устройстве не предусмотрены мери по исключению помех, которые могут иметь место после спада заднего фронта входного импульса. например, при переходном процессе в линии связи, подключаемой к входу устройства. Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для синхронизации сигналов, содержащее в каждом канале первый элемент И, первый вход которого соединен с входом синхронизации устройства, второй элемент И, первый вход которого соединен с информационным входом устройства, выход второго элемента И соединен с единичным входом триггера записи, единичный выход которого соединен с первым входом третьего элемента И-, выход которого соединен с единичным входом триггера хранения, единичный выход которого соединен с входом мажоритарного элемента и соответствующими входами мажоритарных элементов других каналов, триггер выдачи, четвертый элемент И и первый элемент HEti. . Такое устройство имеет ограниченное быстродействие, поскольку в нем для синхронизации входного сигнала также используется циклическая формируемая серия из трех синхроимпульсов, в связи с этим период поступле ния входных импульсов не должен превышать Двух периодов формирования синхронизирующих серий импульсов. Из вестное устройство не может быть использовано в быстродействующих устро iCTBax для приема данных, например в устройствах, в которых с приходом входных импульсов должны синхронно включаться распределители в каналах для преобразования поступившего сигнала , Известное устройство имеет недостаточную помехозащищенность, посколь ку в нем не исключается влияние помех, которые могут быть сформированы после спада заднего фронта входного импульса при переходных процессах в линии связи, подключаемой к входу устройства. Аналогичная ситуация будет и в случае, если .рассйнхронизаци входных сигналов между каналами или разброс длительности входных импульсов превышает длительность цикла фор мирования синхронизированной серии импульсГов. В результате возможна фик сация ложной информации в триггере записи, что снижает надежность устройства в работе. Целью изобретения является увеличение быстродействия и повышение надежности устройства. Это достигается тем, что в устройство введены в каждый канал триггер отсечки входного импульса, триггер отсечки мажоритарного сигнала, счетчик, триггер синхронизации, дешифратор, регистр сдвига, пять элементов НЕ и пять элементов И, синхронизирукиций вход устройства соединен с первым входом четвертого элементаоИ, с-входим первого элемента НЕ, выход которого соединен с входом второго элемента НЕ, с первыми входами регистра сдвига, дешифратора и пятого элемента И, со вторым входом третьего элемента И и с первым входом шестого элемента И, выход которого через третий элемент НЕ соединен с первым входом счетчика и вторы входом дешифратора, выход второго элемента НЕ соединен со вторым входо первого элемента И и с первым входом седьмого элемента И, выход которого соединен с единичным входом триггера синхронизации и с первым входом вось мого элемента И, выход которого соедзикен с нулевым входом триггера синх ронизации и вторым входом счетчика, нулевой вход триггера отсечки входного импульса соединен с выходом пятого элемента И, второй вход которого соединен с нулевым выходом тригге ра записи и вторым входом восьмого элемента И, нулевой выход триггера отсечки входного импульса соединен со вторым входом второго элемента И с нулевым входом триггера хранения, третьим входом восьмого элемента И и с третьим входом третьего элемента И, четвертый вход которого соеди- . нен с единичным выходом триггера синхронизации, выходы счетчика соединены соответственно с третьими входами дешифратора, первый выход которого соединен с единичным входом триггера отсечки входного импульса, второй ВЫХОД дешифратора соединен с нулевым входом триггера записи, а еди-. яичный выход триггера записи со вторым входом седьмохО элемента И, выход мажоритарного элемента соединен с треаьим входом первого эсремента И 4 через четвертый элемент НЕ с первым входом девятого элемента И, выход которого соединен с нулевым входом триггера отсечки мажоритарного сигнала, нулевой выход которого соединен с четвертым входом первого элемента И, первый выход регистра сдвига соединен через пятый элемент НЕ с единичным входом триггера отсечки Мс1жоритарного сигнала и со вторым входом девятого элемента И, второй выход регистра сдвига соединен со вторым входом четвертого элемента И и через шестой элемент НЕ - с третьим входом девятого элемента И, выход четвертого элемента И соединен с нулевым входом триггера выдачи, единичный вход которого соединен с выходом первого элемента И, а единичный выход триггера выдачи - со вторым входом регистра сдвига. На фиг, 1 дана функциональная схема предлагаемого устройства; на фиг. 2 - временная диаграмма его работы , Устройство содержит в каждом канале триггер записи 1, триггер хранения 2, триггер выдачи 3, мажоритарный элемент 4, триггер отсечки 5 входного импульса, триггер отсечки 6 мажоритарного сигнала, триггер синхронизации 7, элементы НЕ 8-13, элементы И 14 - 22, счетчик 23, дешифратор 24, регистр сдвига 25, выход 26 синхроимпульсов, выход 27 входных импульсов, выходы 28 устройства и связи перечисленныхэлементов. Устройство работает следующим образом. В исходном состоянии все триггеры и счетчик 23 находятся в состоянии . Регистр сдвига 25 удерживается в состоянии , поскольку на его второй вход (вход записи) поступает нулевой сигнал с единичного выхода триггера выдачи 3, а на пер,вый вход (вход сдвига) поступают синхроимпульсы - с выхода элемента НЕ 8 (фиг, 2, а), и сигналы на вы- ходах 28 устройства при этом отсутствуют. С поступлением входного импульса на информационнные входы 27 трех каналов (фиг, 2, б, в, г) триггер записи 1 переходит в состояние , так как открыт элемент И 15, тем самым открывается элемент И 20, 5 Синхроимпульс положительной полярно ти с выхода элемента НЕ 9 прохо дит на единичный вход триггера синхронизации 7 и устанавливает его в сос 1 . При этом первый вгдэд тояние И 19, управляемого единичэлементаным выходом триггера синхронизации закрыт до окончания заднего фронта нулевого сигнала на выходе элемента НЕ 8, После того как сигнал на выходе элемента НЕ 8 станет положител ным, он преходит через элемент И 19 и элемент НЕ 10 кт вход счетчика. 23 и дешифратора 24, В свою очередь единичный сигнал с выхода триггера синхронизации 7 подготавливает элемент И 16, прохож дение сигнала через который начнется также после того, как. сигнал на . выходе элемента НЕ 8 станет положительным. При этом триггер хранения установится в единичное состояние я сигнал с его единичного выхода по тупает на вход мажоритарного элемен та 4 своего канала и на входы мажоритарных элементов 4 каналов .Д , tjl (фиг, 2, д, е, ж), В связи в тем что элемент И 14 закрыт двумя сигна лами, поступающими соответственно на первый и второй входы элемента НЕ 9 с синхронизирующего входа 26, прохождение сигнала с выхода мажори тарного элемента 4 (фиг, 2, э) на единичный вход триггера выдачи 3 с выхода элемента И 14 начнется только после того, как изменится фаза сигнала с синхронизирующего входа 2 устройства и на выходе элемента НЕ При этом триггер выдачи 3 установит ен в состояние Ч (фиг, 2, и), а сигнал на первом входе регистра сдв га 25 будет нулевым, и сдвиг этого регистра будет запрещен. Запрещенное состояние элемента И 14, которое на вязывается сигналом с синхронизирую щего входа 26 устройства, исключает формирование помехи на выходе элемента И 14 в случае, если время нарастания переднего фронта положитель ного сигнала на выходе элемента НЕ 8 превышает время переключения элемент И 16, триггера хранения 2, мажоритар ного элемента 4 и элемента И 14, ТШалогичным образом запрещенное состояние, навязываемое элементу И 14 сигналом с выхода элемента НЕ 9, иск лючает формирование на единичном . входе триггера выдачи 3 импульса, ограниченного по длительности, за счет задержки срабатывания элементов И 16, триггера хранения 2, мажоритар ного элемента 4, элемента И 14, в случае, если длительность задержки меньше длительности дополнительного импульса на выходе элемента НЕ 8, Кроме ТОГО , указанный сигнал исключает пр хождение сигнала помехи на вход триггера выдачи 3, если длитель ность задержки в указанной цепи срав 7 нима с длительностью положительной фазы сигнала н вмходе элемента НЕ .8. После перехода триггера выдачи 3 в единичное состояние единичный сигнал с выхода триггера выдачи 3 поступает на второй вход регистра сдвига 25 и фиксируется в первом разряде этого регистра очередным положительным сигналом с выхода элемента НЕ 8 (фиг, 2, к). На этом цикл включения регистра сдвига 25 заканчивается. Далее начинается цикл отсечки сигнала с выхода мяжоритарного элемента 4 и установки в состоянии О триггера выдачи 3, а затем цикл отсечки заднего фронта входного импульса и установка остальных триггеров в состояние О, . Цикл отсечки сигнала мажоритарного элемента 4 осуществляется следующим образом. При фиксации сигнала в первом разряде регистра сдвига 25 в момент спада заднего фронта синхроимпульса появляется на первом выходе и соответственно на выходе 28 регистра сдвига 25 положительный сигнаш, который через элемент НЕ 12 устанавливает триггер отсечки 6 мажоритарного сигнала в единичное состояние и тем самым запрещает прохождение сигнала с выхода мажоритарного элемента 3 через элемент И 14 на единичный вход триггера выдачи 3, Следующий синхроимпульс с выхода элемента НЕ 8 продвигает единичный сигнал во второй разряд регистра сдвига 25, Так как триггер выдачи 3 еще не установлен в состояние О, в первом разряде регистра сдвига 25 сохраняется единичный сигнал, С появле . нием единичного сигнала во втором разряде регистра сдвига 25 (фиг, 2, л), элемент И 17 открывается и очередной сигнал положительной полярности с синхронизирующего входа 26 проходит через элемент И 17 и устанавливает триггер выдачи 3 в состояние О (фиг, 2, и) , По окончании, формирования сигналов на первом и втором выходах регистра сдвига 25 на входы элемента И 22 с выходов элементов НЕ 12 и 13 поступают разрешающие сигналы. Формирование сигналана выходе элемента И 22 и установка в О триггера отсечки 6 мажоритарного сигнала происходит в момент окончания поступления сигнала с выхода мажори- тарного элемента 4 по сигналу с выхода элемента НЕ 11, Соединение второго входа элемента И 17 и входов элементов НЕ 12 и 13 с выходами регистра сдвига 5 может быть изменено в зависимости от длительности сигнала с выхода мажоритарного элемента 4 и заданного перекрытия сигналрв на выходах регистра сдвига 25, В цикле отсечки входного импульса устройстжо функционирует следуквдим образом Положительный импульс, поступивщий с выхода элемента НЕ 10 на вход счетчика 23 после установки триггера синхронизации 7 в единичное соетояние, проходит на вход счетчика 23 и фиксируется в нем в момент спада заднего фронта этого импульса. Тем же синхронизирующим импульсом, поступающим с выхода элемента НЕ 8 на первый вход дешифратора 24, осуществ ляется запрещение прохождения сигналов помех с выходов дешифратора 24 при переходных процессах в счетчике 23. Сигналом с выхода элемента НЕ 10 осуществляется дополнительное увели ченйе времени стробирования выходов дешифратора 24 на ср.абатыван11я элементов И 19 и НЕ 10, что исключае прохождение сигналов помех на выход дешифратора 24 в случае, если время переходных процессов в счетчике 23 сравнимо с длительностью входного импульса счетчика 23. Сигналом, формируе№ М на первом выходе дешифратора 24, триггер отсечки 5 входного сигнала устанавливается в состояние 1 и сигналом с его нулевого выхода триггер хранения 2 устанавливается в состояние О (фиг. 2, д, е, ж), а элемент И 15 закрывается, что приводит к запрещению поступления входного сигнала на единичный вход триггера записи 1 и к окончанию формирования сигнала на входе мажоритарного элемента 4 своего канала и соседних каналов (фиг. 2, з). Длительность интервала времени, в течение которого формируется сигнал на входах мажоритарных элементов 4, выбирается так, чтоейл обеспечить перекрытие сигналов с единичных выходов триггера хранения 2 в трех каналах. Следующим сигналом,- формируемым на втором выходе дешифратора 24, триггер записи 1 устанавливается в состояние О, при этсм открь}вают ся элементы И 18 и 21, управляемые нулевым выходом триггера записи 1. Установка триггера отсечки 5 входно го импульса в состояние осуше вляется импульсом положительной полярности с выхода элемента и 18, который формировался после поступле ния на вход счетчика 23 импульса, обусловившего формирование сигнала на втором выходе дешифратора 24. Ес ли же задержка сигнала в счетчике 23, дешифраторе 24 и триггере запи|си 1 превышает длительность период .синхроимпульсов, установка триггера отсечки 5 входного импульса в сое-тоянии О осуществляется следующим импульсом положительной полярно ти на выходе элемента НЕ 8. Так как триггер записи 1 и триггер отсечки 5ВХОДНОГО импульса установлены в то подготовлены сосостояниитветственно второй и третий входы элемента И 21, и очередной импульс с выхода элемента НЕ 9 проходит через элемент И 21 и устанавливает триггер синхронизации 7 .и счетчик 23 На этом цикл приев состояние ма входного импульса заканчивается. Длительность интервала времени, определяемого моментом формирования импульса на втором выходе дешифратора 24, выбирается так, чтобы разрешить сброс триггера записи 1 в состояниеи последукядих узлов схемы только по окончании переходных процессов, которые могут иметь место после спада заднего фронта входного импульса, поступившего на информационный вход 27 устройства. В связи с тем что входные элементы устройства работают в каждом канале автономно, возможно поступление очередного сигнала на информационный вход 27 устройства в тот момент, когда еще не закончено формирование сигналов на остальных выходах регистра сдвига 25 и соответственно на выходах 28 регистра сдвига 25 (фиг. 2, м, н). Так как в каждом канале период следования входных импульсов остается потоянным на-все время передачи информации, а между собой ймпульсы в каналах могут быть несинхронны в пределах saxBata сигнала можоритарным элементом 4, то длительность отсечки входных сигнгшов в каждом канале не зависит от величины рассинхронизации между каналами. Таким образом, предложенное устройство позволяет осуществить синхронный запуск регистров сдвига 25 при несинхронном поступлении входных импульсов в трех каналах, в пределах периода следования входных импульсов. В связи с тем, что синхронизация всех узлов устройства осзвдествляется от одной синхронизирующей сетки импульсов, быстродействие устройства определяется лишь периодом поступления входных импульсов и требуемым циклом работы регистров сдвига 25, , Кроме того, в предлагаемом устройстве осуществляется надежное стробирование заднего фронта входного импульса в каждом канапе, что исключает влияние переходных процессов, которые могут быть после спада заднего фронта входного импульса. Тем самьв исключается также влияние разброса длительности входных импульсов, что имеет место при установке на входах устройства магистральных усилителей. Сигнал осуществляющий стробирование заднего фронта в предлагаемом устройстве, может заканчиваться непосредственно перед прихо- дом очередного входного импульса, то существенно увеличивает время закрытого состояния элемента И 15, соединенного с информационным входом 27 устройства, тем самым исключается также влияние случайных помех, которое могут быть на. входе устройства. Формула изобретения Устройство для синхронизации сигналов, содержащее в каждом канале пе вый элемент И, первый вход которого соединен с входом синхронизации устройства, второй элемент И, первый вход которого соединен с информацион ным входом устройства, выход второго элемента И соединен с единичньа входом триггера записи, единичный выход которого соединен с первым вхо дом третьего элемента И, выход Koifoрого соединен с единичным входом триггера хранения, единичный выход которого соединён с входом мажоритар ного элемента и соответствующими входами мажоритарных элементов других каналов/ триггер выдачи, четвертый элемент И и первый элемент НЕ, отличающееся тем, что, с целью увеличения быстродействия и повьаления надежности устройства, в него введены в каждый канал триггер отсечки входного импульса, триггер отсечки мажоритарного сигнала, счет чик, триггер синхронизации, дешифратор, регистр сдвига, пять элементов ЙЕ и пять элементов И, синхронизирую щий вход устройства соединен с первым входом четвертого элемента И, с входом первого элемента НЕ, выход которого соединен с входом второго элемента як, с первыми входами регистр сдвига, дииифратора и пятого элемента Иу со вторым входом третье го элемента И и с первым входом шест го элемента И, выход которого через третий элемент НЕ соединен с первым входом счетчика и вторым входом дешлфратора, выход второго элемента НЕ соединен со вторым входом первого элемента И и с первым входом.седьмого элемента И, выход которого соединен с единичным входом триггера синх ронизации и с первым входом восьмого элемента И, выход которого соединен с нулевым входом триггера синхронизации и вторым входом счетчика, нулевой вход триггера отсечки входного импульса соединен с выходом пятого элемента И, второй вход которого соединен с нулевым выходом триггера заПиси и вторым входом восьмого Элемента И, нулевой выход триггера отсечки входного импульса соединен qo вторым входом второго элемента И, с нулевым входом триггера хранения, третьим входом восьмого элемента И и с третьим входом третьего элемента И, четвертый вход которого соединен с единичным выходом триггера синхронизации, выходы счетчика соединены соответственно с третьими входами дешифратора, первый выход которого соединен с единичным входом триггера отсечки входного импульса, второй выход дешифратора соединен с нулевым входом триггера записи, а единичный выход триггера записи - со вторым входом седьмого элемента И, выход мажоритарного элемента соединен с третьим входом первого элемента И и через четвертый элемент НЕ с первым входом девятого элемента И, выход которого соединен с нулевым входом триггера отсечки мажоритарного сигнала, нулевой выход которого соединен с четвертым входом первого элемента И, первый выход регистра сдвига соединен через пятый элемент НЕ с единичным входом триггера отсечки мажоритарного сигнала и со вторым входом девятого элемента И, второй выход регистра сдвига соединен со вторым входом четвертого элемента И и через шестой элемент НЕ - с. третьимвходом девятого элемента И, выход четвертого элемента И соединен с нулевым входом триггера выдачи, единичный вход которого соединен с выходом первого элемента И, а единичный выход триггера вьщачи - со вторым входом регистра сдвига. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 520593, кл. G 06 F 1/04, 1975. 2.Авторское свидетельство СССР 378830, кл. G 06 F 1/04, 1971.

669347

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации сигналов | 1980 |

|

SU868735A2 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Трехканальное устройство для управления синхронизацией микропроцессорной системы | 1985 |

|

SU1352475A1 |

| Резервированный делитель частоты | 1990 |

|

SU1780187A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Устройство для обмена информацией синхронных каналов | 1982 |

|

SU1072037A1 |

Авторы

Даты

1979-06-25—Публикация

1977-04-11—Подача