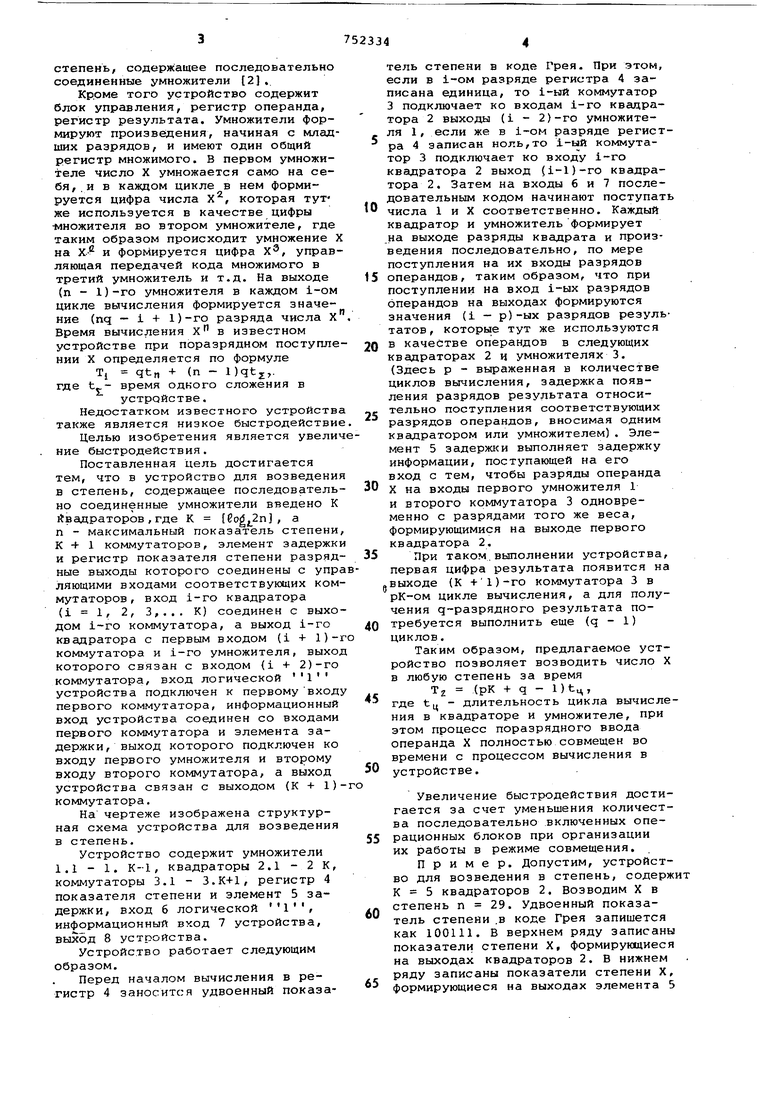

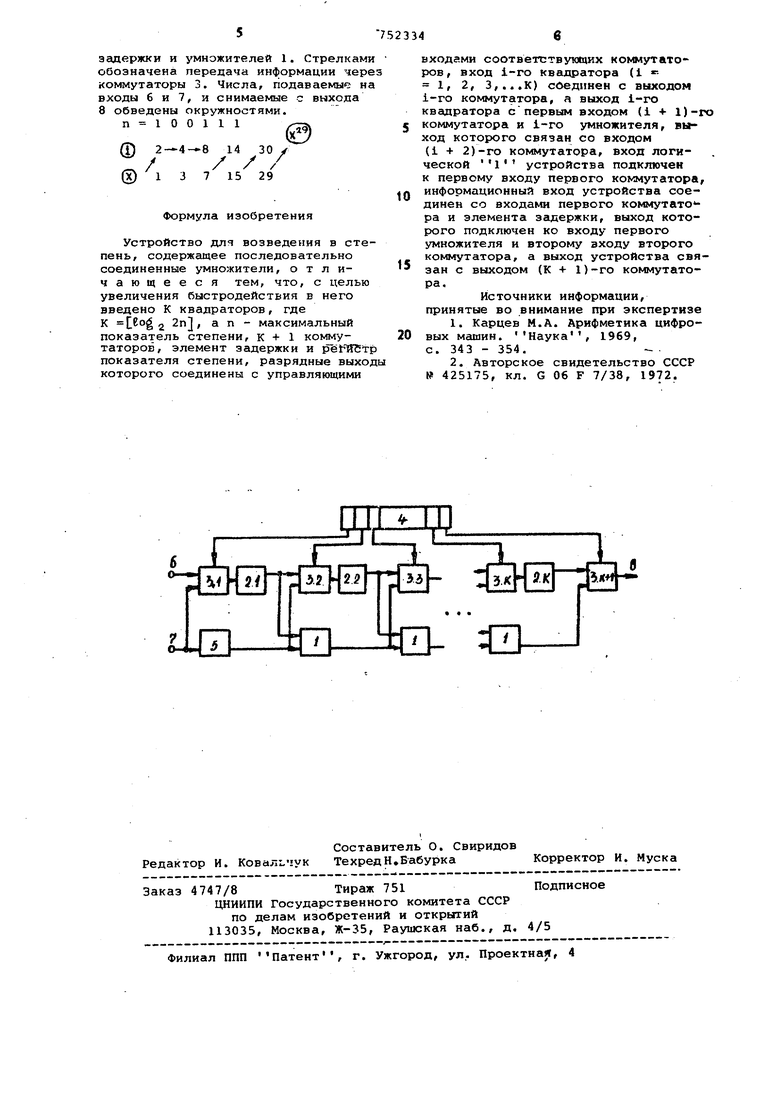

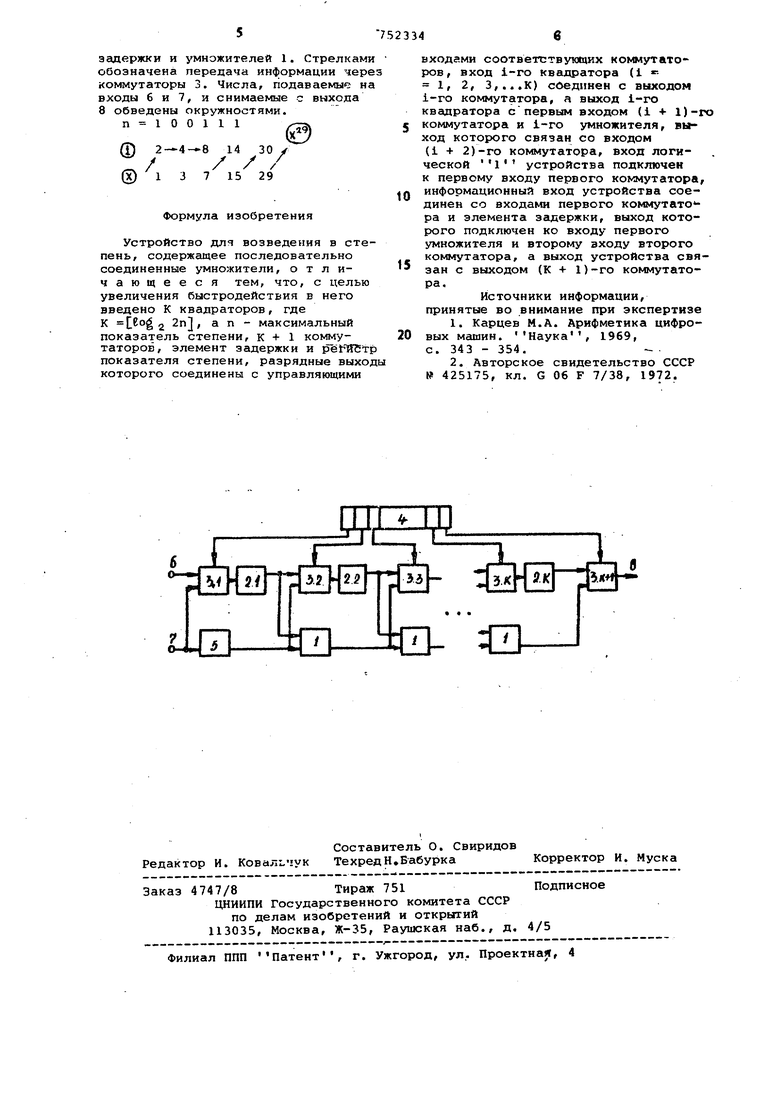

(54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В СТЕПЕНЬ Изобретение относится к цифровой вычислительной технике и может быть использовано для возведения в степен числа, представленного последовательным кодом. Известно устройство для возведения в степень. Такое устройство пред ставляет собой универсальную ЦВМ, а возведение в степень с помощью такого устройства осуществляется путем выполнения последовательности умножений по соответствунхдей программе 1 Однако известное устройство обладает низким быстродействием, так как во-первых, оно не позволяет совмещать во времени с вычислением процес поразрядного ввода в устройство oneранда X (например, когда операнд X формируется на аналого-цифровом преобразователе поразрядного уравновеши вания, или когда из-за ограничений накладываемых на канал связи, операн X может поступать в устройство тольк поразрядно). во-вторых, для возведения числа X в степень п требуется в среднем eogjn раз выполнить операцию умножения, где .,. - функция взятия целой части. В-третьих, при программной реализации алгоритма возведения в степень требуются дополнительные затраты времани на модификацию команд, на выборку из памяти команд и операндов и т.п. Таким образом, время, необходимое для возведения числа X в степень п с помощью известных устройств определяется по формуле Та,, разрядность операнда х; где q tn период следования разрядов числа X ( в общем случае tfi определяется внешними по отношению к устройству факторами, например, быстро действием источника информации) ; время одного умножения; дополнительные затраты времени, обусловленные программной реализацией. Наиболее близким к заявляемому является устройство для возведения BJ степень, содержащее последовательно соединенные умножители 21 . Кррме того устройство содержит блок управления, регистр операнда, регистр результата. Умножители формируют произведения, начиная с млад ших разрядов, и имеют один общий регистр множимого. В первом умножителе число X умножается само на себя,, и в каждом цикле в нем формируется цифра числа Х, которая тут же используется в качестве цифры -множителя во втором умножителе, где таким образом происходит умножение на Х. и формируется цифра Х, управ ляющая передачей кода множимого в третий умножитель и т.д. На выходе (п - 1)-го умножителя в каждом i-ом цикле вычисления формируется значение (nq - i + 1)-го разряда числа х Время вычисления х в известном устройстве при поразрядном поступле НИИ X определяется по формуле qtn + (п - l)qt где время одного сложения в устройстве. Недостатком известного устройств также является низкое быстродействи Целью изобретения является увели ние быстродействия. Поставленная цель достигается тем, что в устройство для возведени в степень, содержащее последователь но соединенные умножители введено К йвадраторов ,где К , а п - максимальный показатель степени К -f 1 коммутаторов, элемент задержк и регистр показателя степени разряд ные выходы которого соединены с упр ляющими входами соответствующих ком мутаторов, вход i-ro квадратора (, 2, 3,... К) соединен с выхо дом i-ro коммутатора, а выход i-ro квадратора с первым входом (i + 1)коммутатора и i-ro умножителя, выход которого связан с входом {i + 2)-го коммутатора, вход логической устройства подключен к первому вход первого коммутатора, информационный вход устройства соединен со входами первого коммутатора и элемента задержки, выход которого подключен ко входу первого умножителя и второму входу второго коммутатора, а выход устройства связан с выходом (К + 1)коммутатора. На чертеже изображена структурная схема устройства для возведения в степень. Устройство содержит умножители 1.1 - 1. К--1, квадраторы 2.1 - 2 К, коммутаторы 3.1 - З.К-fl, регистр 4 показателя степени и элемент 5 задержки, вход 6 логической , информационный вход 7 устройства, выход 8 устройства. Устройство работает следующим образом. Перед началом вычисления в регистр 4 заносится удвоенный показатель степени в коде Грея. При этом, если в 1-ом разряде регистра 4 записана единица, то i-ый коммутатор 3 подключает ко входам 1-го квадратора 2 выходы (i - 2)-го умножителя 1, если же в i-ом разряде регистра 4 записан ноль,то 1-ый коммутатор 3 подключает ко входу 1-го квадратора 2 выход (i-l)-ro квадратора 2. Затем на входы 6 и 7 последовательным кодом начинают поступать числа 1 и X соответственно. Каждый квадратор и умножитель формирует на выходе разряды квадрата и произведения последовательно, по мере поступления на их входы разрядов операндов, таким образом, что при поступлении на вход i-ых разрядов операндов на выходах формируются значения (i - р)-ых разрядов результатов, которые тут же используются в качестве операндов в следующих квадраторах 2 ч умножителях 3. (Здесь р - выраженная в количестве циклов вычисления, задержка появления разрядов результата относительно поступления соответствующих разрядов операндов, вносимая одним квадратором или умножителем). Элемент 5 задержки выполняет задержку информации, поступающей на его вход с тем, чтобы разряды операнда X на входы первого умножителя 1 и второго коммутатора 3 одновременно с разрядами того же веса, формирующимися на выходе первого квадратора 2. При таком,выполнении устройства, первая цифра результата появится на выходе (К +1)-го коммутатора 3 в рК-ом цикле вычисления, а для получения q-разрядного результата потребуется выполнить еще (q - 1) циклов. Таким образом, предлагаемое устройство позволяет возводить число X в любую степень за время TZ (рК + q - 1)Ьц, где t - длительность цикла вычисления в квадраторе и умножителе, при этом процесс поразрядного ввода операнда X полностью совмещен во времени с процессом вычисления в устройстве. Увеличение быстродействия достигается за счет уменьшения количества последовательно включенных операционных блоков при организации их работы в режиме совмещения. Пример. Допустим, устройство для возведения в степень, содержит К 5 квадраторов 2. Возводим X в степень п 29. Удвоенный показатель степени .в коде Грея запишется как 100111. В верхнем ряду записаны показатели степени X, Формирующиеся на выходах квадраторов 2. В нижнем ряду записаны показатели степени X, формирующиеся на выходах элемента 5

задержки и умножителей 1. Стрелками обозначена передача информации через коммутаторы 3, Числа, подаваемые на входы б и 7, и снимаемые с выхода 8 обведены окружностями.

П 100111X--SV

2-4-8 14 30 / // / /

15 29

3

Формула изобретения

Устройство для возведения в степень, содержащее последовательно соединенные умножители, отличающееся тем, что, с целью увеличения быстродействия в него введено К квадраторов, где К 0 2 2пj, an- максимальный показатель степени, к + 1 коммутаторов, элемент задержки и реМГСтр показателя степени, разрядные выход которого соединены с управляющими

входами соответствующих коммутаторов, вход i-ro квадратора (1 , 2, 3,...К) соединен с выходом i-ro коммутатора, а выход 1-го квадратора спервым входом (1 -f 1)-го коммутатора и 1-го умножителя, выход которого связан со входом (1 + 2)-го коммутатора, вход логической устройства подключен к первому входу первого кокмутатора, информационный вход устройства соединен со входами первого коммутато ра и элемента задержки, выход которого подключен ко входу первого умножителя и второму входу второго коммутатора, а выход устройства свя5зан с выходом (К + 1)-го коммутатора.

Источники информации, принятые во внимание при экспертизе

1.Карцев М.А. Арифметика цифро0вых машин. Наука, 1969,

с. 343 - 354.

2.Авторское свидетельство СССР № 425175, кл. G 06 F 7/38, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления многочленов | 1980 |

|

SU960806A1 |

| Устройство для возведения в степень | 1983 |

|

SU1087990A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Устройство для вычисления значений многомерного полинома | 1990 |

|

SU1742829A1 |

| Устройство для вычисления функции А @ | 1986 |

|

SU1383343A1 |

| Устройство для возведения в степень | 1986 |

|

SU1363205A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| УСТРОЙСТВО для ВОЗВЕДЕНИЯ ЧИСЕЛ В СТЕПЕНЬ ЧЕТЬ[РЕ | 1971 |

|

SU290279A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-24—Подача