11

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах, в которых необходимо получение с высокой достоверностью при наличии им- .пульсных помех во входных цепях и высоким быстродействием одновременно всех степеней числа с первой по N-ю,

Цель изобретения - повышение достоверности результата при наличии единичных сбоев в цепях входных данных и повышение быстродействия устройства.

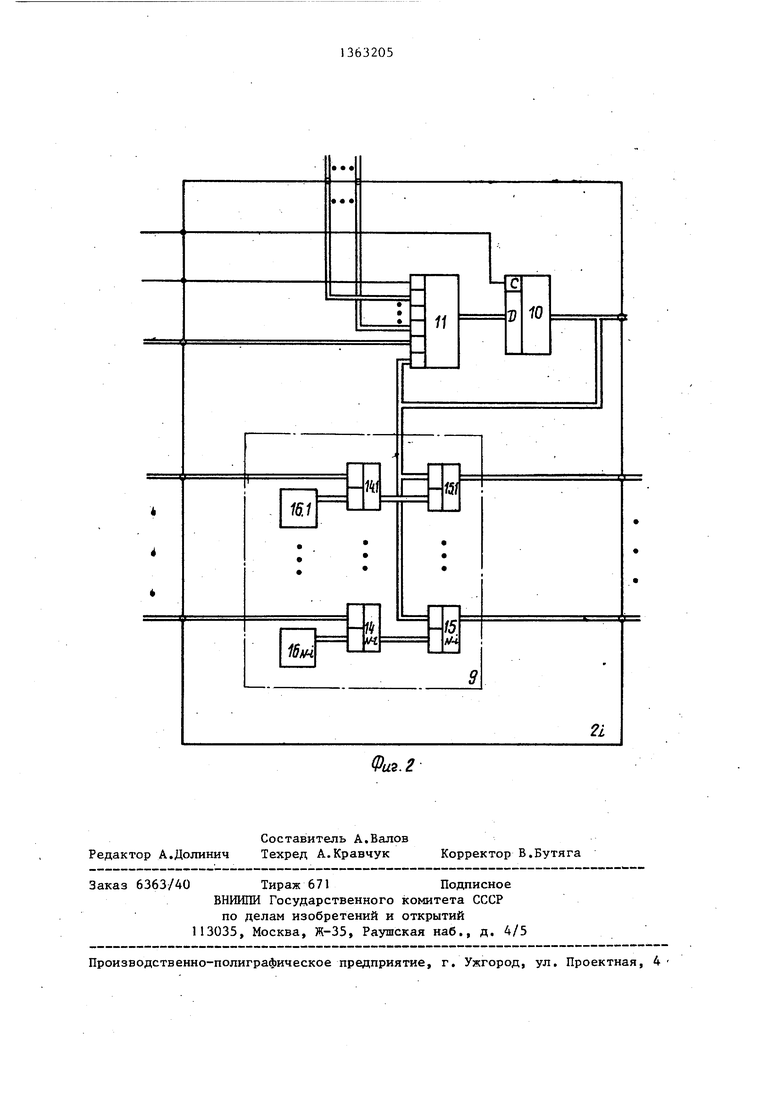

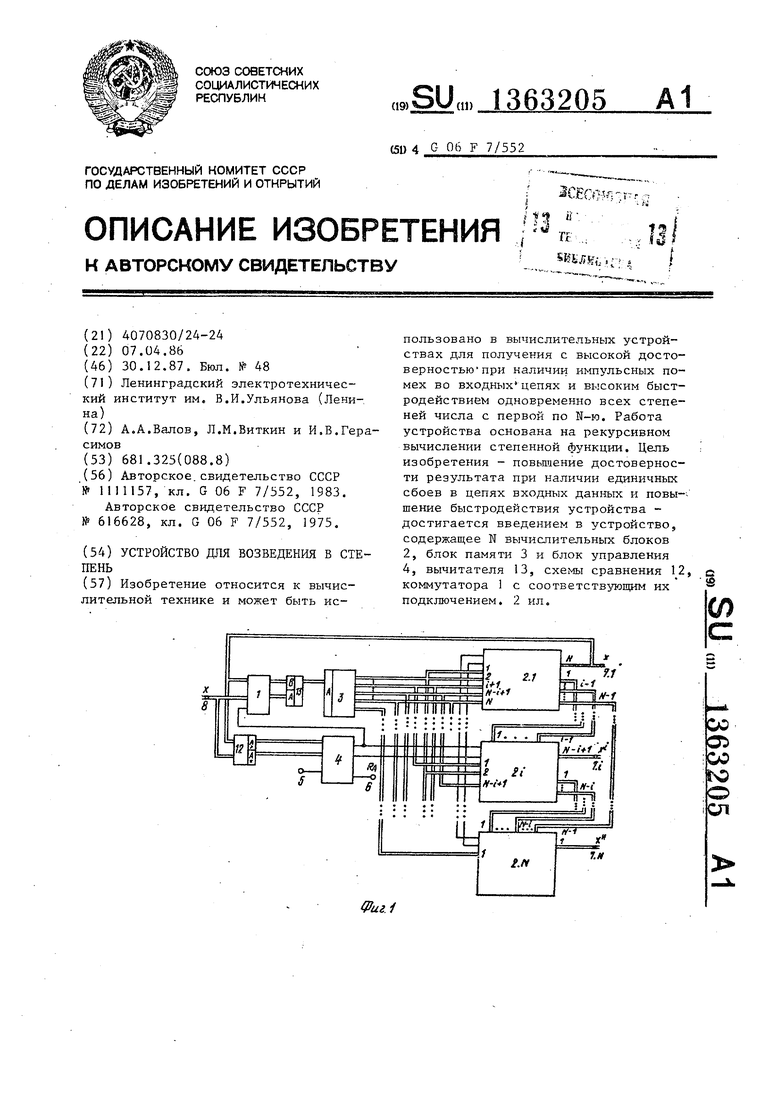

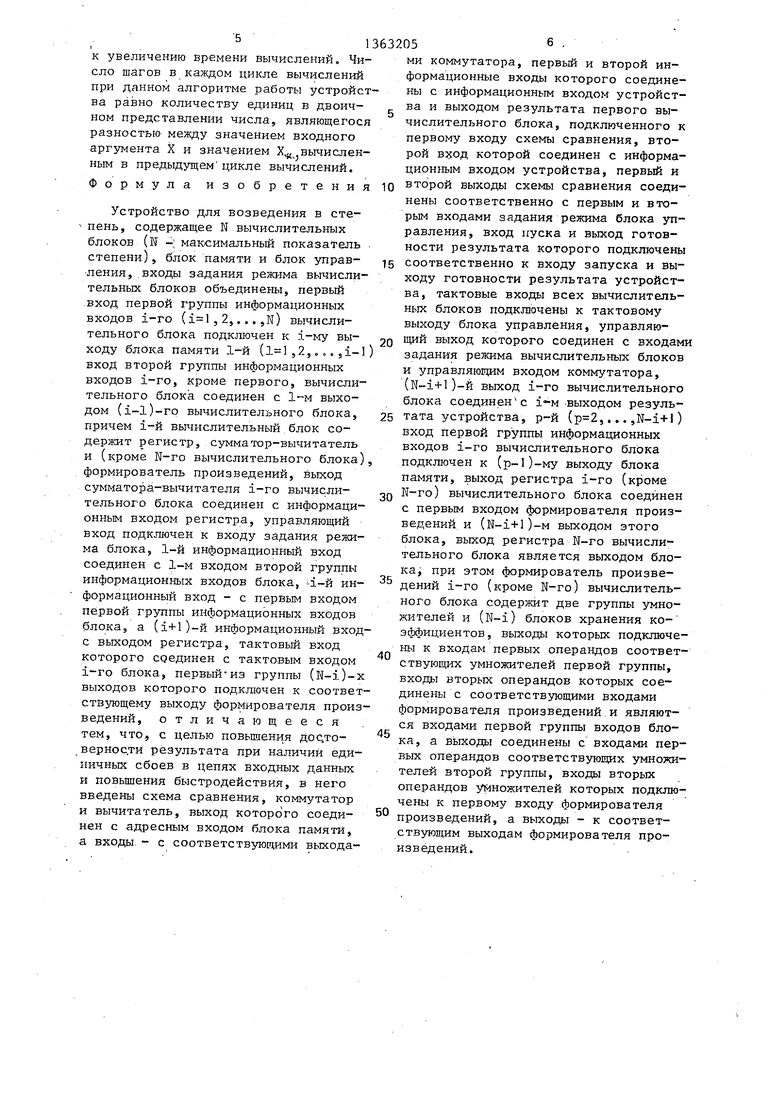

На фиг. 1 представлена структурна схема устройства; на фиг. 2 - функциональная схема вычислительного блока.

Схема (фиг. 1) содержит коммутато 1, N-вычислительньгх блоков 2.1-2.N блок 3 памяти, блок 4 управления, вход 5 запуска и выход 6 готовности результата устройства, выходы 7.1-7. результата устройства, информационный вход 8 устройства. На фиг, 2 изображены формирователь 9 произведения, регистр 10, сумматор-вычитатель

сравнения, вычитатель

11, схема 12 13, умножители 14.1-14.N первой группы, умножители 15.1-15.N второй группы, блоки 16.1-16.N-1 хранения коэффициентов. Все блоки и элементы устройства могут быть реализованы на известных микросхемах.

Работа устройства основана на ре- курсивном принципе вычисления степенной функции . Вычисление значения рекурсивно определенной степенной функции для заданного аргумента (основания -степени) является многошаговым процессом, так как при вычислении будет отслеживаться разность между исходным и заданным значением аргумента путем положительного или отрицательного наращивания исходного значения аргумента. За счет отслеживания разности удается повысить достоверность рекурсивных вычислений, так как ошибочное значение аргзадента можно рассматривать как его новое исходное значение.

Работа устройства основана на следующих рекурсивных соотношениях

Z Х-Х,

Z,- Хк.(1

И,

-i, z,o. о-р

(3.1) (3.2)

5

(Хк.)(Х,Г-Ь(1,Х,-2 2Ч2 Р {Х,)Ч г

.хГ . . (.О (хГ.)(х.А(1,Г.сГ-2 (х,Г

mst

д

m -pw

()(.) С(1кГ-с:-2

(АЛ)

(Хк ), (4.N)

где

гр k число сочетаний из 1 по т; номер старшего значимого разряда двоичного представления (ZK); номер шага вычислений.

начальные условия: (Х) 0, ,2,..,

« у1ч

Условия окончания вычислительного процесса: .

Установим соо тветствие между соотношениями (3), (4) и элементами устройства их реализующими.

Выбор значения осуществляется с помощью схемы 12 сравнения, единица на втором выходе которой появляется, если X больше Х. Вычисление соотношения (3.1) производится на вычита- теле 13, управляющим сигналом с выхода схемы 12 коммутатор 1 подключает на первый вход вычитателя 13 большее из.значений X, Х. Таким образом, результат вычитания всегда является положительной величиной. Реализация соотношений (4,l),...,(4.N) производится соответственно в вычислительных блоках 2.1,.,.,2.N, при зтом на вычислительные блоки 2.1,..., ...,2.N константы 2-1, ( 2) ,..., ...,( 2 поступают соответственно с первого, второго, ....,N-ro выходов блока 3 памяти.

0

В формирователе 9 произведений первого вычислительного блока 2.1 формируются все члены рекуррентных соотно- 5 шений (4.1)i...,(4.N), содержащие

значения С2Х|,,...,С ,..,

.-,fK1 ,

,(- )

..;.,(;;; . в формирователе 9 - произведений i-ro вычислительного блока 2.1-члены рекуррентных соотношений (4.1),...,(4.N), содержащие значения (Х,) :С:,,х;2-Р,.., ,, и т.д. При этом биномиальные коэффициенты Cj ,С,.. ,cj} хранятся в соответствующих блоках 16.1,...,16.N-1 5 хранения ктэзф циентов формирователя 9 произв.едений первого вычислительного 2.1 i коэффициенты Cj , ...,Сц - в соответствующих блоках 16.1,...,16.N-i хранения козффициентов формирователя 9 произведений i-r вычислительного блока 2.1 и т.д.

Устройство работает следующим образом.

. В исходном состоянии все регистры 10 вычислительных блоков 2.1,..., ...,2.N устройства находятся в нулевом состоянии. На входе 6 готовности результата сформирован единичный сигнал (). После поступления данных X на вход 8 данных устройства на вход 5 пуска устройства поступает стробирующий сигнал ST, запускающий генератор тактовых импульсов в блоке 4 управления. С входа 6 готовности результата устройства единичный сигнал снимается. Каждый цикл вычислений осуществляется следующим образом Сигнал со второго выхода схемы 12 сравнения, принимающий значение, равное единице, если (или нулю, если ), поступает на второй вход задания режима блока 4 управления. В соответствии с ним блок 4 управления сигналом с выхода режима настраивает соответствующие сумматоры-вы- читатели Г1 вычислительных блоков 2.1-2.N на суммирование (или вычитание). Сигнал с выхода режима блока 4 управления поступает также на управляющий вход коммутатора 1 и подключает входы к его выходам напрямую (или перекрестно, если на второй вход задания режима блока 4 управления поступает нулевой сигнал со второго выхода схемы 12 сравнения). В результате такого подключения на выходе вычитателя 13 появляется число, равное (х-Х). По результату вычитания, являющемуся адресом блока 3 памяти, в последнем производится вы7-Р

,-pN

борка констант , ,... ,2 , где р - номер старшего разряда, содержащего единицу при двоичном представлении адреса. Эти константы поступают на соответствующие входы первой группы входов вычислительных блоков 2.1,...,2.N. В формирователе 9 произведений каждого i-ro вычислительного блока производится умножение этих констант на величину X , снимаемую с выхода регистра-10 этого вычислительного блока, и на соответствующие биноминальные коэффициенты, содержащиеся в блоках 16.1,...,16.N-i хранения коэффициентов этого вычислителного блока. В результате проведенных операций на первом (N-i)-OM выходах

0

5

0

5

0

5

0

5

0

5

1-гс вычислительного блока формируются все слагаемые рекуррентных соотношений (4.),,..,(4.N), содержащие значения Xj, которые поступают на соответствующие входы второй группы входов вычислительных блоков 2.1+1,.., ..,2.N. Таким образом, на входы с первого по (1-1)-и сумматора-вычита- теля 11 1-го вычислительного блока поступают слагаемые рекуррентного соотношения (4.1), содержащие значения Хц соответственно в степенях с первой по (1-1)-ю, на 1-й вход сумма тора-вычита теля 1 1 - константа с первого входа констант 1-го вычислительного, блока, на (1+1)-и вход - значения Х с выхода регистра 10. По тактовому сигналу с блока 4 управления результат суммирования записывается в регистр 10. (К+1)-й шаг вычисления закончен. В результате проведенных опера1 ий значение X увеличи- лось (или уменьшилось) на величину (ГП . Вычисления на следздощем шаге производятся аналогично.

После очередного шага значения Xj, станет равным значению входного аргумента X. В этом случае единичный сигнал с первого выхода схемы 12 сравнения поступает на первый вход задания режима блока 4 управления, который прекращает выработку тактовых импульсов и формирует единичный сигнал на выходе готовности результата. Цикл вычислений закончен. На выходах 7.1,...,7.N результата находятся все степени (с первой по N-ю для значения входного аргумента) основания степени. Следующий цикл вычислений начинается после йоступле- ния на вход 5 пуска устройства запускающего сигнала ST.- При этом за исходные значения Х принимаются значения, вычисленные в предыдущем цикле вычислений.

.1 .

При наличии единичных сбоев во

входных цепях данных, значение входного аргумента X может измениться. На следующем шаге изменится и значение XJ на величину , отслеживая изменение X. Так как к началу очередного шага значение X восстановится, то на этом шаге восстановится и прежнее значение ХЧ

Таким образом, единичный сбой, приведший к искажению значения входного аргумента, не приведет к искажению результата, а может привести лишь

к увеличению времени вычислений. Число шагов в каждом цикле вычислений при данном алгоритме работы устройства равно количеству единиц в двоичном представлении числа, являющегося разностью- между значением входного аргумента X и значением Х вычисленным в предыдущем цикле вычислений.

Формула изобретения

Устройство для возведения в степень, содержащее N вычислительных блоков (N -; максимапьньй показатель - степени), блок памяти и блок управления, входы задания режима вычислительных блоков объединены, первый вход первой группы информационных входов i-ro (,2,...,N) вычислительного блока подключен к 5.-ну выходу блока памяти 1-й (,2,.,.ji-l) вход второй группы информационных входов i-ro, кроме первого, вычислительного блока соединен с 1-м выходом (i-l)-rp вычислительного блока, причем i-й вычислительный.блок содержит регистр, сумматор-вычитатель и (кроме N-ro вычислительного блока), формирователь произведений, выход сумматора-вычитателя 1-го вычислительного блока соединен с информационным входом регистра, управляющий вход подключен к входу задания режима блока, 1-й информационный вход соединен с 1-м входом второй группы

ми коммутатора, первый и второй информационные входы которого соединены с информационньш входом устройства и выходом результата первого вычислительного блока, подключенного к первому входу схемы сравнения, второй вход которой соединен с информа- ЦИОН1ШМ входом устройства, первый и

10 второй выходы схемы сравнения соединены соответственно с первым и вторым входами задания режима блока управления, вход пуска и выход готовности результата которого подключены

(5 соответственно к входу запуска и выходу готовности результата устройства, тактовые входы всех вычислительных блоков подключены к тактовому выходу блока управления, управляю2Q щий выход которого соединен с входами задания режима вычислительных блоков и управляющим входом коммутатора, ()-й выход i-ro вычислительного блока соединение i-м -выходом резуль25 тата устройства, р-й (,...,N-i+l) вход первой группы информационных входов i-ro вычислительного блока подключен к (р-1)-му выходу блока памяти, выход регистра i-ro (кроме

2Q N-ro) вычислительного блока соединен с первым входом формирователя произведений, и (N-i+l)-M выходом этого блока, выход регистра N-ro вычислительного блока является выходом блока, при этом формирователь произве-

информационных входов блока, -i-й ин- 5 i-ro (кроме N-ro) вычислитель- формационный вход - с первым входом ного блока содержит две группы умно- первой грзшпы информационных входов жителей и (N-i) блоков хранения ко- блока, а (i+l)-fi информационный вход- эффициентов, выходы которых подключе- с выходом регистра, тактовый вход которого сдединен с тактовым входом i-ro блока, первый ИЗ группы (N-i)-x выходов которого подключен к соответ- стзующему выходу формирователя произведений, отличающееся тем, что, с целью повьшения дос.то40

45

ны к входам первых операндов соответствующих умножителей первой группы, входы вторых операндов которых соединены с соответствующими входами формирователя произведений и являются входами первой группы входов блока, а выходы соединены с входами первых операндов соответствующих умножителей второй группы, входы вторых операндов умножителей которых подключены к первому входу формирователя произведений, а выходы - к соответствующим выходам формирователя произведений.

верности результата при наличии единичных сбоев в цепях входт-гых данных и повьшения быстродействия, в него введены схема сравнения, коммутатор и вычитатель, выход которого соединен с адресным входом блока памяти, а входы - с соответствующими выходами коммутатора, первый и второй информационные входы которого соединены с информационньш входом устройства и выходом результата первого вычислительного блока, подключенного к первому входу схемы сравнения, второй вход которой соединен с информа- ЦИОН1ШМ входом устройства, первый и

второй выходы схемы сравнения соединены соответственно с первым и вторым входами задания режима блока управления, вход пуска и выход готовности результата которого подключены

соответственно к входу запуска и выходу готовности результата устройства, тактовые входы всех вычислительных блоков подключены к тактовому выходу блока управления, управляющий выход которого соединен с входами задания режима вычислительных блоков и управляющим входом коммутатора, ()-й выход i-ro вычислительного блока соединение i-м -выходом результата устройства, р-й (,...,N-i+l) вход первой группы информационных входов i-ro вычислительного блока подключен к (р-1)-му выходу блока памяти, выход регистра i-ro (кроме

N-ro) вычислительного блока соединен с первым входом формирователя произведений, и (N-i+l)-M выходом этого блока, выход регистра N-ro вычислительного блока является выходом блока, при этом формирователь произве-

i-ro (кроме N-ro) вычислитель- ного блока содержит две группы умно- жителей и (N-i) блоков хранения ко- эффициентов, выходы которых подключе-

i-ro (кроме N-ro) вычислитель- ного блока содержит две группы умно- жителей и (N-i) блоков хранения ко- эффициентов, выходы которых подключе-

ны к входам первых операндов соответствующих умножителей первой группы, входы вторых операндов которых соединены с соответствующими входами формирователя произведений и являются входами первой группы входов бло

ка, а выходы соединены с входами первых операндов соответствующих умножителей второй группы, входы вторых операндов умножителей которых подключены к первому входу формирователя произведений, а выходы - к соответствующим выходам формирователя произведений.

Редактор А.Долинич

Составитель А.Валов Техред А.Кравчук

Заказ 6363/40 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фи2.2

Корректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1986 |

|

SU1322271A1 |

| Адресное устройство для цифрового фильтра | 1985 |

|

SU1298859A1 |

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Устройство для вычисления функций | 1987 |

|

SU1411775A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1348815A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1388891A1 |

| Устройство для вычисления свертки | 1989 |

|

SU1688259A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для вычисления многочленов | 1980 |

|

SU960806A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах для получения с высокой достоверностью при наличии импульсных помех во входных цепях и высоким быстродействием одновременно всех степеней числа с первой по N-ю. Работа устройства основана на рекурсивном вычислении степенной функции. Цель изобретения - повьпиение достоверности результата при наличии единичных сбоев в цепях входных данных и повы- шение быстродействия устройства - достигается введением в устройство, содержащее N вычислительных блоков 2, блок памяти 3 и блок управления 4, вычитателя 13, схемы сравнения 12, коммутатора 1 с соответствующим их подключением. 2 ил. сл

| Устройство для возведения чисел в @ -ю степень | 1983 |

|

SU1111157A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для возведения в степень | 1975 |

|

SU616628A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-04-07—Подача