(21)4128950/24-24

(22)03.10.86

(46) 23.03.88. Бюл. №11 (72) Е.Я.Ваврук, А.А.Мельник и И.Г.Цмоць

(53)681.325 (088.8)

(56).Авторское свидетельство СССР №752334, кл. G 06 F 7/552, 1980.

Авторское свидетельство СССР № 1087990, кл.С 06 F 7/552, 1983.

(54)УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНК1ДИИ А

(57)Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных устройствах обработки цифровой информации для вычисления функции

А . Цель изобретения - уменьшение

аппаратурных затрат. Сущность изобретения заключается в том, что в предлагаемом устройстве в каждом вычислительном блоке производится анализ К разрядов, что позволяет уменьшить количество вычислительных блоков в К раз. Устройство содержит блоки 4.1-4.(2 -2) возведения в степень (где К - количество анализируемых разрядов показателя степени в одном вычислительном блоке), коммутатор 5, L вычислительных блоков 6

, (logira) + l-K

(L - ---- где К - количестк

во анализируемых разрядов в группе, m - показатель степени), каждый из которых содержит регистры 7 - 9, коммутатор 10, блок 11 возведения в 2 -ю степень, умножитель 12. 1 ил.

т

ел

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень | 1988 |

|

SU1718217A1 |

| Устройство для возведения в степень | 1983 |

|

SU1087990A1 |

| Устройство для возведения в степень | 1978 |

|

SU752334A1 |

| Устройство для возведения в степень | 1984 |

|

SU1179327A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения в избыточной системе счисления | 1984 |

|

SU1229755A1 |

| Устройство для возведения в степень | 1986 |

|

SU1363205A1 |

00 00

со со

4:

со

11

Изобретение относится к вычислительной технике и может быть исполь- зёвано в высокопроизводительных устройствах обработки цифровой информа- 1ЩИ для вычисления функции А.

Цель изобретения - уменьшение аппаратурных затрат.

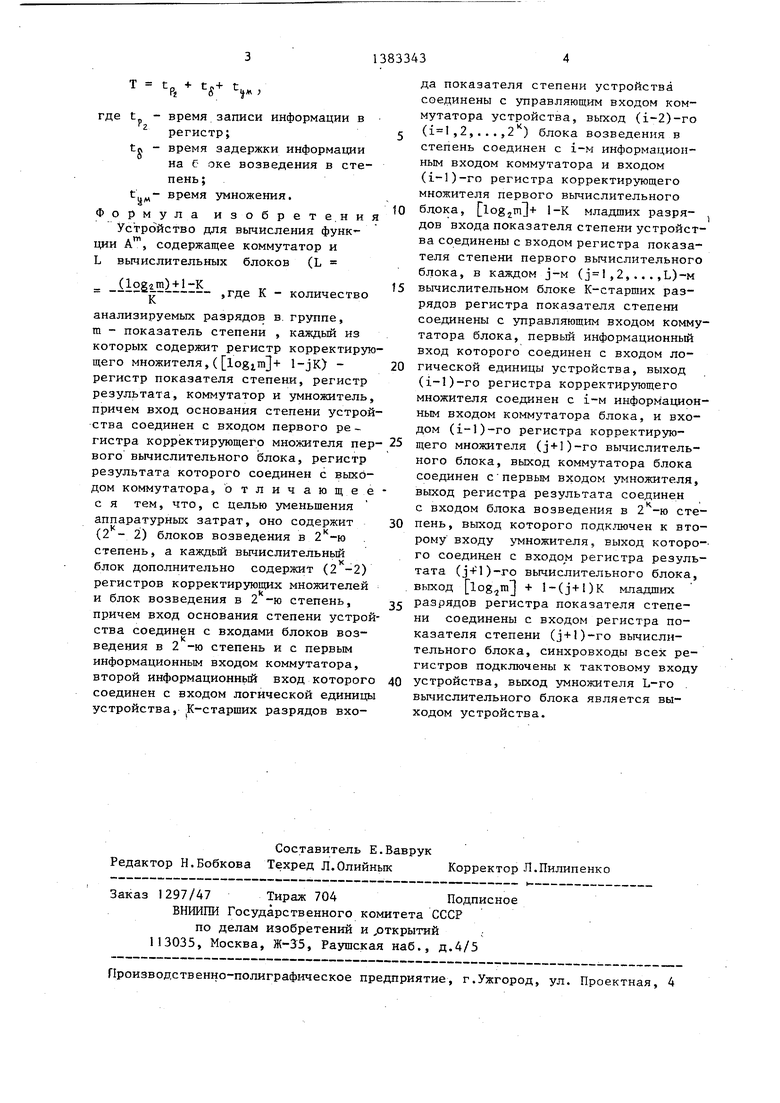

На чертеже представлена функциональная схема устройства.

На схеме обозначены тактовый

вход 1, вход 2 показателя степени и вход 3 основания степени устройства, блоки 4,- 4 к возведения в

степень (где К - количество анализируемых разрядов показателя степени в одном вычислительном блоке), коммутатор 5, L вычислительных блоков 6, каждый из которых содержит регистр 7 показателя степени, регистры 8,- , корректирующего мнжителя, регистр 9 результата, ком- мутатор 10, блок 11 возведения в .

2 -ю степень, умножитель 12, вход логической единицы устройства, выхо

14 устройства. I . .

В предлагаемом устройстве используется алгоритм возведения числа А в га-ю степень, при котором показатель степени разбивается на группы по К разрядов с последовательным анализом данных групп слева направо и вьшолнением при предьщущего пень с последующим умножением его н корректирующий множитель, Для каждо анализируемой группы корректирующий множитель равен результату возведения числа А в степень, равную числу записанному в данной группе. При анализе первой группы предьщущий результат принимается равным единице.

Устройство работает следующим образом.

Основание степени с входа 3 постпает на входы блоков 4,- .. воз- в едения в степень,

этом возведения результата в 2 -ю стегде в каждом (i--2)-M (i 1 ,2,. . .,2)блоке 4,-.2

оно возводится в (1-1)-ю степень. Старшие К разрядов показателя степени с входа 2 поступают на управляющий вход коммутатора 5 и управляют его переключением так, что при нуле на управляющем входе на выход поступает информация с первого входа,, при единице - информация с второго входа и т.д.

8

0

В первом такте в регистры 7,8,, 8,. . , , и 9 первого вьмисли- тельного блока 6, производится запись информации, причем в регистры 7 и 9 записываются соответственно показатель степени без К старших разрядов и информация с выхода коммутатора 5 (корректирующий множитель а в регистры 8, ,82,...,.,j - основание степени и информация с выходов блоков 4,,42,.., возведения в степень.

В первом вычислительном блоке 6,

15 информация с выхода регистра 9 (предыдущий результат) на блоке 11 возводится в 2 -ю степень и поступает на вход умножителя 12, где умножается на информацию с выхода коммута0 тора 10 (корректирующий множитель). Информация с К старших разрядов регистра 7 управляет переключением коммутатора 10 так, что при нуле на управляющем входе на выход поступа5 ет информация с первого входа, при единице - информация с второго входа и т.д. Результат умножения с выхода умножителя 12 поступает на вход регистра 9 второго вычислительного бло0 ка 6...

Во втором такте производится перезапись информации с выходов первого вычислительного блока 6, во второй вычислительный блок 6. Одно5

в первый вычислительный

новые элемен- массива. Во вто- блоке 6.

временно

блок 6, записываются

ты обрабатьшаемого ром вычислительном блоке 6 информация с выхода регистра 9, проходя

0 через блок 11 возведения в степень, возводится в 2 -ю степень и поступает на вход умножителя 12, где умножается на информацию с выхода коммутатора 10. Информация на выходе ком-.

5 мутатора 10 задается К старшими раз- рядами регистра 7.

В последзтощих тактах устройство работает аналогично, т.е. в каждом вычислительном блоке 6 выполняется

0 одна итерация алгоритма возведения в степень. Операция возведения в. степень вьтолняется при прохождении операндами всех вычислительных блоков 6.

5 Устройство работает по конвейерному принципу. Его быстродействие определяется временем выполнения одной итерации, т.е. тактом конвейера. Это время равно

Т tg t,

где t - время записи информации в

регистр;

ti - время задержки информации на б оке возведения в степень;t - время умножения.

Z

Формула изобретения

Устройство для вычисления функ - ции А, содержащее коммутатор и L вычислительных блоков (L

(log2ra) + l-K ...

в-,где К - количество

К

анализируемых разрядов в. группе, m - показатель степени , каждый из которых содержит регистр корректирующего множителя, ( 1-jK) - регистр показателя степени, регистр результата, коммутатор и 5 множитель, причем вход основания степени устройства соединен с входом первого ре - гистра корректирующего множителя первого вычислительного блока, регистр результата которого соединен с выходом коммутатора, отличающее с я тем, что, с целью уменьшения аппаратурных затрат, оно содержит (2 - 2) блоков возведения в 2 -ю

степень, а каждый вычислительньй

V

блок дополнительно содержит (2 -2) регистров корректирующих множителей

и блок возведения в 2 -ю степень, причем вход основания степени устройства соединен с входами блоков возведения в 2 -ю степень и с первым информационным входом коммутатора, второй информационньй вход которого соединен с входом логической единицы устройства, К-старших разрядов входа показателя степени устройства соединены с управляющим входом коммутатора устройства, выход (i-2)-ro

(,2,...,2 ) блока возведения в степень соединен с i-м информационным входом коммутатора и входом (i-l)-ro регистра корректирующего множителя первого вычислительного

блока, LlogjmJ-b 1-К младших разрядов входа показателя степени устройства соединены с входом регистра показателя степени первого вычислительного блока, в каждом j-м (,2,...,Ь)-м

вычислительном блоке К-старших разрядов регистра показателя степени соединены с управляющим входом коммутатора блока, первый информационный вход которого соединен с входом логической единицы устройства, выход (i-l)-ro регистра корректирующего множителя соединен с i-м информационным входом коммутатора блока, и входом (i-l)-ro регистра корректирующего множителя (j+l)-ro вычислительного блока, выход коммутатора блока соединен с первым входом умножителя, выход регистра результата соединен с входом блока возведения в 2 -ю степень, выход которого подключен к второму входу умножителя, выход которо-- го соединен с входо м регистра результата ()-ro вычислительного блока, вьпсод + l-(j+l)K младших

разрядов регистра показателя степени соединены с входом регистра показателя степени (j+l)-ro вычислительного блока, синхровходы всех регистров подключены к тактовому входу

устройства, выход умножителя L-ro . вычислительного блока является выходом устройства.

Авторы

Даты

1988-03-23—Публикация

1986-10-03—Подача