Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных устройствах обработки цифровой информации для вычисления функций . ..

Известно устройство для вычисления показательных функций у N, содержащее блок управления, блок управления, блок суммирования, сумматор, эле1у1ент ИЛИ, т-1 вычислительных Кодов, каждый из которых содержит умножитель, элемент И, элемент ИЛИ и блок суммирования, который содержит регистр, сумматор и коммутатор Cl3.,

Наиболее близким к предлагаемому является устройство для возведения в, степень, содержащее коммутатор, К вычислительных блоков, каждый из которых содержит коммутатор, квайратор, умножитель (где , т-показатель степени), причем и каждом вычислительном блоке выход квадратора соединен с первым информационным входом коммутатора Lll.

Недостатком известных устройств является низкое быстродействие.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для возведения в степень, содержащее коммутатор, К вычислительных блоков каждый из которых содержит коммутатрр, квадратор, умножитель (где K teg-jir, - показатель степени), причем в каждом вычислительном блоке выход квадратора соединен с первым инфор мационным входом умножителя и с первым информационным входом коммутатора, введены элемент НЕ, а в кажый вычислительный , блок введены регистр основания степени, регистр показателя степени и регистр результата, причем первый информационный вход коммутатора устройства соединен с-информаци 7нным входом регистра основания степени и входом основания степени устройства, второй информационный вход коммутатора устройства соединен с шиной логиеской единицы устройства, вход показателя степени устройства соединен с входом элемента НЕ, первым правляющим входом коммутатора устройства и информационным входом егистра показателя степени перого вычислительного блока, выход лемента НЕ соединен с вторым упавляющим входом коммутатора устройтва, тактовые входы регистра осноания Степени, регистра результата регистра показателя степени кажого вычислительного блока соединены с тактовым входом устройства, выход

регистра основания степениi-го

вычислительного блока ,K) соединен с вторым информационным входом умножителя, i-го вычислительного блока, выход умножителя i-го-вычислительного блока соединен с первым информационным входом коммутатора 5 1-го вычислительного блока, выход коммутатора устройства с информациЪнным входом регистра результата первого вычислительного блока, выход регистра результата 0 i-го вычислительного блока соединен с информационным входом квадратора этого вычислительного блока, выхсд регистра основания степени i-го вычислительного, блока соединен с ин5 формационным входом регистра основания степени (1+1)-го вычислитель. ного блока, выход коммутатора i-ro вычислительного блока соединен с информационным входом регистра результата (i+l)-ro вычислительного блока, прямой и инверсный выходыi старшего разряда регистра показателя . степени i-го вычислительного блока соединены соответственно с первым и вторым управляющими входами ком мутатора 1-го вычислительного блока, выходы (K-i)-x младших разрядов регистра показателя степени i-го вычислительного блока соеДинены соответственно с (К-1)-ми старпими

0 разрядами регистра показателя степени (1+1)-го вычислительного блока, выход коммутатора последнего вычислительного блока является выходом устройства.

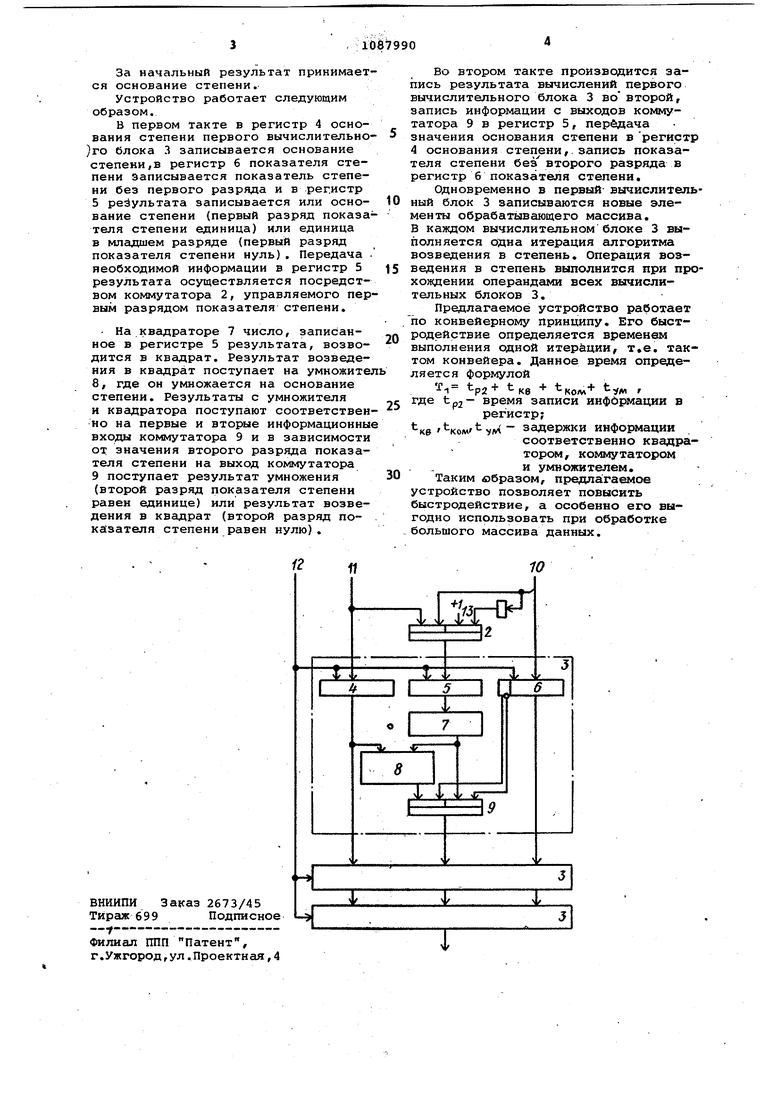

5 На чертеже приведена структурная схема предлагаемого устройства. . Устройство содержит элемент 1.НЕ, коммутатор 2, К вычислительных блоков 3, каждый из которых содержит

Q регистр 4 основания степени, регистр 5 результата, регистр б показателя степени, квадратор 7, умножитель 8, коммутатор 9, вход 10 показателя степени устройства, вход 11 основа. кия степени устройства, тактовый

вход 12 устройства, шину 13 логической единицы устройства.

Количество вычислительных блоков

3 определяется по формуле m ,

.т.е. К меньшее целое значение выра0 жения 8о,,т .

В устройстве для возведения в степень используется бинарный способ сокращения количества умножений. В показателе степени, записанном в

5 двоичной системе счисления, определяется крайндя левая единица. При последовательном чтении цифр слеванаправо от этой единицы выполняются операции: если очередная цифра нуль,

О то результат предыдущей операции

возводится в квадрат; если очередная цифра единица, то предыдущий результат возводится в квадрат, а затем умножается на основание сте5 пени. За начальный результат принимает ся основание степени. Устройство работает следующим образом. В первом такте в регистр 4 основания степени первого вычислительно }го блока 3 записывается основание степени,в регистр б показателя степени Записывается показатель степени без первого разряда и в регистр 5 результата записывается или основание степени (первый разряд показа теля степени единица) или единица в младшем разряде (первый разряд показателя степени нуль). Передача необходимой информации в регистр 5 результата осуществляется посредством коммутатора 2, управляемого пер вым разрядом показателя степени. На квадраторе 7 число, записанное в регистре 5 результата, возводится в квсщрат. Результат возведения в квадрат поступает на умножите Б, где он умножается на основание степени. Результаты с умножителя и квадратора поступают соответствен но на первые и вторые информационны входы коммутатора 9 и в зависимости от значения второго разряда показателя степени на выход коммутатора 9 поступает результат умножения (второй разряд показателя степени равен единице) или результат возведения в квадрат (второй разряд показателя степени равен нулю).

/ ft

10 Во втором такте производится запись результата вычислений первого вычислительного блока 3 вовторой, запись информации с выходов коммутатора 9 в регистр 5, передача значения основания степени в регистр 4 основания степени,. запись показателя степени безвторого разряда в регистр 6 показателя степени. Одновременно в первый вычислительный блок 3 записываются новые элементы обрабатывающего массива. В каждом вычислительном блоке 3 выполняется одна итерация алгоритма возведения в степень. Операция возведения в степень выполнится при прохождении операндами всех вычислительных блоков 3. Предлагаемое устройство работает по конвейерному принципу. Его быстродействие определяется временем выполнения одной итерации, т.е. тактом конвейера. Данное время определяется формулой Г, tp2 + t Kg + t,, , где tpj- время записи инфйрмации в регистр; задержки информации соответственно квадратором, коммутатором и умножителем. Таким сбразом, предлагаемое устройство позволяет повысить быстродействие, а особенно его выгодно использовать при обработке большого массива данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень | 1984 |

|

SU1179327A1 |

| Устройство для возведения в степень | 1978 |

|

SU752334A1 |

| Устройство для вычисления многочленов | 1980 |

|

SU960806A1 |

| Устройство для вычисления функции А @ | 1986 |

|

SU1383343A1 |

| Устройство для возведения в степень | 1988 |

|

SU1718217A1 |

| Вычислительное устройство | 1983 |

|

SU1130862A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| УСТРОЙСТВО для ВОЗВЕДЕНИЯ ЧИСЕЛ В СТЕПЕНЬ ЧЕТЬ[РЕ | 1971 |

|

SU290279A1 |

| Устройство для возведения в степень | 1986 |

|

SU1363205A1 |

| Устройство для вычисления значений многомерного полинома | 1990 |

|

SU1742829A1 |

УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В СТЕПЕНЬ, содержащее коммутатор, К вычислительных блоков, каждый из которых содержит коммутатор, квадрат тор, умножитель (где , m-показатель степени), причем в каждом вычислительном блоке выход квадратора соединен с первым информационным входом умножителя и с первым информационным входом комму.татора, отличающееся тем; что, с целью повышения быстродействия, в устройство введены элемент НЕ, а в каждый вычислительный блок введены регистр основания степени, регистр показателя степени и регистр результата, причем первый информационный вход коммутатора устройства соедднен с информационным входом регистра основания степени и входом основания степени устройства, второй информационный вход коммутатора устройства соединен с шиной логической единицы устройства, вход показателя степени устройства соединен с входом элемента НЕ,первым управляющим входом коммутатора устройства и информационным входом регистра показателя степени первого вычислительного блока, выход элемента НЕ соединен с вторым управляющим входом коммутатора устройства, тактовые входы регистра основания степени, регистра результата и регистра показателя степени Каждого вычисли тельного блока соединены с тактовым входом устройства,, выход регистра основания степени i-го вычислительного блока (,К) соединен с вторым информационным входом умножителя 1-го вычислительного блока, выход умножителя 1-го вычислительного блока соединен с первым информационным входом коммутатора i-го вычислительного блока, выход коммутатора-устройства соединен с информационным входом регистра результата первого вычислительного блока,, выход регистра результата i-го вычислительного блока соединен с ин(Л формационным входом квадратора этого вычислительного блока, выход регистра основания степени i-го вычислительного блока соединен с информационным входом регистра основания степени (i-fl)-ro вычислительного блока, выход коммутатора i-го вычислительного блока-соединен с информационным входом регистра результата (i+l)-ro вычислительного оо блока, прямой и инверсный выходы старшего разряда регистра показасо со теля хзтепени i-ro вычислительного блока соединены соответственно с первым и BTOfftjM управляющими входами коммутатора i-ro вычислительного блока, выходы (K-i)-x младших разрядов регистра показателя степени i-го вычислительного блока соединены соответственно с (К-1)-ми старшими разрядами регистра показателя степени (i+l)-ro .вычислительного блока, выход коммутатора последнего вычислительного блока является выходом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления показательных функций | 1976 |

|

SU643887A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для возведения в степень | 1978 |

|

SU752334A1 |

Авторы

Даты

1984-04-23—Публикация

1983-01-11—Подача