1

Изобретение относится к автоматике и вычислительной технике и может найти применение при разработке счетчиков, обладающих эффективной системой контролй.

Известны счетчики, осуществляющие контроль путем сравнения четности кода, находящегося в контрольном счетчике с четностью кода, находящегося JQ в контролируемом счетчике 1.

Однако такой контроль является неполным, так как не может зафиксировать ошибки переноса, возникающие при работе счетчика. -с

Наиболее близким техническим решением к изобретению является двоичный счетг ик 2 .

Для контроля в схеме имеется дополнительный контрольный разряд/ на- jn чальное состояние которого устанавливается таким, чтобы сумма единиц содержимого счетчика вместе с собственным состоянием была четной. Для определения четности или нечетности суммы25 единиц счетчика необходим диодный дешифратор (схема свертки).

Дальнейшее изменение четности происходит в зависимости от места разряда и изменения его состояния при

жении и вычитании, а для этого необходима схема определения места переключения четности при сложении и вычитании. Такой контроль не определяет на каком этапе работы счетчика произошла ошибка, а, следовательно, распознать место сбоя.

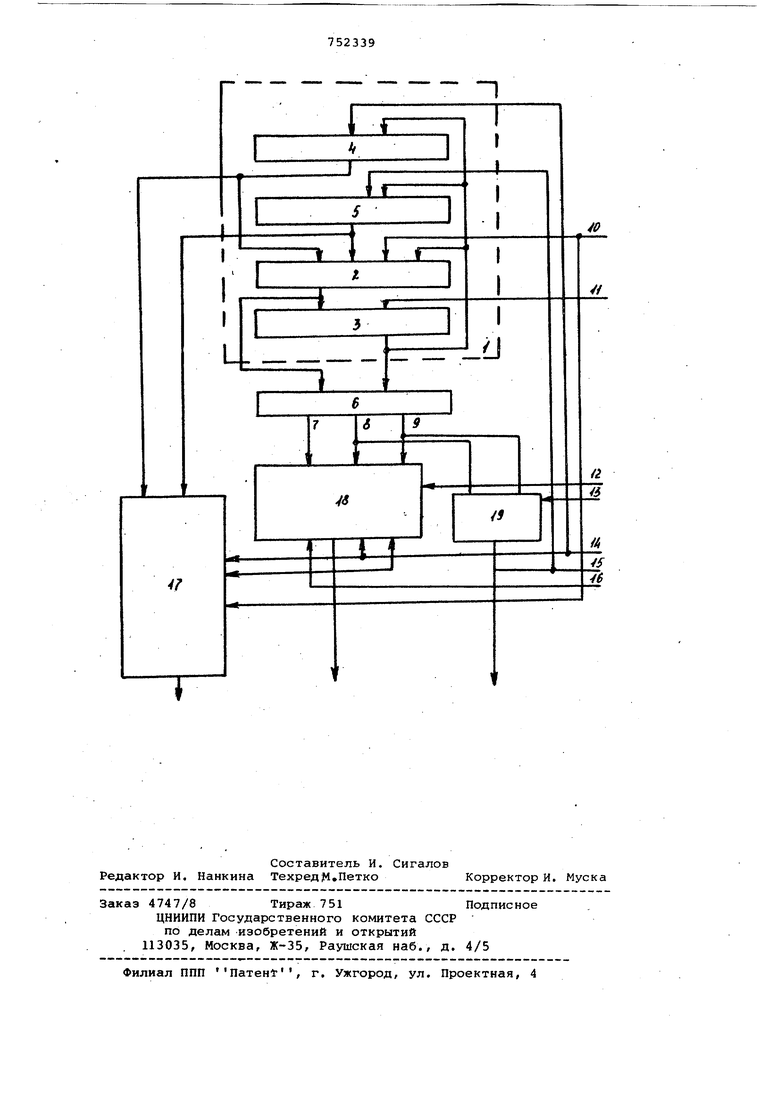

Цель изобретения - увеличение эффективности контроля, достижение более полного контроля реверсивного двухтактного двоичного счетчика на потенциальных элементах. Поставленная цель достигается тем, что в реверсивный двоичный счетчик с контролем, содержащий основной и вспокюгательный.регистры, узел переноса, узел эаема, причем входы сложения и вычмтания счетчика соединены соответственио с первыми входами узла переноса и узла эаема, выход которого соединен с первым входом основного регистра, выход основного регистра соединен с. информационным входом вспомогательного регистра, выход которого соединен со вторыми входами основного регистра, узла эаема и узла переноса, выход узла переноса соединен с третьим входом основного регистра, первый и второй синхронизационные входы счетчика соединены соответственно с четвертым входом основного регистра, со вторым входом вспомогательного регистра, введены.схема сравнения, де шифратор ошибок передачи, дешифратор ошибок сложения, дешифратор ошибок переноса, причем первый и второй входы дешифратора ошибок переноса соединены соответственно с выходами узла переноса, узла заема, первый и второй входы схемы сравнения соедине соответственно с выходами основного и вспомогательного регистров, первый, второй и третий выводы схемы сравнения соединены соответственно с первым, вторым и третьим входами дешифратора ошибок сложения, второй и третий выходы схемы сравнения соединены соответственно с первьлм и вторым входом дешифратора ошибок передачи, первый синхронизационный вход счетчика соединен с третьим входом дешифратора ошибок переноса, выход которого является первым выхо дом устройства, вход сложения счетчика соединен с первыми управляюшим входами дешифратора ошибок переноса и дешифратора ошибок сложения, вход вычитания счетчика соединен со вторыми управляющими входами дешифратора ошибок переноса и дешифратор ошибок сложения, вход вычитания сче чика соединен со вторыми управляющи ми входами дешифратора ошибок переноса и дешифратора ошибок сложения, тактовый вход счетчика соединен с третьим управляющим входом дешифратора ошибок сложения, третий и четвертый синхронизационные входы счетчика соединены соответственно с.первыми синхронизационными входами дешифратора ошибок сложения и дешифратора ошибок передач, выходы дешифратора ошибок сложения и дешиф ратора ошибок передач являются соот ветственно вторым и третьим выходом счетчика. На чертеже представлена блок-схе ма реверсивного двоичного счетчика с контролем. Реверсивный двоичный счетчик с контролем содержит счетчик 1, состоящий из основного регистра 2, вспомогательного регистра 3, узла 4 переноса, узла 5 заема, схему 6 сравнения с выходами 7-9, синхронизационные входы 10-13, управляющие входы 14-16, дешифратор 17 ошибок переноса, дешифратор 18 ошибок сложения, дешифратор 19 ошибок передачи. Счетчик работает в двух режимах суммирования и вычитания. Режим работы счетчика устанавлив ется по сигналам, поступающим по входам 14-16. При единичном .значени сигнала на входе 14 счетчик работае в режиме суммирований. При единично значении сигнала на входе 15 счетчик работает в режиме вычитания. Тактирующий сигнал на входе 16 стробирует работу счетчика при сложении и вычитании. Наличие сигнала переноса при сложении или сигнала заема при вычитании формируется в дешифраторе 17 ошибок переноса. Каждый период работы двухтактного реверсивного двоичного счетчика с контролем делится на 4 фазы. Для этого по входам 10-13 поступают четыре взаимосмещенных серии синхроимпульсов. При поступлении синхроимпульсов по входу 10 происходит изменение состояния основного регистра. При поступлении синхроипульсов по входу 12 Обнаруживается ошибка, которая может при этом возникнуть. При поступлении синхроимпульсов по входу 11 происходит передача содержимого основного регистра во вспомогательный. При поступлении синхроимпульсов по входу 13 обнаруживается ошибка, которая может при этом возникнуть. Сигналы с выходов основного и вспомогательного регистров поступают в схему 6 сравнения, где производится сравнение из содержимого и в результате появляется единица на одном из выходов 7-9 схемы 6 сравнения. Если единичный сигнал на выходе 9, то содержимое вспомогательного регистра меньше основного. Если единичный сигнал на выходе 8, то содержимое вспомогательного регистра больше основного. Если единичный сигнал на выходе 7, то содержимое этих регистров равно. При поступлении сигнала по входу 10в зависимости от режима работы счетчика происходит добавление или вычитание единицы в основном регистре счетчика. Так как еще не произошла передача содержимого основного регистра во вспомогательный, то в этой фазе работы счетчика содержимое вспомогательного регистра не равно основному, при сложении оно должно быть меньше основного, при вычитании - больше. Отсутствие этого условия является ошибкой, которая обнаруживается дешифратором 18 ошибок сложения. При поступлении сигнала по входу 11содержимое основного регистра передается во вспомогательный и с этого момента они равны друг другу до поступления следующего импульса по входу 11. При несоблюдении этого условия ошибка обнаруживается дешифратором 19 ошибок передачи. В предлагаемом реверсивном счетчике с контролем фиксируются ошибки, которые могут возникнуть в различных фазах работы счетчика. Этим обеспечивается более полный контроль работы счетчика и упрощается определение места сбоя, что особенно важно при эксплуатации устройств, работающих в реальном масштабе времени. Формула изобретения Реверсивный двоичный счетчик с контролем, содержащий основной и вспомогательный регистры, узел переноса, узел заема, причем входы сложения и вычитания счетчика соединены соответственно с первыми входами узла переноса и узла заема, выход которого соединен с первым входом основного регистра, выход основного регистра соединен с информационным входом вспомогательного регистра, выход которого соединен со вторыми входами основного регистра, узла заема и узла переноса, выход узлапереноса соединен с третьим входом основного регистра, первый и второй синхронизационные входы счет чика соединены соответственно с четвертым входом основного регистра, со вторым входом вспомогательного реги стра, отличающийся тем, что, с целью увеличения эффективнос контроля, введены схема сравнения, дешифратор ошибок передачи, дешифра тор ошибок сложения и дешифратор ош бок переноса, причем первый и второ входы дешифратора ошибок переноса соединены соответственно с выходами узла переноса и узла заема, первый и второй входы схемы сравнения соеди нены соответственно с выходами основного и вспомогательного регистро первый, второй и третий выходы схемы сравнения соединены соответственно с первым, вторым и третьим входами дешифратора ошибок сложения, второй и третий выходы схемы сравнения соединены соответственно с первым и вторым входом дешифратора ошибок передачи, первый синхронизационный вход счетчика соединен с третьим входом дешифратора ошибок переноса, выход которого является первым выходом устройства, вход сложения счетчика соединен с первыми управляющими входами дешифратора ошибок перенос; а и дешифратора ошибок сложения, вход вычитания счетчика соединен со вторыми управляющими входами дешифратора ошибок переноса и дешифратора ошибок сложения, вход вычитания счетчика соединен со вторыми управляющими входами дешифратора ошибок переноса и дешифратора ошибок сложения, тактовый вход счетчика соединен с третьим управляющим входом дешифратора ошибок сложения, третий и четвертый синхронизационные входы счетчика соединены соответственно с первыми синхронизационными входами дешифратора ошибок сложения и дешифратора ошибок передач, выходы дешифратора ошибок сложения и дешифратора ошибок передачявляются соответственно вторым и третьим выходом счетчика. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 154095, кл. G 06 F,-1 9 . 04 . 62 . 2.Майоров С.А. и Новиков Г.И. Структура цифровых вычислительных машин. М., 1979, с. 79-87 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1982 |

|

SU1024988A1 |

| Устройство для сложения в двоичной и в двоично-десятичной системе счисления | 1985 |

|

SU1273919A1 |

| Реверсивный счетчик | 1980 |

|

SU879780A2 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Устройство для определения логарифмического коэффициента ошибок дискретного канала связи | 1986 |

|

SU1411993A1 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Двоичный счетчик с контролем ошибок | 1972 |

|

SU448469A1 |

| Устройство символьной синхронизации | 1990 |

|

SU1775869A1 |

| Комбинационный двоичный сумматор-вы-чиТАТЕль | 1979 |

|

SU824205A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-19—Подача