(54) КОМБИНАЦИОННЫЙ ДВОИЧНЫЙ СУММАТОР-ВЫЧИТATБЛЬ

чен к выходу результата сумматора-вычитателя, первые дополнительные выходы ; первого и второго .узлов неравнозначности подключены к первому и второму входам узла формирования заема, выход которого подключен к выходу эаема сумматора-вычитателя, вторые дополнительные выходы первого и второго узлов неравнозначности подключены к первому и второму входам узла формирования переноса, выход которого подключен к выходу переноса сумматора-вычитателя , содержит дополнительно элемент И-НЕ, первый управляющий вход первого узла неравнозначности . соединен с первым управляющим входом сумматора-вычитателя, а второй управляющий вход первого узла неравнозначности - с выходом элемента И-НЕ входы которого подключены к второму дополнительному выходу узла неравнозначности и второму управляющему входу сумматора-вычитателя, третий и четвертый управляющие входы которого подключены к управляющим входам узлов формирования заема и Формирования переноса соответственно, основной, первый дополнительный и второй дополнительный выходы первого узла неравнозначности соединены соответственно с первЕом, вторым и третьим дополнительными выходами сумматора-вычитателя, при этом узлы формирования заема и переноса выполнены на одном элементе И-НЕ каждый, а узлы неоднозначностина четырех элементах И-НЕ ка;кдый, причем в каждом из узлов неравнозначности первый и второй входы первого элемента И-НЕ соединены с первым и вторым входами узла неравнозначности соответственно, выход первого элемента И-НЕ соединен с первыми входами второго и третьего элементов И-НБ выходы которых подключены соответственно к первому и второму входам четвертого элемента Й-НЕ, выход которого соединен с основным выходом узла неравнозначности, первый и второй входы которого соединены с вторыми входами второго и третьего элемен- тов И-НЕ соответственно, первый и втО рой управляющие входы первого узла неравнозначности подк} К)чены к третьим входам первого и четвертого элементов И-НЕ этого узла соответственно, первый и второй дополнительиые выходы первого узла неравнозначности соединены с выходами соответственно третьего и первого элементов И-НЕ этого узла, третьи входы первого и . второго элементов И-НЕ второго узла неравнозначности соединены с третьим входом этого узла первый и второй дополнительные выходы которого соединены с выходами соответственно.второго и первого элементов И-НЕ этого узла.

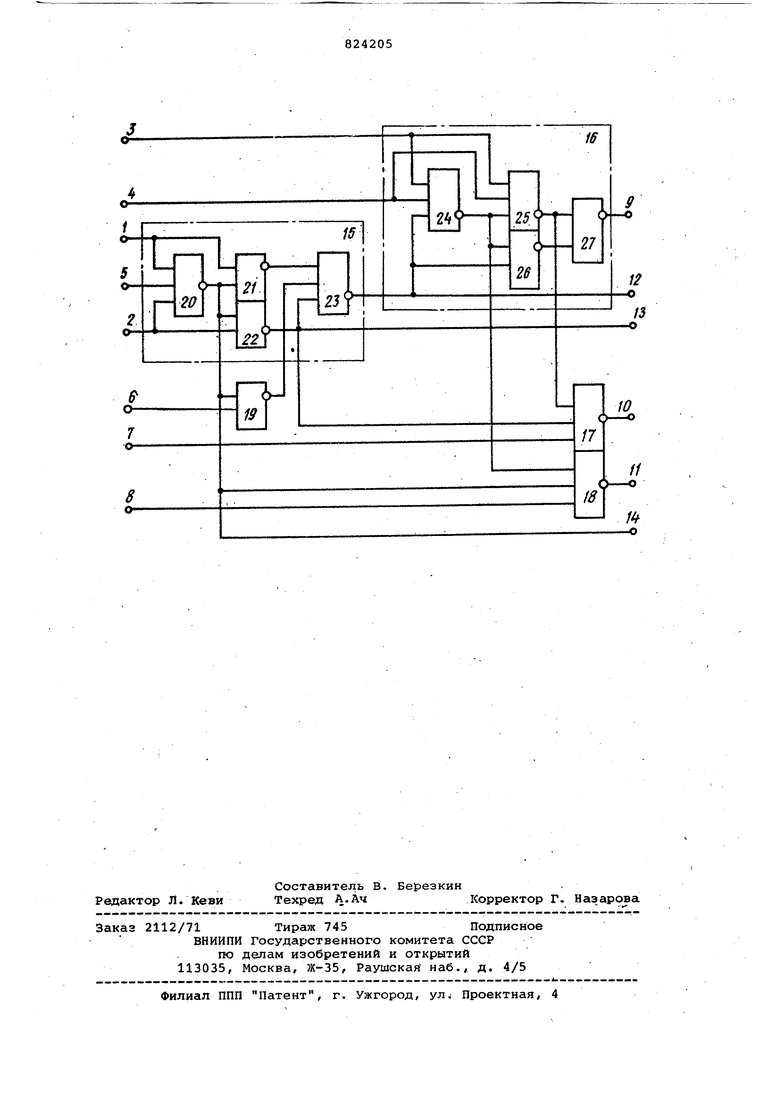

На чертеже приведена функциональная схема сумматора-вычитателя.

Сум атор-Вогчитатель содержит вход. 1 первого операнда (слагаемого при сложении, уменьшаемого при вычитании, перво-го слова при выполнении логической операции), вход 2 второго операнда (для приема второго слагаемого при сложении, вычитаемого при вычитании, второго слова при выполнении логичес|кой операции), вход 3 переноса из младшего разряда при сложении, вход 4 заема из млададего разряда при вычитании, управляющие входы 5-8 для переключения вида операции, выполняемой сумматором-вычитателем, выход 9 результата для выдачи результата выполненной операции, выход 10 заема для выдачи заема в старший разряд при вычитании, выход 11 переноса для выдачи переноса в старший разряд при сложении, дополнительные выходы 1214 для выдачи данных, необходимых при формировании ускоренных переноса (выходы 12 и 14) и заема (выходы 12 и. 13) . Су1иматор-вычитатель содержит узел is неравнозначности для получения частичной суммы при сложении (вычитании) входных чисел, узел 16 неравнозначности для получения суммы (разности) при сложении (вычитании), эти же узлы используются для выполнения логических операций, узел формирования заема на элементе И-НЕ 17 для формирования заема в старший разряд при вычитании, узел формирования переноса на элементе И-НЕ 18 для формирования переноса в старший разряд при сложении, элемент И-НЕ 19 для переключения выполняемой в устройстве операции. Узел 15 состоит из четырех элементов И-НЕ 20-23, узел 16 состоит из четырёх элементов И-НЕ 24-27.

При выполнении операции на входы 1 и 2 подаются соответствующие разряды чисел (слов), над которыми производится арифметическая или логическая операция, на входы 3 и 4 подаются перенос и заем из младшего разряда сумматора-вычитателя при сложении и вычитании.

Описание сумматора-вычитателя в действии приведено в виде формул, эквивалентных выполняемым функциям элементов сумматора-вычитателя. Элементы И-НЕ, которые входят в сумматор, описываются следующей формулой

XjX, (1) где у - значение сигнала на выходе

элемент а

X,,- - равно О или 1, при этом О обозначает низкий уровень напряжения, 1 - высокий уровень напряжения.

0 Для двухвходовых элементов следует положить Хд 1. в формуле выполняются обычные арифметические операции; вычитание и умножение, еЬли входные величиндл сами являются функциями дру.щх входных величин, то после подставки их значений формула принимае вид многочлена, в котором добавляет операция сложения. Обозначим значение величин на вх де сумматора-вычитателя через х с и дексом, равным номеру входа. Значен величины на выходе сумматора-вычита ля обозначим через У с индексом, ра ным номеру выхода. Обозначим значе ние величины на выходе элемента чер iv с индексом, равным номеру элемент Тогда функционирование сумматора и его элементов описывается формулгиши 2-18 Уго АЛ . -Af 22- IV J К -Уг Уа- Угв Vas V 4 УМ. 26 УМ yi4 . i Уйб УЛ f- тУгзУйБ - 8У2оУй4 У9 У27 , , И М8 Уа., У У12, У14 У20Подставив соответствующие значения в формулы для у, , у , у . У« /

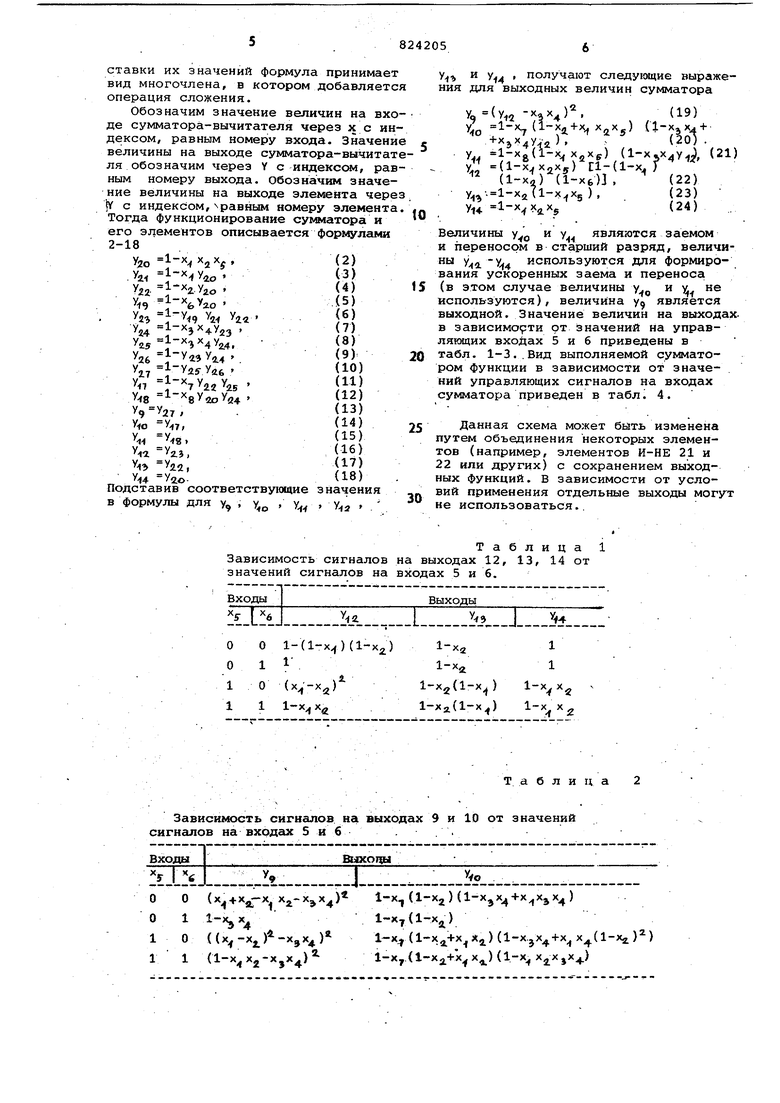

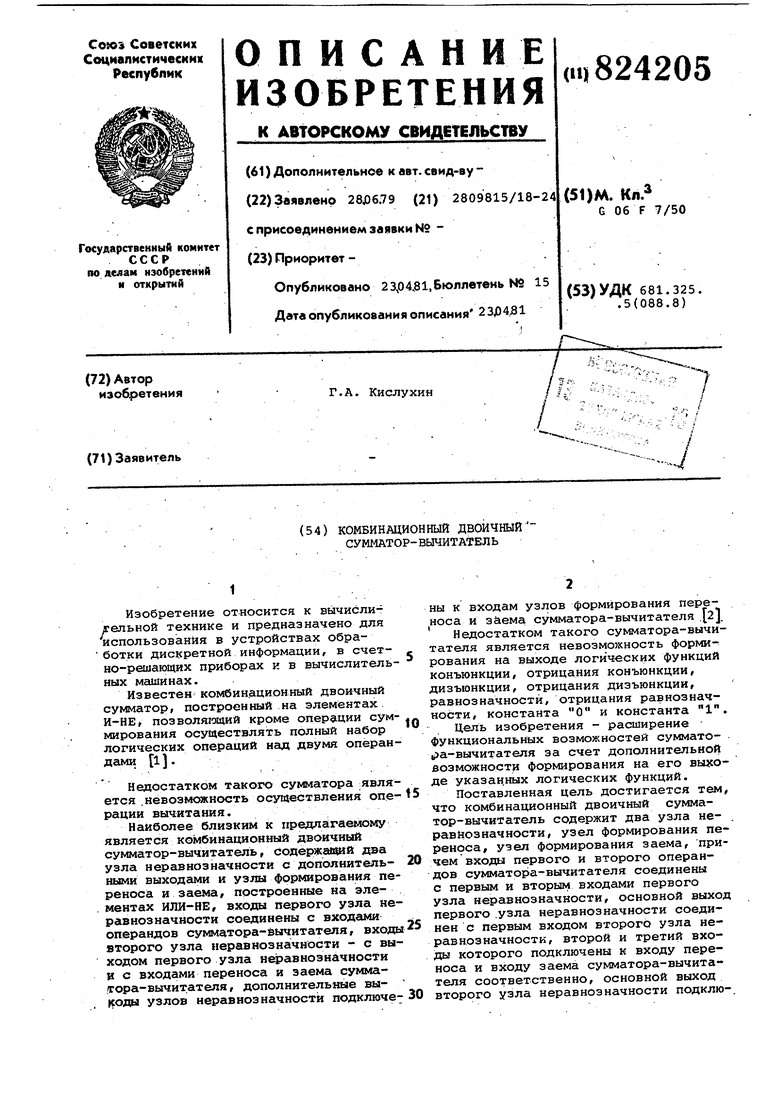

Зависимость сигналов на выходах 12, 13, 14 от значений сигналов на входах 5 и 6.

Таблица 1 У-j У14 получают следующие выражения для выходных величин сумматора Уо (У12 S 4+ (.+ -bxjx y.-g ) ,,(20) . УЯ 21) У„ () Cl-d-x.) (1-х1) (1-Хб).(22) у,,-.1-Х2( ) ,(23) У14 l-.(24). Величины у и у являются заемом и переносом в старший разряд, величины используются для формирования ускоренных заема и переноса (в этом случае величины у и у. не используются), величина у является выходной. Значение величин на выходахв зависимости от значений на управляющих входах 5 и 6 приведены в табл. 1-3..Вид выполняемой сумматором функции в зависимости от значений управляющих сигналов на входах сумматора приведен в табл. 4. Данная схема может бать изменена путем объединения некоторых элементов (например, элементов И-НЕ 21 и 22 или других) с сохранением выходных функций. В зависимости от условий применения отдельные выходы не использоваться..

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| Сумматор-вычитатель | 1981 |

|

SU993254A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Сумматор-вычитатель | 1988 |

|

SU1536373A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Устройство для сложения и вычитания | 1984 |

|

SU1193664A1 |

Зависимость сигналов на выходах 9 и 10 от значений сигналов на входах 5 и б . . .

Выходы

Входы

Т а б л и ц а

7824205

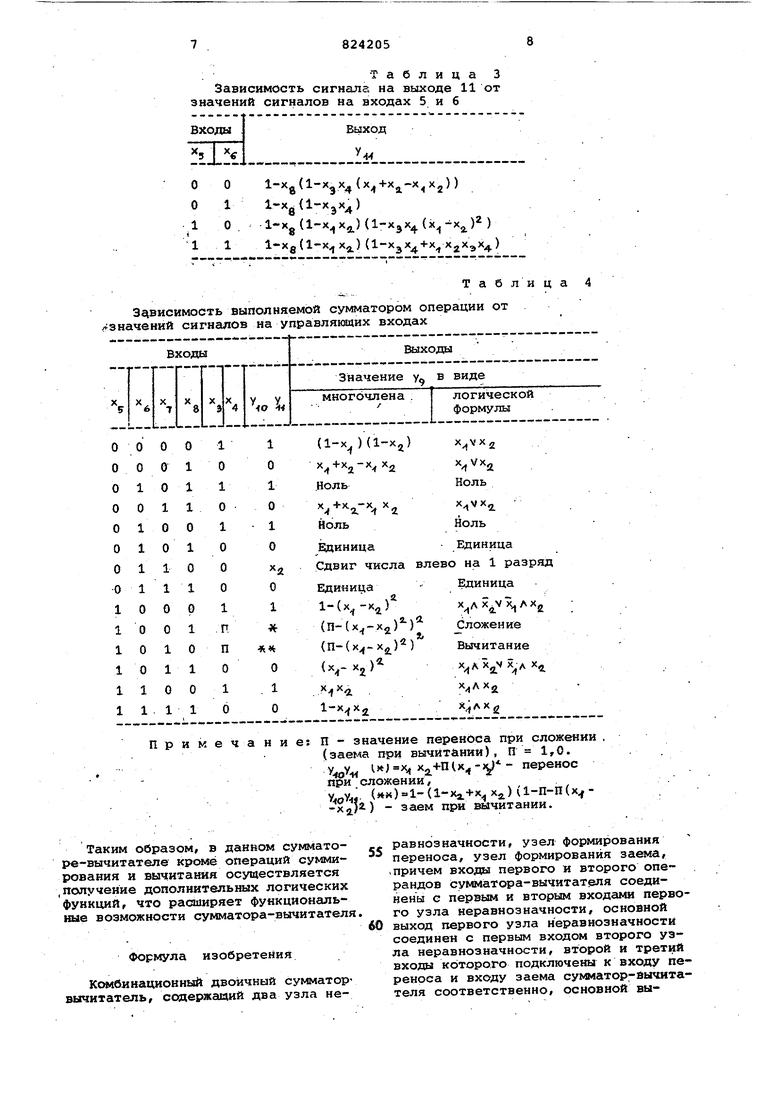

Зависимость сигнала на выходе 11 от значений сигналов на входах 5 и 6

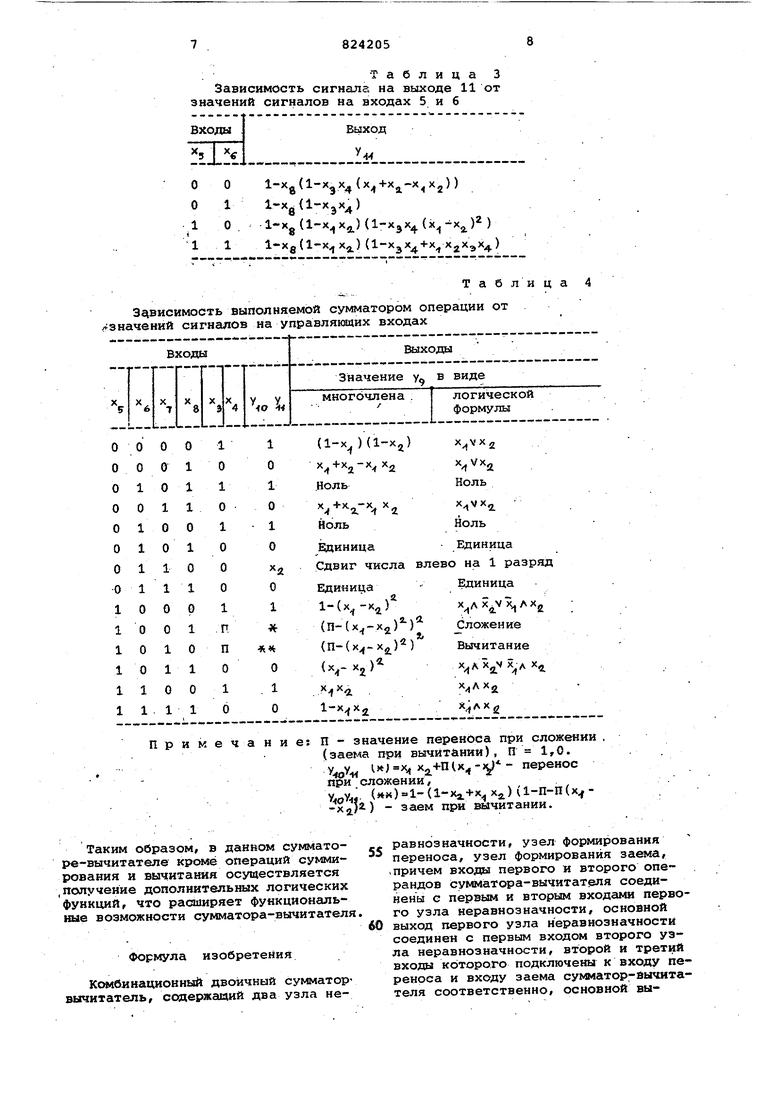

Зависимость выполняемой сумматором операции от значений сигналов на управляющих входах

р и м е ч а вне: П - значение переноса при сложении

(заема при вычитании), П 1,0. Хд ч-ПСх ч - перенос при сложении,

У« ()l-(.) (х -xjji) - заем при шачитании.

Таким образом, в данном cyi iaTOре-вычитателе крсхмё операций суммирования и вычитания осуществляется .получение дополнительных логических функций, что расширяет функциональные возможности сумматора-вычитателя.

Формула изобретения

Комбинационный двоичный сумматорвычитатель, содержащий два узла неТаблицаЗ

Таблица 4

равнозначности, узел формирования переноса, узел формирования заема, .причем входы первого и второго операндов сумматора-вычитателя соединены с первым и вторым входами первого узла неравнозначности, основной выход первого узла неравнозначности соединен с первым входом второго узла неравнозначности, второй и третий входы которого подключены к входу переноса и входу заема сумматор вычитателя соответственно, основной вы--СОД второго узла неравнозначности подключен к выходу результата сумматора-вычитателя, первые дополнительные выходы первого и второго узлов неравнозначности подключены к первому и второму входам узла формирования заема, выход которого подключен к выходу заема сумматора-вычитателя, вторые дополнительные выходы первого и второго узлов неравнозначности подклю ,чены к первому и второму входам узла формирования переноса, выход которого подключен к выходу переноса сумматора-вычитателя, отличаю щий с я тем, что, с целью расширения функциональных возможностей за счет выполнения дополнительных логических функций, конъюнкции, отрицания конъюнкции, дизъюнкции, отрицания дизъюн| ции, равнозначности, отрицания равнозначности, константа О и константа 1, сумматор-вычитйтель содержит дополнительно элемент И-НЕ, первый управляющий вход первого узла неравнозначности соединен с первым управляющим входом сумматора-вычитателя, а второй управляющий вход первого узла неравнозначности - с выходом элемента И-НЕ, входы которого подключены к второму дополнительному выходу узла неравнозначности и второму управляющему входу сумматоравычитателя, третий и четвертый управляющие входы которого подключены к управляющим входам узлов формирования заема и формирования переноса соответственно, основной, первый дополнительный и второй дополнительный выходы первого узла неравнозначности соединены соответственно с первым, вторым и третьим дополнительными выходами сумматора-вычитателя, при этом

узлы формирования заема и переноса выполнены на одном элементе И-НЕ каждый, а узлы неоднозначности - на четырех элементах и-НЕ каждый, причем в каждом из узлов неравнозначности первый и второй входы первого элемента И-НЕ соединены, с первь|м и вторым входами узла неравнозначности соответственно, выход первого элемейта И-НЕ соединен с первыми входами второго и третьего элементов И-НЕ,

0 выходы которых подключены соответственно к первому и второму входам , четверто-го элемента И-НЕ, выход которого соединен .с основным выходом узла неравнозначности, первый и вто5рой входы которого соединены с вторыми входами второго и третьего элементов И-НЕ соответственно, первый и второй управляющие входы первого узла неравнозначности подключены к

0 третьим входам первого и четвертого элементов И-НЕ этого узла соответственно, первый и второй дополнительные выходы первого узла неравнозначности соединены с выходами соответственно третьего и первого эле5ментов И-НЕ этого узла, третьи входы первого и второго элементов И-НЕ второго узла неравнозначности.соединены с третьим входом этого узла, первый и второй дополнительные выхо0 . ды которого.соединены с выходами соответственно второго и первого элементов И-НЕ этого узла.

Источники информации, принятые во внимание при экспертизе

5

(прототип).

Авторы

Даты

1981-04-23—Публикация

1979-06-28—Подача