I

Изобретение относится к вьгаислительной технике, автоматике и телемеханике и может быть использовано в качестве самостоятельного устройства или в составе аппаратуры для .решения специальных задач.

Известно устройство, содержащее запоминающее устройство, блок двоичных умножителей, счетчик, два счетчика интервалов, вычитающее устройство, двоичный умножитель, схему ИЛИ, счетчик резуль- тата ij.

Недостатком устройства является невоаможность воспроизведения пространственных кривых, принадлежащих поверхности (к,V), траектория движения которых в плоскости ХОУ задается потоками единичных приращений ДУч и ду.

Из известных устройств наиболее близким к изобретению по технической сущности является устройство, содержащее блок памяти и счетчик; приращений по /, линейный преобразователь, блок формированш/ знака приращения и линию задержки 2J,

Недостатком устройства является формирование приращений только одномерных функций, т.е. плоских кривых. Воспроизведение пространственных кривых с помошью данного ФП также невозможно.

Цель изобретения - расширение функциональных возможностей за счет воспроизведения пространственных кривьи.

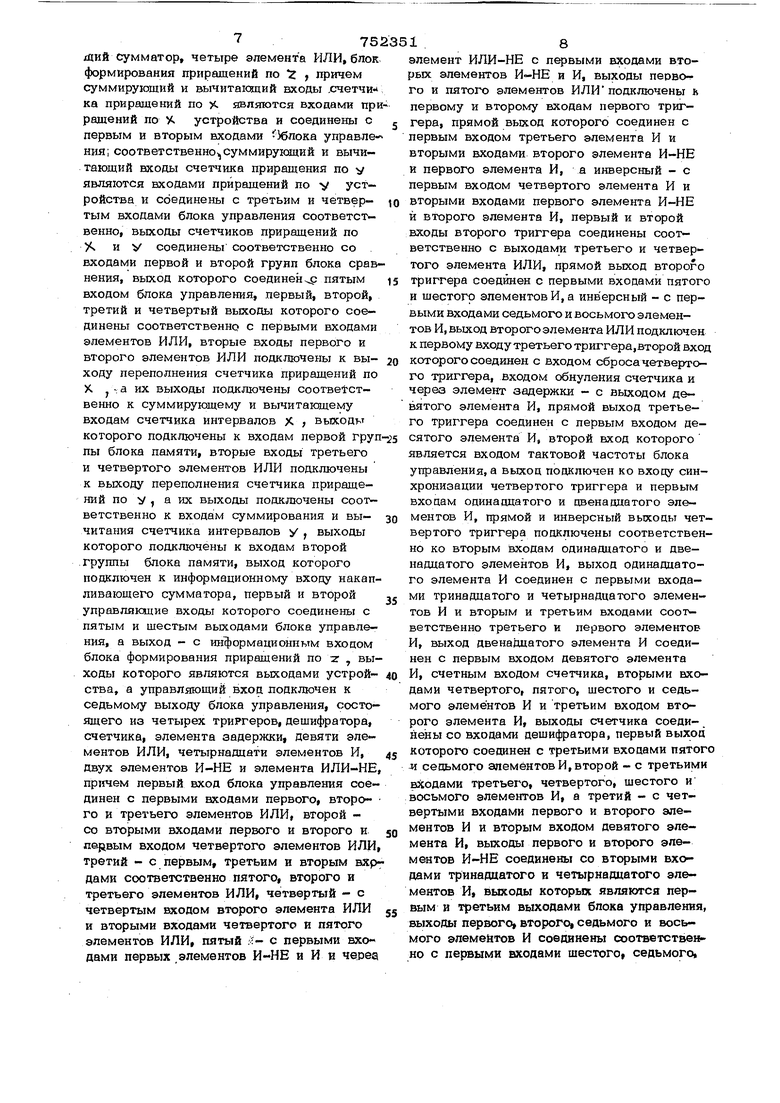

Указанная цель достигается тем, что в устройство, содержащее блок памяти и счетчик приращений по у., дополнительно введены счетчик тфиращений по v счетчики интервалов у, и V, блок сравнения, блок управления, накапливающий сумматор, четыре элемента ИЛИ, блок формирования пр1фа1аеш}й по 2 j причем суммирующий и вычитаюший входы счетчика приращений по являются входами приращений по К устройства н соединены с первым и вторым вхопами блока управления соответственно суммирующий и вычитающий входы счетчика приращения по являются входами приращений по D устройства и соединены с третьим и четвертым входами 75 блока управления соответственно, выходы счетчиков приращений по X и V соединены соответственно со входами первой и второй групп блока сравнения, выход которого соединен с пятым входом блока уп равления, первый, второй, третий и четвертый выходы которого соединены соответственно с первыми входами элементов ИЛИ, вторые входы первого и второго элементов ИЛИ подключены к выходу переполнения счег ика приращений по X , а их выходы подключены соответственно к суммирующему и вычитаквдему Ьходам счетчика интервалов выходы которого подключены к входам первой группы блока памяти, вторые входы третьего и четвертого элементов ИЛИ подключены к выходу переполнения счетчика приращений по у , а их выходы подключены соответственно ко входам суммирования и вычитания счетчика интервалов V , выходы которого подключены к входам второй группы блока памяти, выход которого подключен к информационному входу накапливающего сумматора, первый и второй управляющие входы которого соединены с пятым и шестым выходами блока управления, а выход - с информационным входом блока формирования приращений по 2 .выходы которого являются выходами устройства, а управлякяций вход подключен к седьмому выходу блока управления, состоящего из четырех триггеров, дешифратора, счетчика, элемента задержки, девяти элементов ИЛИ, четырнадцати элементов И, двух элементов И-НЕ и элемента ИЛИ-НЕ, причем первый вход блока управления соединен с первыми входами первого, второго и третьего элементов ИЛИ второй - со вторыми входами первого и второго и первым входом четвертого элементов ИЛИ, третий - с первым, третьим и вторым входами соответственно пятого, второго и третьего элементов ИЛИ, четвертый - с четвертым входом второго эле мента ИЛИ и вторыми входами четвертого и пятого элемента ИЛИ, пятый - с первыми входами первых элементов И-НЕ и Ии через элемент ИЛИ-НЕ с первыми входами вторых элементов И-НЕ и И, выходы первого и пятого элементов ИЛИ подключены к первому к второму входам первого триггера, прямой выход которого соединен с первым входом Третьего элемента И и вторыми входами второго элемента И-НЕ и первого элемента И, а инверсный - с первым входом четвертого элемента И и вторыми входами первого элемента И-НЕ и второго элемента И, первый и второй входы второго триггера соединены соответствен1но с выходами третьего и четвертого элементов ИЛИ, прямой выход второго триггера соединен с первыми входами пятого и шее того элементов И, а инверсный -спер- лыми входами седьмого и восьмого элеменгов И, выход второго элемента ИЛИ подключен к первому входу третьего триггера, второй вход которого соединен с входом сброса четвертого триггера, входом обнуления счетчика и через элемент задержки - с выходом девятого элемента И, прямой выход третьего триггера соединен с первым входом десятого элемента И, второй вход которого является входом тактовой частоты блока управления, а выход подключен ко входу синхронизации четвертого триггера и первым входам одинадцатого и двенадцатого элементов И, прямой и инверсный выходы четвертого триггера подключены соответственно ко вторым входам одинадцатого и двенадцатого элементов И, выход одинадцатого элемента И соединен с первыми входами тринадцатого и четырнадцатого элементов И и вторым и третьим входами соответствен- ко т ретьего и первого элементов И, выход двенадцатого элемента И соединен с первым входом девятого элемента И, счетным входом счетчика, вторыми входами четвертого, пятого, шестого и седьмого элементов И и третьим входом второго элемента И, выходы счетчика соединены со входами дешифратора, первый выход которого соединен с третьими входами-пятого и седьмого элементов И, второй - с третьими входами третьего, четвертого, шестого и восьмого элементов И, а третий - с четвертыми входами первого и второго элементов И и вторым входом девятого элемента И, выходы первого и второго элементов И-НЕ соединены со вторыми входами тринадцатого и четырнадцатого элементов И, выходы которых являются первым и третьим входами блока управления, выходы первого, второго, седьмого и восьмого элементов И соединены соответственно с первыми входами шестого, седьмого, восьмого и девятого элементов ИЛИ, вторые входы которых соединены с выходами соответственно четвертого, третьего, шестого и пятого элементов И, а выходы являются соответственно четвертым, вторым, шестым и Пятым выходами блока управления, седьмым выходом которого является выход девятого элемента И. На фиг. I представлена блок-схема устройства; на фиг. 2 - блок-схема блока управления. 575 Устройство содержит счетчики 1 и 2 приращений по X и у , счетчики 3 и 4 интервалов у. ну, блок 5 сравнения, элементы 6 ИЛИ, блок 7 управления, блок 8 памяти, накапливающий сумматор 9 и блок 10 формирования приращения. Блок управления содержит триггеры 11-14, дешифратор 15, счетчик 16, элемент 17 задержки, элементы 18-26 ИЛИ, элементы 27-40 И, элементы 41 и 42 И-НЕ, элементы 43 ИЛИ-НЕ. Преобразователь предназначен для воспроизведения функции 2 1(х.,У, котора вместе со своими аргументами X и У представлена в виде потоков единичных приращений (1 Д ,t X, . У ).ЦФП реализован на основе кусочно-плоскостной ин- терпол5щии поверхности : ( / У ) Зависимости для определения величины ЛТ по прирашениям д ). и ЛУ, т.е. л7(ДК и Л Z (AV) на IJ -ом квадрате разбиения . --Z- - X /(ду)--(т;,,-,,-.,,д)-.У, (,(.) ,--.,,, SJM :г:(ду),(г,. ,,j,,-Zi. УДУ (K-X;)(y-V-) Выражения (1) и (2) положены в основу построения преобразователя. Значения аргументов х и у фиксируются в соответствующих реверсивных счет чиках 13и24 Коды счетчиков3 и 4 интервалов подключены к адресной шине блока памяти, предназначенного для хранения кодов ординат функции в узлах и определяют адрес ячейки памяти в которой хранится код, со ответствующий ординате 7.1 . Коды счетчиков 1 и 2 приращений соответствуют величинам( и (VVj)H поступают на блок 5 сравнения, выходной сигнал котог О,если (/ - )t . (V- vp и ,ecAVA()) С приходом единичного приращения по f(t) i) или V (i ) запускается блок 7 управления, работа которого осуществляется в соответствии с микропро-55 граммой. В первом такте с помощью управляющих сигналов блока 7 управления обеспечивается увеличение содержимого счетчи16ков 3 и 4 интервалов на единицу, что Позволяет выбрать из блока 8 памяти код ординаты а:- 141 и суммировать его во втором полутакте с содержимым накапливакщего сумматора 9. Во втором такте содержимое счетчика 3 уменьшается на 1, что позволяет во втором полутакте осуществить передачу в сумматор 9 обратного кода ординаты7; т.е. осуществить операцию вычитания. В результате вьтолнения двух тактов к содержимому сумматора 9 прибавляется разность (i,j+ -z.jjj ) т.е. приращение функции, соответствующее единичному приращению аргумента X В третьем такте обеспечивается установка счетчиков 3 и 4 в исходное состояние и в случае возникновения переполненкя в сумматоре фop Лиpyeтcя соответствующее единичное приращение функции AZ . этого блок 7 управления вырабатывает сигнал опроса блока 1О формирования приращения - формирование д2 . Остаток в сумматоре 9 учитывается при выработ ке следующего единичного приращения д7, которое может быть сформировано при поступлении AZ или ДУ . После выполнения трех тактов блок 7 управления устанавливается в исходное состояние. Погрешность воспроизведения $ (х, у), основном, определяется видом самой « объемом памяти, т.е. количест ом разбиений по осям аргументов X и V,H может быть сведена к величинам порядка 0,1-0,01%. По сравнению с известным устройством в предлагаемом суЩ ственно расширены функциональные возможности. Предлагаемое изобретение может найти применение при построении различного рода автоматизированных систем управления и контроля, в цифровых интегриРУкэших машинах и других специализирован« вычислительных устройствах. Формула изобретения Цифровой функциональный преобразователь, содержащий блок памяти и счетчик приращений по )С,,отличающийс я тем, что, с целью расширения функциональных возможностей за счет воспронаведения пространственных кривых, преобразователь содержит счетчик приращений по у, счетчики интервалов k и У, блок сравнения, блок управления, накапливаюдни сумматор, четыре элемента ИЛИ, блок формирования приращений по , причем суммирующий и вычитакяций входы .счетчи- ка приращений по X. являются входами пр ращений по УЧ устройства и соединены с первым и вторым входами JenoKa управле ния; соответственно суммирующий и вычитающий входы счетчика приращения по v являются входами приращений по v уст ройства и соединены с третьим и четвертым входами блока управления соответственно, выходы счетчиков приращений по X и у соединены соответственно со входами первой и второй групп блока срав нения, выход которого соединен пятым входом блока управления, первый, второй, третий и четвертый выходы которого соединены соответственно с первыми входами элементов ИЛИ, вторые входы первого и второго элементов ИЛИ подключены к выходу переполнения счетчика приращений по их выходы подключены соотве ственно к суммирующему и вычитающему входам счетчика интервалов X , выходы которого подключены к входам первой груп пы блока памяти, вторые входы третьего и четвертого элементов ИЛИ подключены к выходу переполнения счетчика приращений по V , а их выходы подключены соответственно к входам суммирования и вычитания счетчика интервалов у, выходы которого подключены к входам второй группы блока памяти, выход которого подключен к информационному входу накап ливающего сумматора, первый и второй управляющие входы которого соединены с пятым и шестым выходами блока управления, а выход - с информационным входом блока формирования приращений по -z , выходы которого являются выходами устройства, а управляющий вход подключен к седьмому выходу блока управления, состоящего из четырех триргеров, дещифратора, счетчика, элемента задержки, девяти эле ментов ИЛИ, четырнадцати элементов И, двух элементов И-НЕ и элемента ИЛИ-НЕ причем первый вход блока управления соединен с первыми входами первого, второго и третьего элементов ИЛИ, второй со вторыми входами первого и второго и первым входом четвертого элементов ИЛИ третий - с первым, третьим и вторым вхр дами соответственно пятого, второго и третьего элементов ИЛИ, четвертый - с четвертым входом второго элемента ИЛИ и вторыми входами четвертого и пятого элементов ИЛИ, пятый .- с первыми входами первых элементов И-НЕ и И и череа элемент ИЛИ-НЕ с пфвыми входами вторых элементов и И, выходы перво- Го и пятого элементов ИЛИ подключены к первому и второму входам первого триггера, прямой выход которого соединен с первым входом третьего элемента И и вторыми входами второго элемента И-НЕ и первого элемента И, а инверсный - с первым входом четвертого элемента И и вторыми входами первого элемента И-НЕ и второго элемента И, первый и второй входы второго триггера соединены соответственно с выходами третьего и четвертого элемента ИЛИ, прямой выход второго триггера соединен с первыми входами пятого и шестого элементов И, а инверсный - с первыми входами седьмого и восьмого элементов И.выход второгоэлемента ИЛИ подключен к первому входу третьего триггера,второй вход которого соединен с входом сброса четвертого триггера, входом обнуления счетчика и через элемент задержки - с выходом девятого элемента И, прямой выход третьего триггера соединен с первым входом десятого элемента И, второй вход которого является входом тактовой частоты блока управления, а выход подключен ко входу синхронизации четвертого триггера и первым входам одинадцатого и двенадцатого элементов И, прямой и инверсный вьжоды четвертого триггера подключены соответственно ко вторым входам одинадцатого и двенадцатого элементов И, выход одинадцатого элемента И соединен с первыми входами тринадцатого и четырнадцатого элементов И и вторым и третьим входами соот ветственно третьего и первого элементов И, выход двенадцатого элемента И соединен с первым входом девятого элемента И, счетным входом счетчика, вторыми входами четвертого, пятого, шестого и седьмого элементов И и третьим входом второго элемента И, выходы счетчика соединены со входами дешифратора, первый выход которого соединен с третьими входами пятого л седьмого эпемёнтов И, второй - с третьими входами третьего, четвертого, шестого и восьмого элементов И, а третий - с четвертыми входами первого и второго элементов И и вторым входом девятого элемента И, выходы первого и второго элементов И-НЕ соединены со вторыми входами тринадцатого и четырнадцатого элементов И, выходы которьк являются первым и третьим выходами блока управления, выходы первогс второгО| седьмого и восьмого элемейтов И соединены соответственно с первыми входами шестого, седьмого. 975 восьмого н девятого элементов ИЛИ, вто. рые входы которых соединены с выходами соответственно четвертого, третьего, шестого и пятого элементов И, а выходы являются Соответственночетвертым, вторым, шестым и пятым выходами блока управления, седьмым вьтходом которого является выход девятого элемента И. 1 Источники информации, принятые во внимание при экспертиз.. 1.Авторское свидетельство СССР № 52157О, кл. q Об F 15/34, 1976. 2,Авторское свидетельство СССР N 368618 кл. G 06 F 7/26, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране электронно-лучевой трубки | 1982 |

|

SU1053139A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Система оптимизации управления непосредственно и косвенно управляемыми объектами | 1982 |

|

SU1080117A1 |

| Арифметическое устройство | 1981 |

|

SU1012240A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU883897A1 |

| Устройство для формирования информации на телевизионном индикаторе | 1981 |

|

SU1075298A1 |

| Интерполятор поверхности | 1980 |

|

SU942040A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для вычисления полинома | 1980 |

|

SU885997A1 |

+ЛХ -АИ

I

+ лу

/Л2

р« -Ai

-fO

фыг-/

Авторы

Даты

1980-07-30—Публикация

1978-07-24—Подача