1

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля памяти, использующее ЦВМ для задания последовательности выбираемых адресов, видов операций, хранения и обработки результатов l .

Недостатком этого устройства является невысокое быстродействие при контроле блоков памяти с малым временем обращения.

Наиболее близким техническим решением к предлагаемому является устройство для контроля памяти, содер-, жащее формирователь тестовых сигналов, формирователь сигналов записи и считывания, блок останова, схему сравнения, регистр числа, блок управления, триггер, первый и второй рЛИстры адреса, блок местного управления и коммутатор, причем входы регистров адреса подключены соответственно к первому и второму выходам блока управления, а выходы - к одним из входов коммутатора, вход формирователя тестовых сигналов соединен -с третьим выходом блока управления, а выходы соединены соответственно с одним из входов регистра числа и первыми входами схемы сравнения

и формирователя сигналов записи и считывания, вторые входы которых подключены соответственно к выходу регистра числа и первому выходу блока местного управления, второй выход и вход которого подключены соответственно ко входу блока управления и выходу блока останова, вход которого соединен с выходом схемы сравнения,

10 четвертый выход блока управле ния подключен ко входу триггера 2 .

Однако в этом устройстве не обеспечена возможность производить регенерацию содержимого запоминающих

15 ячеек при контроле динамической памяти .

Цель изобретения - раслирение области применения устройства за счет обеспечения возможности регенерации

20 содержимого запоминающих ячеек при контроле динамической оперативной памяти.

Поставленная цель достигается тем, что устройство содержит третий

25 регистр адреса, элементы И, элемент НЕ и формирователь сигналов регенера ции, входы которого подключены соответственно к третьему выходу блока MecjTHoro управления и пятому вык©

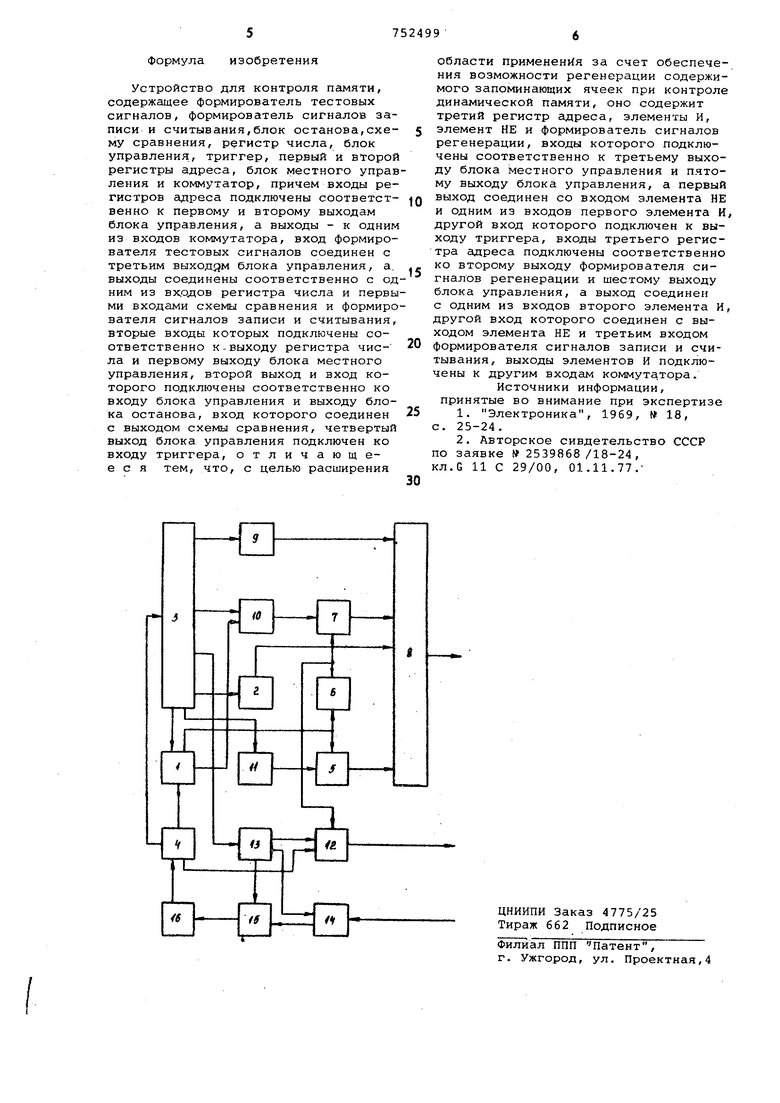

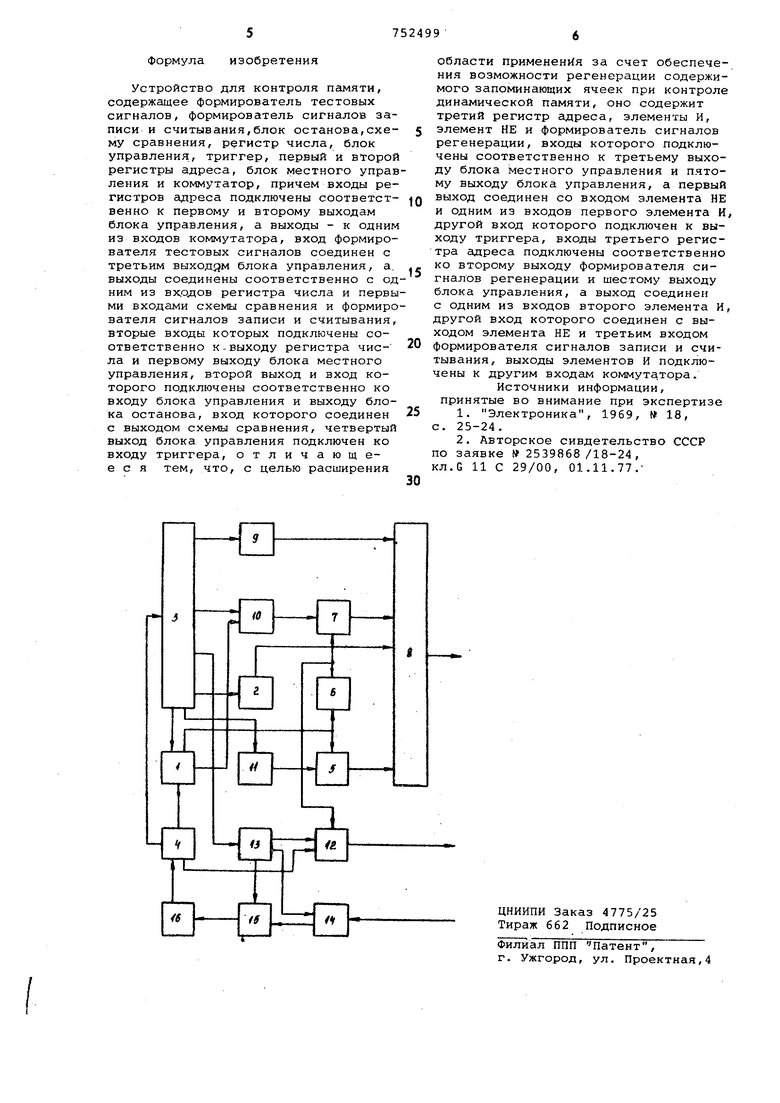

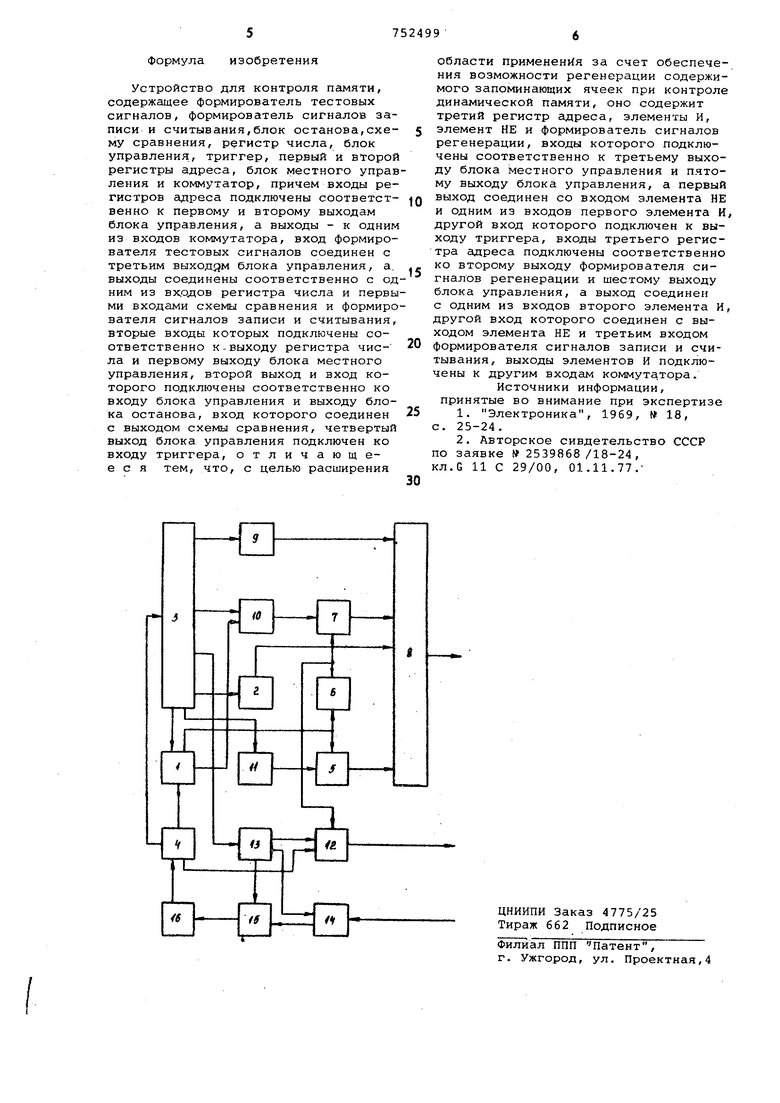

30 ду блока управления, а первый выход соединен со входом элемента НЕ и одним из входов первого элемента И, другой вход которого подключен к выходу триггера,входы третьего регистра адреса подключены соответственно ко второму выходу формирователя сигналсэв регенерации и шестому выходу блока управления, а выход соединен с одним из входов второго элемента И, другой вход которого соединен с выходом элемента НЕ и третьим входом формирователя сигналов записи и считывания, выходы элементов И подключены к другим входам коммутатора. На чертеже изображена структурная схема предлагаемого устройства. Устройство .содержит формирователь 1сигналов регенерации,первый регистр 2адреса, блок 3 управления, блок 4 местного управления, первый элемент 5 И, элемент 6 НЕ, второй элемент 7 И коммутатор 8, второй 9 и третий 10 регистры адреса, триггер 11, формиро ватель 12 сигналов записи и считывания, формирователь 13 тестовых сигна лов, регистр 14 числа, схему 15 срав нения, блок 16 останова. Входы регистров 2 и 9 подключены первому и второму выходам блока 3, а выходы - к одним из входов коммутато ра 8. Вход формирователя 13 соединен с третьим выходом блока 3, а выходы соединены соответственно с одним из входов регистра 14 и первыми входами схемы сравнения 15 и формирователя 12, вторые входы которых подключены соответственно к выходу регистра 14 и первому выходу блока 4, второй выход и вход которого подключены соответственно ко входу блока 3 и выходу блока 16, вход которого соединен с выходом схемы 15 сравнения. Четверты выход блока управления подключен ко входу триггера 11, Входы формировате ля 1 подключены соответственно к тре тьему выходу блока 4 и пятому выходу блока 3, а первый выход, соединен со входом элемента б НЕ и одним из входов элемента 5 И,другой вход которог подключен к выходу триггера 11,Входы регистра10 подключены соответственн ко второму выходу формирователя 1 и шестому выходу блока 3, а выход соединен с одним из входов элемента 7 И другой вход которого соединен с выхо дом элемента 6 НЕ и третьим входом формирователя 12. Выходы элементов 7 и 5, И подключены к другим входам К01у у утатора 8 . Устройство работает следующим об разом. Перед контролем динамического оперативного запоминаюцего устрой ства в формирователе 1 производится установка периода следования тактов регенерации -i где Т - паспортное время хранения данных в динамическом ОЗУ; Р - количество строк или столбцов в матрице памяти, по которым производится регенерация соде.ржимого ячеек. в исходном состоянии регистр 10 адреса устанавливается в нулевое состояние сигналом из блок.а. 3 управления. Переброс состояния регистра 10 производится в каждом такте регенерации сигналом из формирователя 1, который запускается калиброванными сигналами времени из блока 4 местного управления. В начальный момент времени после запуска устройства формирователь 1 выдает разрешающий сигнал на элемент 5 И и элемент 6 НЕ. После инвентирования в элементе 6НЕ этот сигнал закрывает элемент 7И и сигналы адреса с регистра 10 на коммутатор 8 не поступают. Сигналами из блока 3 управления производится перебор состояний регистров 2 и 9, выходные сигналы которых в зависимости от состояния триггера 11 подаются через коммутатор 8 на выход устройства. По истечении времени t формирователь 1 вьщает запрещающий сигнал на элемент 5 И и элемент 6 НЕ. Управляющие сигналы триггера 11 на коммутатор 8 не поступают и оба регистра 2 и 9 отключаются от входа устройства. Запрещающий сигнал из формирователя 1 инвентируется элементом 6 НЕ в разрешающий для элемента 7 И, через который на коммутатор 8 и выход устройства поступает адрес первой строки или столбца. Разрешающий сигнал с выхода элемента б НЕ поступает на блок 12 формирования сигналов записи и чтения и этот блок выдает на выход устройства сигнал чтения, по которому в выбранной строке или столбце проверяемой памяти регенерируется содержимое запоминающих .ячеек. После окончания такта регенерации производится переключение Формирователя 1, после чего он снова выдает разрешающий сигнал на элемент 5 И и элемент б НЕ. Триггер 11 оказывается опять подключенным к коммутатору 8 и подача адреса с регистров 2 и 9 на выход устройства продолжается с прерванного момента. По истечении второго периода t снова происходит подобная смена сигналов на формирователе 1 и следует регенерация содержимого второй строки или столбца, адрес которого соответствует состоянию третьего регистра 10. Использование третьего регистра адреса, элемента НЕ, элементов И и формирователя сигналов регенерации позволяет расширить область прим.енения описанного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1984 |

|

SU1348895A1 |

| Устройство для контроля накопителей | 1982 |

|

SU1048521A1 |

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

| Устройство для отображения информации | 1987 |

|

SU1437909A1 |

| Устройство для отображения информации | 1988 |

|

SU1566404A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-13—Подача