1

Изобретение относится к вычислительной технике и может быть использовано для построения параллельнопоследовательных коммутационных и5 суммирующих устройств в универсальных и специализированных вы 1ислительных системах и структурах высокой производительности.

Наиболее близким техническим ре- Q шением к данному изобретению является электронный искатель-счетчик многоканальный, содержащий ключ,элемент ИЛИ, элемент НЕ, коммутационные блоки, каждый из которых состоит из j элемента И, двух триггеров, трех ключей и элемента задержки I,

Недостатком данного искателя-счетчика многоканального является низкое быстродействие при формировании зна- jQ чений суммы приращений.

Целью изобретения является повышение быстродействия при формировании суммы приращений.

Поставленная цель достигается тем,25 что в электронный искатель-счетчик многоканальный, содержащий ключ, управляющий вход которого соединен с выходом элемнета НЕ, вход которого подключен к первой входной шине уп- JQ

равления, выход ключа соединен с информационной выходной шиной устройства, а сигнальный вход ключа соединен с выходом элемента ИЛИ, входы которого подключены к информационным выходным шинам двух коммутационных блоков, каждый из которых состоит из первого элемента И, первый вход которого соединен с информационной входной шиной и с сигнальным входом первого ключа, второй вход первого элемента И соединен с первой входной шиноа управления, третий вход - с информационной выходной шиной устройства, а выход первого элемента И - с единичным входом первого триггера, нулевой вход которого соединен со второй входной шиной управления, прямой выход первого триггера соединен с управляющим входом первого ключа, выход которого соединен с единичным входом второго триггера, нулевой вход которого подключен к выходу элемента задержки, прямой выход второго триггера подключен к управляющему входу второго ключа, выход которого соединен с информационной выходной шиной коммутационного блока, инверсный выкод второго триггера подключен к управляющему входу третьего ключа, сигнальные входы второго и третьего ключей первого коммутационного блока соединены с третьей входной шиной управления, а второго - с выходом третьего ключа первого коммутационного блока; четвертую, пятую и шестую шины управления, в кажддай из коммутационных блоков дополнительно четыре элемента И и два элемента ИЛИ, причем входы первого элемента ИЛИ соединены с выходом второго ключа и выходами второго и третьего элементов И, выход первого элемента ИЛИ первого коммутационного блока соединен с первыми входами второго и четвертого элементов 4 второго коммутационного блока, выход первого элемента ИЛИ второго коммутационного блока соединен с первой выходной шиной управления, второй вход второго элемента И подключен к инверсному выходу второго триггера и к первому входу пятого элемента И, третий вход второго-элемента И - к первому входу третьего элемента И и к четвертой -входной шине управления, выход первого элемента ИЛИ соединен с входом элемента задержки, -второй, вход третьего элемента И подключен к прямому выходу второго триггера и к второму входу четвертого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу пятого элемента И, выход второго элемента ИЛИ первого коммутационного блока подключен ко второму входу пятого элемента И и к третьему входу третьего элемента И второго коммутационного блока, выход второго элемента ИЛИ второго коммутационного блока подключен ко второй выходной шине управления, первые входы второго и . четвертого элементов И первого коммутационного блока подключены к пятой входной шине управления, второй вход пятого элемента И и третий вход третьего элемента И первого коммутационного блока подключены к шестой входной шине управления, выход третьего ключа второго коммутационного блока подключен к третьей выходной шине управления.

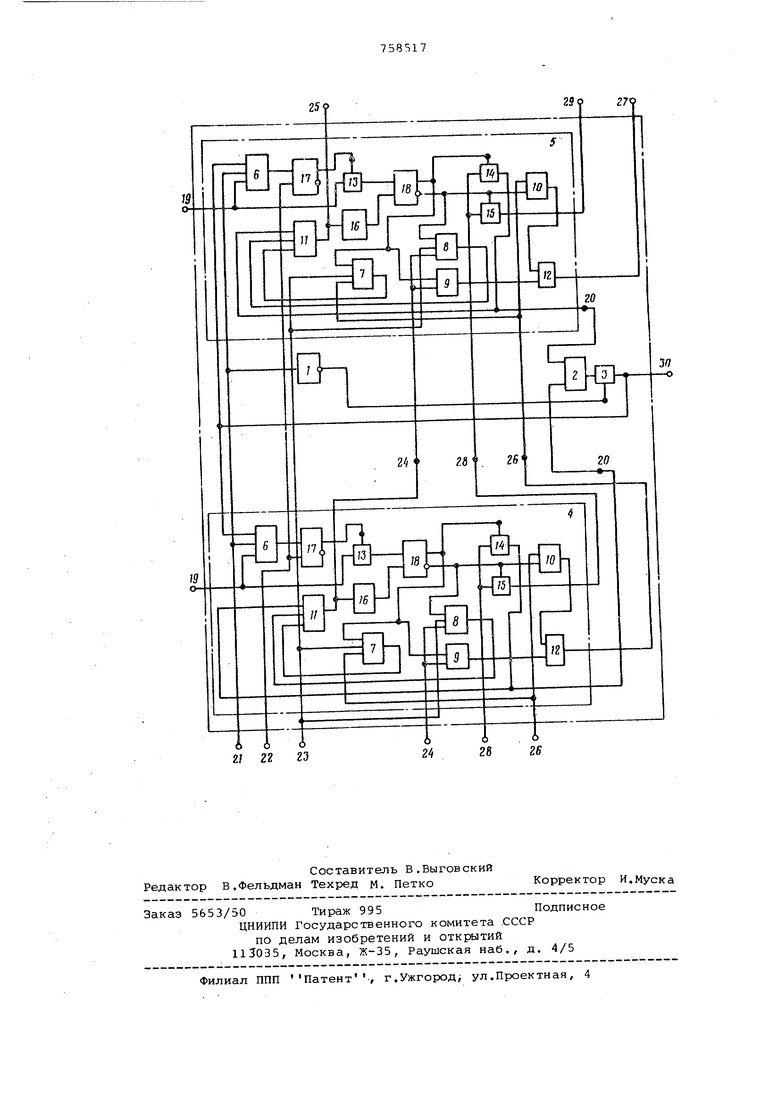

На чертеже представлена принципиальная электрическая схема электронного искателя-счетчика многоканального, выполненная согласно данному изобретению.

Электронный искатель-счетчик многоканальный содержит элемент НЕ-1, элемент ИЛИ 2,ключ 3, коммутационные блоки 4,5, каждый из которых состоит из элементов И 6-10,- элементов ИЛИ 11-12, ключей 13-15, элемента задержки 16,. триггеров 17, 18, входную информационную шину 19 выходную информационнул шину 20; шины управления-- шину сборки 21, шину сброса

22, шину разрешения суммирования 23, шину формирования единичного значения суммы приращений 24, выходную шину формирования единичного значения суммы приращений 25, шину формирования 5 нулевого значения суммы приращений 26, выходную шину формирования нулевого значения суммы приращений 27, шину считывания приращений 28, выходную шину считывания приращений 29 и Q выходную информационную шину устройства 30.

Электронный искатель-счетчик многоканальный может быть расширен за счет последовательного подключения п-коммутационных блоков,

5Работает электронный искатель-счетчик многоканальный следующим образом.

В первом такте производится сброс в нулевое состояние триггеров 17 и 18 каждого коммутационного блока 4, 5. 0 Для- этого на шину 22 сброса и шину 28 считывания приращений подаются единичные сигналы. Первый из них непосредственно поступает на нулевые входы триггеров 17 и устанавливает их в нулевое 5 состояние, второй же поступает на объединенные сигнальные входы ключей 14 и 15 коммутационного блока 4. Если в триггере 18 коммутационного блока 4 была записана единица, то открыт ключ Q 14, через КОТОЕМЙ сигнал поступает на элемент ИЛИ 11. С выхода данного элемента сигнал пройдет через элемент задержки 16 на нулевой вход триггера 18. С этого момента прог изойдет сброс триггера 18 коммутационного блока 4 в нулевое состояние. После Сброса триггера 18 в нулевое состояние открюется ключ 15, а ключ 14 окажется закрытымi С выхо;да ключа 15 сигнал поступает на 0 объединенные сигнальные входы ключей 14 и 15 следующего коммутационного блока 5. Процесс повторяется, пока триггеры 17 и 18 всех коммутационных блоков не установятся в нулевое 5 состояние и на выходной шине считывания приращений 29 не появится импульс .

Во втором такте осуществляется запись единиц в триггеры 17 выQ бранных коммутационных блоков.

Выборка производится путем подачи единичных сигналов на входные информационные шины 19 соответствующих коммутационных блоков 4, 5 и шину f сборки 21. в результате на выходе

элемента И б выбранного коммутацион. ного блока появится сигнал,устанавливающий триггер 17в единичное состояние.

В третьем такте информационные 0 сигналы, поступающие на входные.информационные шины 19 коммутационных блоков 4, будут записаны в триггер 8 только выбранньЕс коммутационных блоков 4, Это объясняется тем, что 5 S данных ко1Л 1утационных блоках 4 7 ириггерах 17 записаны единицы и поэтому открыты ключи 13. Через от крытые ключи 13 единичные сигнапы с информационных входов 19 будут записаны в триггеры 18 выбранных коммутационных блоков 4. В четвертом такте формируется сумма прираигений,, записанных в соответствующих триггерах 18 коммутационных блоков 4. Для этого на шину разрешения суммирования 23 подается разрешающий потенциал, На входную шину формирования нулевого значения суммы приращений 26 и входную шину считывания приращений 28 подаются импульсы, длительность которых не должна превышать время задержки злемента задержки 16. Количество этих импульсов будет зависеть от информации, записанной в триггерах. 18 ком мутационных блоков 4, и равнЬ (1+ + К) число единичных пр ращений, хранящихся в триггерах- 18 к мутационных блоков 4. Предположим,что в единичном состо янии находятся триггеры 18 первого и последнего коммутационных блоков 4, 5. Тогда в коммутационном блоке 4 сигнал с шини 28 считывания приращений пройдет через открытый ключ 14 и через элемент ИЛИ 11 поступит на вход элемента И 8 второго коммута-. ционного блока 5. Через элемент И 8 и элемент ИЛИ 11 сигнал поступит на вход элемента И 8 следующего коммута ционного блока. Аналогично сигнал будет проходить во всех коммутационных блоках, причем последнего. В последнем коммутационном блоке сигнал через элемент И 9 и элемент ИЛИ 12 поступает на входную шину формиро вания нулевого значения суммы приращений 27. Появление единичного сигнала на этом выходе будет говорить о формировании нуля в младшем разряде сум.мы, В момент появления сигна ла на выходе элемента задержки 16 коммутационного блока 4 произойдет сброс триггера 18 в нулевое состояние и на этом закончится выполнение первого шага суммирования едини ных приращений. На втором шаге суммирования единич ных приращений вновь, как и в первом шаге, подаются сигналы на шину 28 сч тывания приращений и на шину 26 фо мирования нулевых значений суммы пр ращений коммутационного блока 4. Те перь в коммутационном блоке 4 данны сигналы появятся на выходе ключа 15 и на выходе элемента ИЛИ 12, пройдя при этом через элемент И 10. Аналогично данные сигналы пройдут и чере остальные коьмутационкые блоки 4, 5 кроме последнего. В последнем комму тационном блоке будет открыт ключ 1 так как на управляющем входе присут ствует единичный сигнал с единичног выхода триггера 18. Поэтому сигнал пройдет в последнем коммутационном блоке через открытый ключ 14, элемент ИЛИ 11 на выход 25 формирования единичного значения суммы приращений. Таким образом, второй разряд суммы будет равен единице. Когда появится сигнал на выходе элемента задержки 16 последнего коммутационного блока 4, произойдет сброс триггера 18 в нулевое состояние. С этого момента закончится выполнение второго шага, а появление сигнала на выходе 29 считывания приращений последнего коммутационного блока будет указывать об окончании выполнения суммирования. Данное устройство позволяет также считывать на выходную информационную шину 30 только единичное приращения, которые хранятся в триггерах 18 коммутационных блоков. Для этого на входную шину считывания приращений 28 подается сигнал, длительность которого равна времени задержки на элементе задержки 16 одного коммутационного блока 4. Данный сигнал в коммутационном блоке пройдет через открытый ключ 14 и поступит через элемент ИЛИ 2, открытый ключ 3 на информационный выход 30. Одновременно с этим этот же сигнал пройдет через элемент ИЛИ 11 и элемент задержки 16 на нулевой вход триггера 18 ксглмутационного блока 4 и перебросит его в нулевое состояние. С этого момента закроется ключ 14 и сигнал на информационном выходе 30 станет нулевым, т.е. закончится считывание первого единичного приращения. При подаче второго сигнала на шину 28 считывания приращений в коммутационном блоке 4 будет открыт ключ 15 и поэтому сигнал с него сразу же поступит на входы ключей 14 и 15 и поэтому сигнал с него сразу же посту-пит. на входы ключей 14 и 15 коммутационного блока. Аналогичным образом сигнал пройдет через остальные коммутационные блоки, кроме последнего. В последнем коммутационном блоке произойдет считывание единичного приращения так же, как и в коммутационном блоке 4. В момент появления единичного сигнала на выходе 29 считывания приращений прекращается подача сигналов на шину 28 считывания приращений и тем самым заканчивается считывание. Формула изобретения Электронный искатель-счетчик многоканальный, содержащий ключ,управляющий вход которого соединен с выходом элемента НЕ, вход которого подключен к первой входной шине управления, выход ключа соединен с информационной выходной шиной устройства, а сигнальный вход ключа соединен с выходом элемента ИЛИ, входы которого подключены к инФормационным выходным шинам двух коммутационных е5локов, каждый из которы состоит из первого, элемента И, первый вход которого соединен с информационной входной шиной и с сигнальным входом первого ключа, второй вхо первого элемента И соединен с первой входной шиной управления, третий вход - с информационной выходной шиной устройства, а выход первого элемента И - с единичным входом первого триггера, нулевой вход которого соединен со второй входной шиной управления, прямой выход первого триггера соединен с управляющим входом первого ключа, выход которого со единен с единичным входом второго триггера, нулевой вход которого подключен к выходу элемента задержки, прямой выход второго триггера подключен к управляющему входу второго ключа, выход которого соединен с информационной выходной шиной коммутационного блока, инверсный выход второго триггера подключен к управляющему входу третьего ключа, сигнальные входы второго и третьего ключей первого коммутационного блока соединены с третьей входной шиной управления , а второго - с выходом третьего ключа первого коммутационного блока, четвертую, пятую и шестую входные

шины управления, отличающийся тем, что, с целью повышения быстродействия формирования сукну приращений, в каждый из коммутационных блоков дополнительно введены четыре элемента И и два элемента ИЛИ, причем входы первого элемента ИЛИ соединены с выходом второго ключа и выходами второго и третьего элеме.нтов И, выход первого элемента ИЛИ первого коммутационного блока соединен

с первыми входами второго и четвертого элементов И второго коммутационного блока, выход первого элемента ИЛИ второго коммутационного блока соединен с первой выходной шиной управления, второй вход второго элемента И подключен к инверсному выходу второго триггера и к первому входу пятого элемента И, третий вход второго элемента И - к первому входу третьего элемента И и к четвертой входной шине управления, выход первого элемента ИЛИ соединен с входом элемента задержки, второй вход третьего элемента И подключен к прямому выходу второго триггера и к второму входу четвертого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу пятого элемента И, выход второго элемента ИЛИ первого коммутационного блока подключен ко второму входу пятого элемента И и к третьему входу третьего элемента И второго коммутационного блока, выход второго элемента ИЛИ второго коммутационного блока подключен ко второй выходной шине управления, первые входы второго и четвертого элементов И первого ког«мутационного блока подключены к пятой входной шине управления второй вход пятого элемента И и третий вход третьего элемента И первого коммутационного блока подключены к шестой входной шине управления, выход третьего ключа второго коммутационного блока подключен к третьей выходной шине управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 499665, кл. Н 03 К 17/04, 1974 (прототип) .

о о О 2/ 22 23

2428гВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Электронный искатель-разъединитель | 1981 |

|

SU961141A1 |

| Коммутатор | 1977 |

|

SU738162A1 |

| Электронный искатель-разъединитель | 1979 |

|

SU849487A1 |

| Электронный искатель-разъединитель | 1974 |

|

SU499665A1 |

| Генератор многомерных случайных процессов | 1990 |

|

SU1755279A1 |

| Анализатор экстремумов | 1984 |

|

SU1233173A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2020 |

|

RU2726497C1 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2015 |

|

RU2616153C2 |

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 2001 |

|

RU2199774C1 |

Авторы

Даты

1980-08-23—Публикация

1974-08-02—Подача