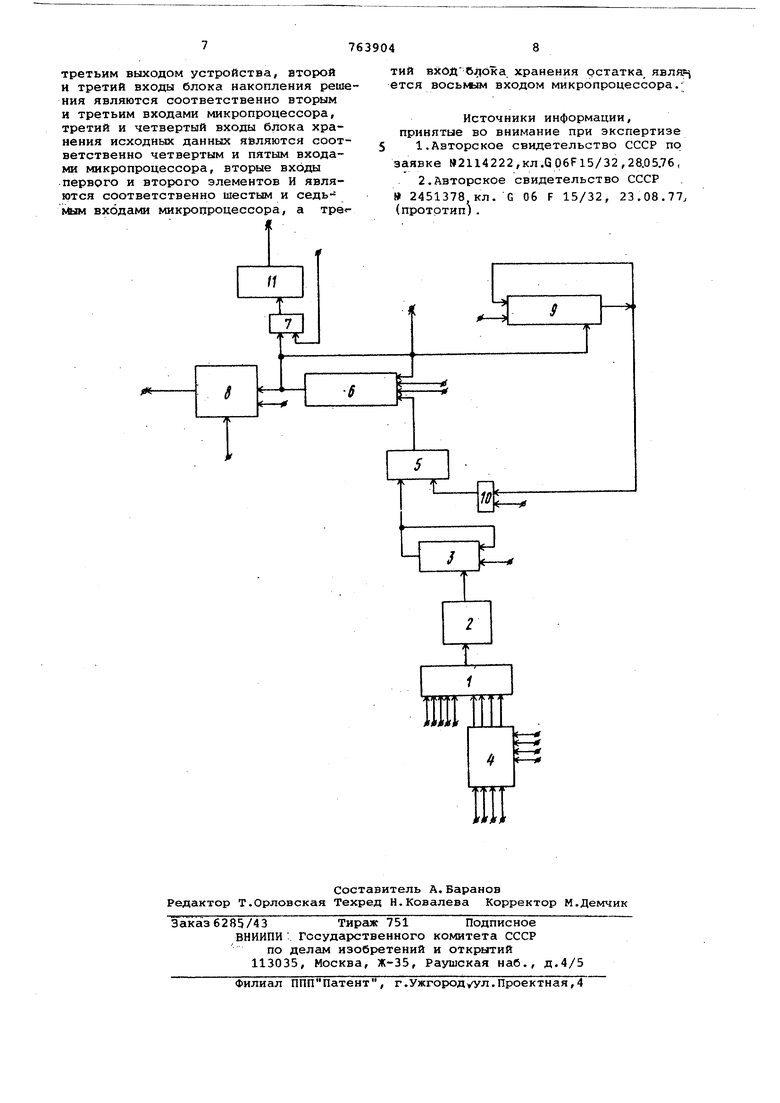

Изобретение относится к области вычислительной техники и может быть использовано при построении устройст для решения задачи Дирихле многомерных эллиптических и параболических уравнений математической физики с реализацией различных вычислительных шаблонов и сеток. Известно устройство, содержащее многовходовый одноразрядный комбинационный сумматор последовательного типа с элементами для запоминания переносов на один или различное число тактов, регистр сдвига, регист функции, группы входных,-выходных и управляющих шин 1 .. Недостатком его является большое количество оборудования, которое рас ходуется на построение комбинационных сумматоров и триггеров ,для запоминания значений результата и пере носа для каждого комбинационного сум матора. Для построения вычислительного узла, предназначенного для решения трехмерного уравнения Пуассона требуется не менее шести трехвходовых сумматоров и 12 элементов памяти (триггеров) для запоминания перено сов и результатов. Устройство имеет область применения, что обусловлено ориентацией на уравнения Лапласа и Пуассона, и используется для построения только двумерных цифровых сеток. Наиболее близким техническим решением к предложенному является сеточный микропроцессор, состоящий из мультйпликсора, счетчика с промежуточным регистром, регистра сдвига результата и коммутатора значений результата илизначения суммы, зафиксированной в текущем микротакте в младшем разряде счетчика 2 . К недостаткам такого сеточного микропроцессора следует отнести ограниченные функциональные возможности, поскольку он решает только задачи с единичными коэффициентами при старших производных, малое быстродействие, поскольку операция умножения, реализуемая устройством, выполняется за время, гораздо большее, чем операция типа однократного суммирования с одним или несколькими операциями сдвига, а также усложненная структура для выполнения операции умножения. Кроме того, устройство не может решать уравнения с переменными коэффициентами, . Цель изобретения - расширение функциональньж возможностей и повы-г шение быстродействия устройства. Эта цел, достигается тем, что в устройство, содержащее мультиплексо суммирующий блок, узел сдвига, при этом первые входы мультиплексора являются первой группой входов микропроцессора, а выход мультиплексора соединен со входом суммирующего блока, выход которогоподключен к перво му входу узла сдвига ,второй вход которого является первым входом микропроцессора, а выход узла сдвига подключен к его третьему входу, согласно изобретению, введены сумматор, блок накопления решения, блок хранения исходных данных, блок хранения остатка, два элемента И, триггер приращения и блок хранения коэффициентов. Первая и вторая группа входов блока хранения коэффициентов является соответственно второй и ,третьей группой микропроцессора, . а выходы блока хранения коэффициентов подключены соответственно ко вторым входам мультиплексора. Выход ,узла сдвига соединен с первым входом сумматора, выход которого подключен к первому входу блока хранения исходных данных, выход которого является первым выходом устройства и подключен к вто рому входу этого блока и первым входам блока накопления решения, блока хранения остатка первого элемента И выход которого подключен к входу триггера приращений, выход которого является вторымвыходом устройства, Выход блока хранения остатка соединен с его вторым входом и подключен к первому входу второго элемента И, выход которого соединен со вторым входом сумматора, выход блока накопления решения является третьим выходом устройства, второй и третий входы блока накопления решения явля ются соответственно вторым и треть входами микропроцессора, третий и четвертый входы блока хранения исходных данных являются соответствен но четвертым и пятым входами микропроцессора, вторые входы первого и второго элементов И являются соотве ственно шестым и седьмым входами микропроцессора, а третий вход блока хранения остатка является ВОСЬМЕЛ входом микропроцессора. Предлагаемое устройство реализуе новый метод приращений (или инкреме ный метод), который позволяет избежать традиционных для таких задач операций умножения классическим пут сведя все к арифметической операции суммирования коэффициентов с одним или несколькими операциями сдвига п лученного кода с выделением и накоп лением выделенных приргицений. Схема предлагаемого сеточного микропроцессора приведена на чертеже . Она содержит мультиплексор 1, суммирукяций блок 2, узел сдвига 3, блок 4 хранения коэффициентов, сумматор 5, узел б хранения исходных данных, первый элемент и 7, блок 8 накопления решения, блок 9 хранения остатка, второй элемент И 10, триггер приращения 11. Сеточный микропроцессор может быть применен в качестве внутреннего узла при решении задач математической физики. Устройство работает следующим образом . При подготовке устройства к работе в блок 4 хранения коэффициентов через информационные входы вводят в цифровой форме значения соответст вующих коэффициентов. Сигналы управления блока 4 хранения коэффициентов подключены к выходам триггеров приращения 11 соответствующих соседних сеточных микропроцессоров. Таким обраэом, если соседний с рассматриваемым микропроцессор в предыдущей итерации выделил приращение (т.е.старший разряд) , то в текущей итерации выходной.сигнал триггера приращения, поступивший на управляющий вход блока хранения коэффициентов, разрешит подключение ко входу мультиплексора 1 (через одну иэ шин второй группы информационных шин мультиплексора) в момент развертки соответствующего адреса мультиплексора. Если в предыдущей итерации, например, были выде лены приращения во всех соседних микропроцессорах, то все четыре коэффициента будут введены через мультиплексор на вход суммирующего блока 2 в текущей итерации.Сложение коэффициентов может осуществляться последовательным, параллельным, последовательно-параллельным способами. В итоге с помощью суммирующего блока 2промежуточного результата будет получена и запомнена в узле сдвига 3сумма коэффициентов. Для определенности будем считать в дальнейшем, что операции выполняются над числами в последовательном коде, форма представления - фиксированная запятая перед старшим слева значащим разрядом после знакового, а обработка чисел в суммирующем блоке и сумматоре - начиная с младшего. Тогда код полученного значения последовательно, начиная с младшего, будет поступать на Тпервый вход сумматора 5, на второй вход которого через второй элемент И 10, выполняющий роль вентиля, на сигнале управления, также младшими разрядами вперед, будет поступать код блока 9 хранения остатка. Результатом сложения будет число, выполнякнаее роль новых исходных данных для следующей

итерации, которое будет записано из сумматора в блок б хранения исходньк данных на соответствующем сигнале управления. Затем полученный код сдвигают уже старшими разрядами вперед. Первоначальный сдвиг начинают с самого старшего разряда, а последующие - начиная с того разряда, в котором в предьадущей итерации был выделен старший разряд отличный от нулевого значения. Наличие сигнала управления на втором входе первого элемента И свидетельствуе о в 4делении соответствующего приращения во всем устройстве на данном микротакте, соответствующем, например, сдвигу t-ro разряда,фиксирует состояние текущего разряда исходных данных рассматриваемого сеточного микропроцессора. Номер позиции выделенного разряда фиксируется в целом по устройству и он определяет количество (ti) разрядов, на которое необходимо один раз сдвинуть в сторону младшего разряда код суммы, полученной на следующей микроитерации в суммирующем блоке 2, и записанный в узел сдвига 3. Наличие же старшего разряда- в данном сеточном микропроцессоре фиксируется триггером приращения 11. Далее поскольку выход блока хранения исходных данных одновременно заведен и на информационный вход блока накопления решения, то выделенное приращение весом 2 должно быть просуммировано с ранее полученными приращениями в данном блоке. Полученная сумма приращений

. I

г д ,. , выделяемых в данном микрК

процессоре на каждой микроитерации, взятых каждый раз со своим весом, определенным номером позиции в кодовой последовательности, и является накопленным решением в данном сеточ«ом узле, или сеточной функцией, полученной каждый раз уточнением предьщущего значения на величину вьщеленного старшего разряда в текущей итерации. Код в блоке 6 хранения исходных данных, оставшихся после выделения старшего разряда, является кодом остатка. Он переписывается в блок 9 хранения остатка, из которого на следующей итерации путем сдвига (но.уже младшими разрядами вперед) будет скоммутирован на вход сумматора 5 через первый вход первого элемента И. Далее код остатка будет сложен с кодом прюмежуточного результата, полученным на ( +1)-ой микроитерации, который равен сумме коэффициентов, соответствующих тем сеточным микропроцессорам, в которых на С-ой микроитерации был выделен старший разряд, сдвинутый на разрядов в сторону младшего , и т.л.

Таким образом, данный сеточный микропроцессор обеспечивает вычисление узловой функции, которая в итоге слагается из суммы приращений (или старших разрядов,выделенных на каждой микроитерацин из исходных данных. Отсюда и название метода : метод прира;цений.

Технико-экономический эффект данного изобретения по сравнению с известным заключается в расширении функциональных возможностей за счет решения уравнений с переменными коэффициентами, в повышении быстродействия устройства за счет замены операции умножения операцией сложения 5 коэффициентов и разового сдвига полученного таким образом кода, в простой аппаратурной реализации устройства.

20

изобретения

Формула

Сеточный микропроцессор, содержащий мультиплексор, суммирующий блок, узел сдвига, при этом первые входы

25 мультиплексора являются первой группой входов миkpoпpoцedcopa, а выход мультиплексора соединен со входом суммирующего блока, выход которого подключен к первому входу узла сдви0га, второй вход которого является первым входом микропроцессора, а выход узла сдвига подключен к его третьему входу, отличающийся тем, что, с целью повыше5ния быстродействия и расширения функциональных возможностей микропроцессора за счет решения уравнений с переменными коэффициентами, в него введены cyм 1aтop, блок накопления решения, блок хранения исходных дан0ных, блок хранения остатка, два элемента И, триггер приращения и блок хранения коэффициентов, первая и вторая группа входов которого является соответственно второй и третьей

5 группой входов микропроцессора, а выходы блока хранения коэффициентов подключены соЬтветственно ко вторым входам мультиплексора, выход узла сдвига соединен с первым входом сум0матора, выход которого подключен к первому входу блока хранения исходных данных, выход которого является первым выходом устройства и подключен к второму входу этого блока и пер5вым входам блока накопления решения, блока хранения остатка первого элемента И, выход которого подключен к входу триггера приращений, выход которого является вторым выходом устройства, выход блока хранения остат0ка соединен с его вторым входом и подключен к первому входу второго элемента И, выход которого соединен со вторым входом сумматора, выход блока накопления решения является

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел для однородной вычислительной системы | 1979 |

|

SU982008A1 |

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

| Узловой процессор | 1986 |

|

SU1399763A1 |

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| Вычислительный узел цифровойСЕТОчНОй МОдЕли для РЕшЕНия диффЕРЕН-циАльНыХ уРАВНЕНий B чАСТНыХ пРОизВОд-НыХ | 1978 |

|

SU798858A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Устройство для отображения информации | 1981 |

|

SU1005171A1 |

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1978 |

|

SU798862A1 |

Авторы

Даты

1980-09-15—Публикация

1978-06-14—Подача