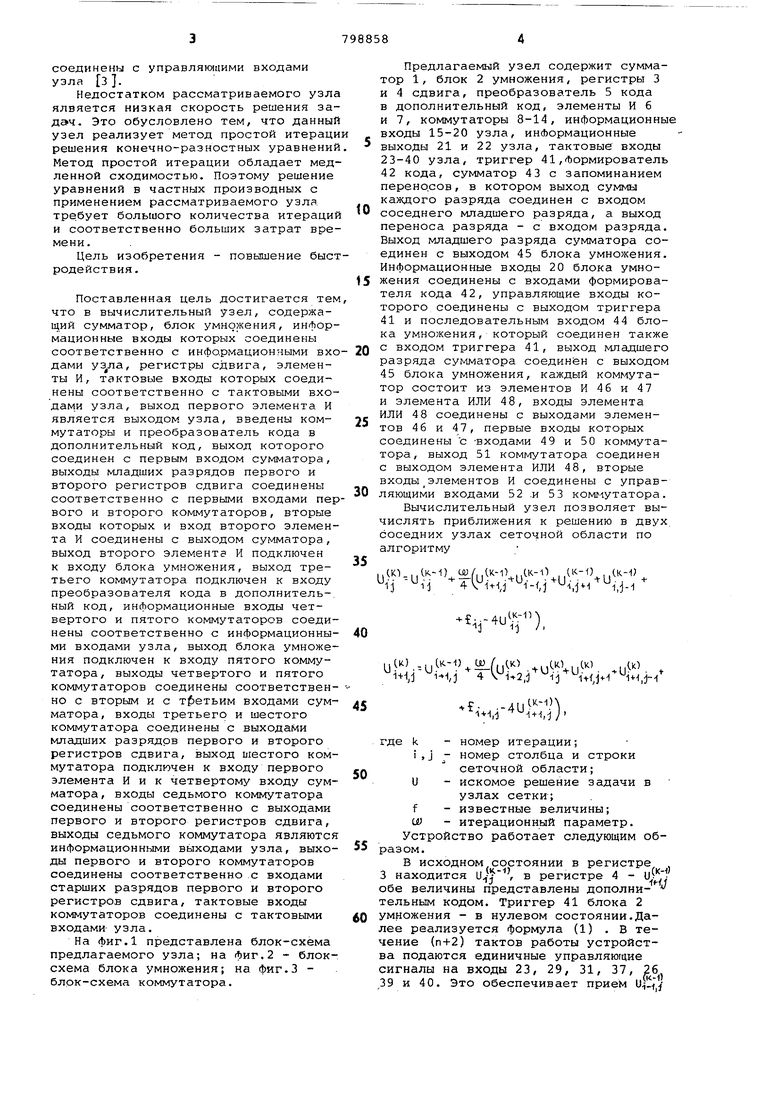

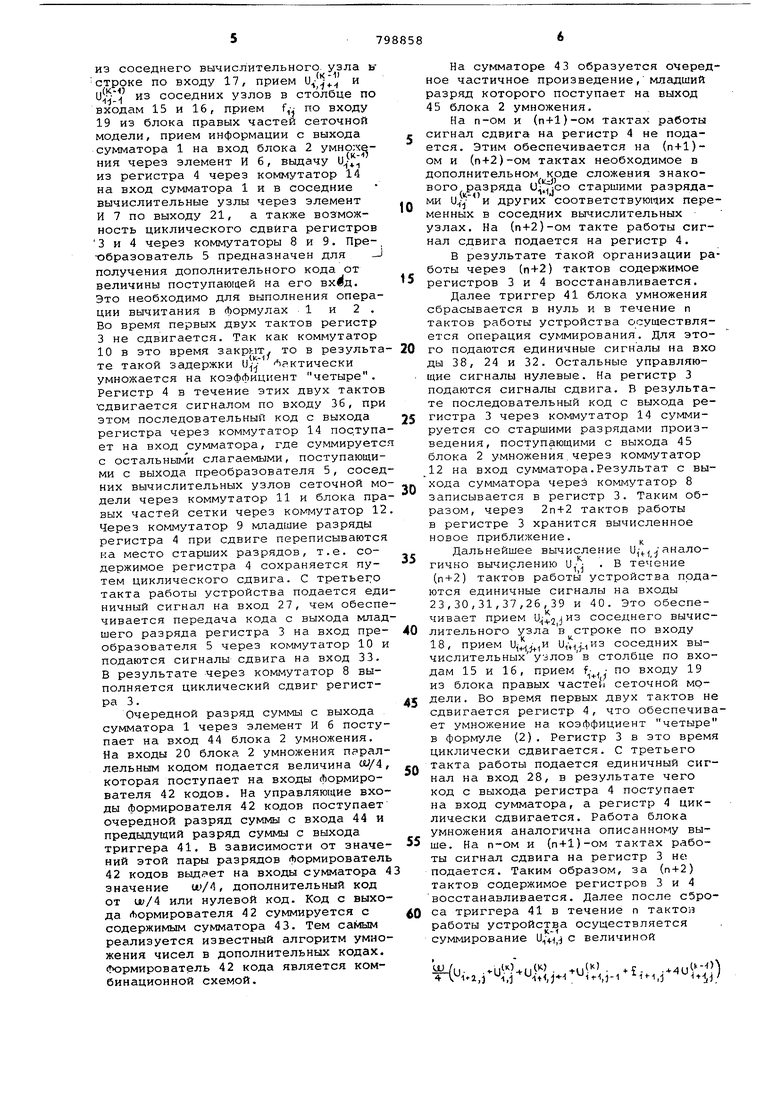

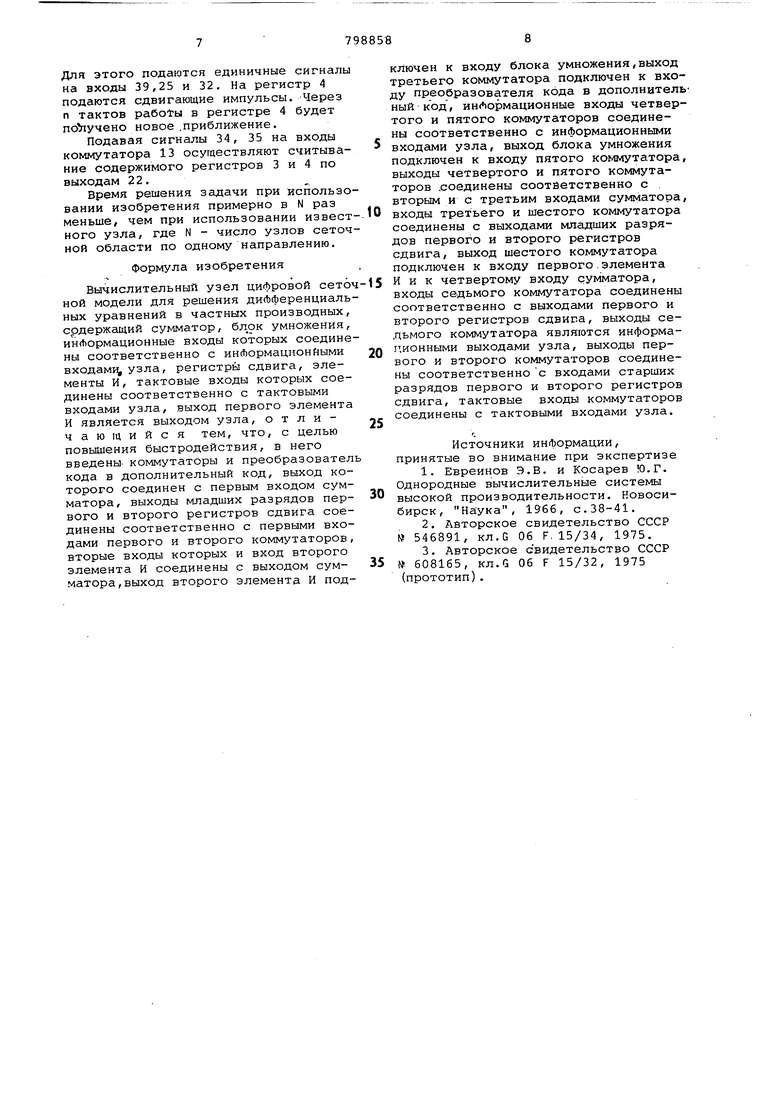

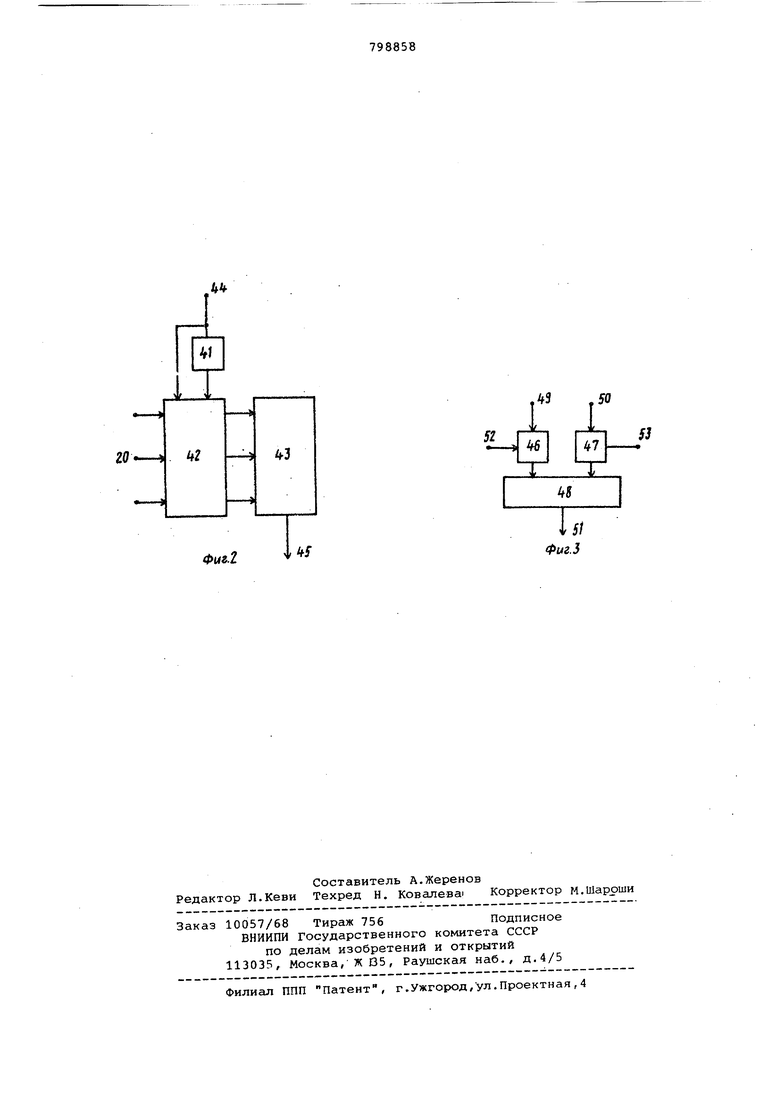

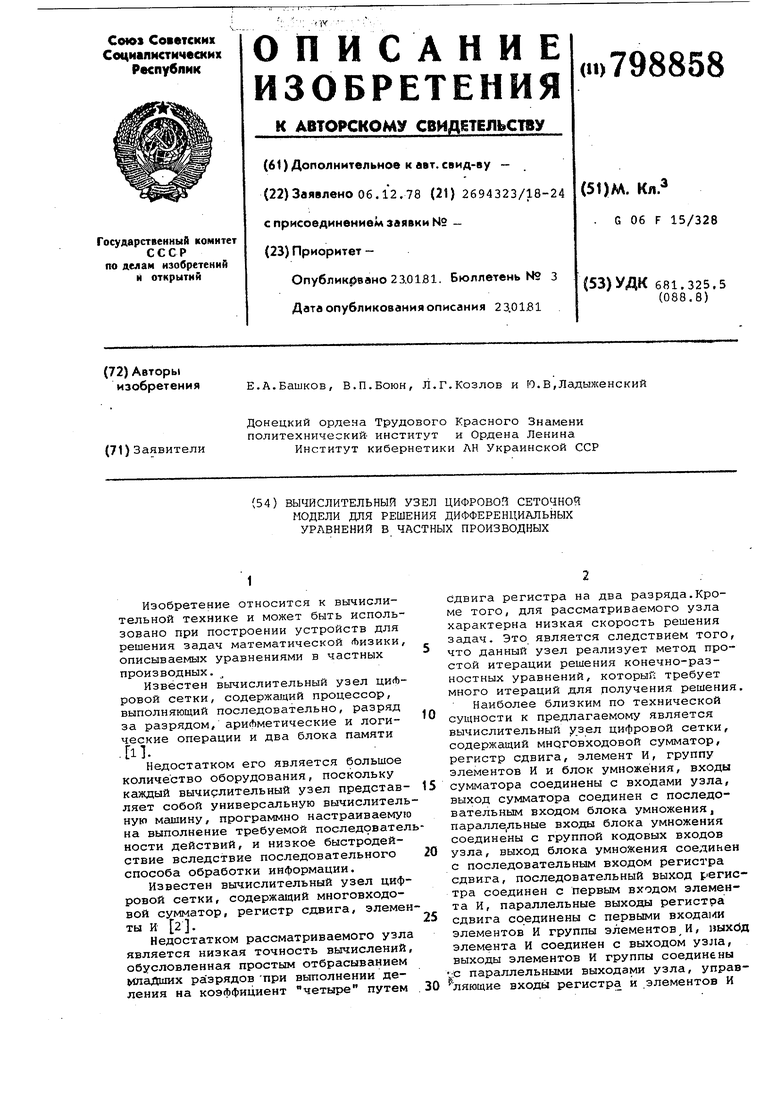

Изобретение относится к вычислительной технике и может быть использовано при построении устройств для решения задач математической гЪизики, oпиcывae /IЫX уравнениями в частных производных. Известен вычислительный узел циЛровой сетки, содержащий процессор, выполняющий последовательно, разряд за разрядом, арифметические и логические операции и два блока памяти Недостатком его является большое количество оборудования, поскольку каждый вычислительный узел представляет собой универсальную вычислитель ную машину, программно настраиваемую на выполнение требуемой последовател ности действий, и низкое быстродействие вследствие последовательного способа обработки информации. Известен вычислительный узел циф ровой сетки, содержащий многовходовой сумматор, регистр сдвига, элеме ты И 2. Недостатком рассматриваемого узл является низкая точность вычислений обусловленная простым отбрасыванием младших разрядов при выполнении деления на коэффициент четыре путем сдвига регистра на два разряда.Кроме того, для рассматриваемого узла характерна низкая скорость решения задач. Это является следствием того, что данный узел реализует метод простой итерации решения конечно-разностных уравнений, который требует много итераций для получения решения. Наиболее близким по технической сущности к предлагаемому является вычислительный узел цифровой сетки, содержащий многовходовой сумматор, регистр сдвига, элемент И, группу элементов И и блок умножения, входы сумматора соединены с входами узла, выход сумматора соединен с последовательным входом блока умножения, параллельные входы блока умножения соединены с группой кодовых входов узла, выход блока умножения соединен с последовательным входом регистра сдвига, последовательный выход регистра соединен с первым входом элемента И, параллельные выходы регистра сдвига соединены с первыми входа1«1И элементов И группы элементов,И, иыхбд элемента И соединен с выходом узла, выходы элементов И группы соединены ;С параллельными выходами узла, управляющие входы регистра и элементов И соединены с управляющими входами узла З. Недостатком рассматриваемого узл ялвяется низкая скорость решения за дач. Это обусловлено тем, что данный узел реализует метод простой итераци решения конечно-разностных уравнени Метод простой итерации обладает мед ленной сходимостью. Поэтому решение уравнений в частных производных с применением рассматриваемого узла тре.бует большого количества итераци и соответственно больших затрат вре мени. Цель изобретения - повышение быс родействия. Поставленная цель достигается тем что в вычислительный узел, содержащий сумматор, блок умножения, инфор мационные входы которых соединены соответственно с информационными вхо дами , регистры сдвига, элементы И, тактовые входы которых соединены соответственно с тактовыми входами узла, выход первого элемента И является выходом узла, введены коммутаторы и преобразователь кода в дополнительный код, выход которого соединен с первым входом сумматора, выходы младших разрядов первого и второго регистров сдвига соединены соответственно с первыми входами пер вого и второго коммутаторов, вторые входы которых и вход второго элемента И соединены с выходом сумматора, выход второго элементе И подключен к входу блока умножения, выход третьего коммутатора подключен к входу преобразователя кода в дополнительный код, информационные входы четвертого и пятого коммутаторов соединены соответственно с информационными входами узла, выход блока умножения подключен к входу пятого коммутатора, выходы четвертого и пятого коммутаторов соединены соответственно с вторым и с т |етьим входами сумматора, входы третьего и шестого коммутатора соединены с выходами младших разрядов первого и второго регистров сдвига, выход шестого коммутатора подключен к входу первого элемента И и к четвертому входу сумматора , входы седьмого коммутатора соединены соответственно с выходами первого и второго регистров сдвига, выходы седьмого коммутатора являются информационными выходами узла, выходы первого и второго коммутаторов соединены соответственно с входами старших разрядов первого и второго регистров сдвига, тактовые входы коммутаторов соединены с тактовыми входами- узла. На фиг.1 представлена блок-схема предлагаемого узла; на Фиг.2 - блоксхема блока умножения; на фиг.З блок-схема коммутатора. Предлагаемый узел содержит сумматор 1, блок 2 умножения, регистры 3 и 4 сдвига, преобразователь 5 кода в дополнительный код, элементы И б и 7, коммутаторы 8-14, информационные входы 15-20 узла, информационные выходы 21 и 22 узла, тактовые входы 23-40 узла, триггер 41 ,Ьормирователь 42 кода, сумматор 43 с запоминанием перено.сов, в котором выход каждого разряда соединен с входом соседнего младшего разряда, а выход переноса разряда - с входом разряда. Выход младшего разряда сумматора соединен с выходом 45 блока умножения. Информационные входы 20 блока умножения соединены с входами формирователя кода 42, управляющие входы которого соединены с выходом триггера 41 и последовательным входом 44 блока умножения, который соединен также с входом триггера 41, выход младшего разряда сумматора соединён с выходом 45 блока умножения, каждый кoм тaтор состоит из элементов И 46 и 47 и элемента ИЛИ 48, входы элемента ИЛИ 48 соединены с выходами элементов 46 и 47, первые входы которых соединены с -входами 49 и 50 коммутатора, выход 51 коммутатора соединен с выходом элемента ИЛИ 48, вторые входы элементов И соединены с управляющими входами 52 .и 53 коммутатора. Вычислительный узел позволяет вычислять приближения к решению в двух соседних узлах сеточной области по алгоритму U)/. Лк-1) ..(.. ,,( ,(.и).с. ,, -v). .Ч t 1П1 4 1+ди iH,:)--i V 1-2,J -ij . -номер итерации; -номер столбца и строки сеточной области; -искомое решение задачи в узлах сетки; -известные величины; -итерационный параметр. Устройство работает следующим образом. В исходном состоянии в регистре 3 находится , в регистре 4 - обе величины представлены дополнительным кодом. Триггер 41 блока 2 умножения - в нулевом состоянии.Далее реализуется формула (1) . В течение (п+2) тактов работы устройства подаются единичные управляющие сигналы на входы 23, 29, 31, 37, 26 ,39 и 40. Это обеспечивает прием

из соседнего вычислительного, узла н строке по входу 17, прием и и, из соседних узлов в столбце по входам 15 и 16, прием f,-; по входу 19 из блока правых частей сеточной модели, прием информации с выхода сумматора 1 на вход блока 2 умноления через элемент И б, выдачу из регистра 4 через коммутатор 14 на вход сумматора 1 и в соседние вычислительные узлы через элемент И 7 по выходу 21, а также возможность циклического сдвига регистров 3 и 4 через коммутаторы 8 и 9, Преобразователь 5 предназначен для J получения дополнительного кода от величины поступающей на его . Это необходимо для выполнения операции вычитания в формулах 1 и 2 . Во время первых двух тактов регистр 3 не сдвигается. Так как коммутатор 10 в это время закрыт, то в результате такой задержки (i -тактически умножается на коэффициент четыре. Регистр 4 в течение этих двух тактов сдвигается сигналом по входу 36, при этом последовательный код с выхода регистра через коммутатор 14 пос.тупает на вход сумматора, где суммируетс с остальными слагаемыми, поступающими с выхода преобразователя 5, соседних вычислительных узлов сеточной модели через коммутатор 11 и блока правых частей сетки через коммутатор 12 Через коммутатор 9 младшие разряды регистра 4 при сдвиге переписываются на место старших разрядов, т.е. содержимое регистра 4 сохраняется путем циклического сдвига. С третье1:о такта работы устройства подается единичный сигнал на вход 27, чем обеспечивается передача кода с выхода младшего разряда регистра 3 на вход преобразователя 5 через коммутатор 10 и подаются сигналы сдвига на вход 33. В результате через коммутатор 8 выполняется циклический сдвиг регистра 3.

Очередной разряд суммы с выхода сумматора 1 через элемент И б поступает на вход 44 блока 2 умножения. На входы 20 блока 2 умножения параллельным кодом подается величина cw/4, которая поступает на входы формирователя 42 кодов. На управляющие входы формирователя 42 кодов поступает очередной разряд суммы с входа 44 и предыдущий разряд суммы с выхода триггера 41. В зависимости от значений этой пары разрядов формирователь 42 кодов выдает на входы сумматора 4 значение и.|/4, дополнительный код от ш/4 или нулевой код. Код с выхода (Формирователя 42 суммируется с содержимым сумматора 43. Тем самым реализуется известный алгоритм умножения чисел в дополнительных кодах. (Формирователь 42 кода является комбинационной схемой.

На сумматоре 43 образуется очередное частичное произведение,младший разряд которого поступает на выход 45 блока 2 умножения.

На п-ом и (п+1)-ом тактах работы J сигнал сдвига на регистр 4 не подается. Этим обеспечивается на (п+1)ом и (п+2)-ом тактах необходимое в дополнительном коде сложения знакового разряда старшими разрядаQ ми ,j- и других соответствующих переменных в соседних вычислительных узлах. На (п+2)-ом такте работы сигнал сдвига подается на регистр 4.

В результате такой организации работы через (п+2) тактов содержимое

5 регистров 3 и 4 восстанавливается.

Далее триггер 41 блока умножения сбрасывается в нуль и в течение п тактов работы устройства осуществляется операция суммирования. Для этого подаются единичные сигналы на вхо

ды 38, 24 и 32. Остальные управляющие сигналы нулевые. На регистр 3 подаются сигналы сдвига. В результате последовательный код с выхода регистра 3 через коммутатор 14 суммируется со старшими разрядами произведения, поступающими с выхода 45 блока 2 умножения,через коммутатор 12 на вход сумматора.Результат с выхода сумматора через коммутатор 8

0 записывается в регистр 3. Таким образом, через 2п+2 тактов работы в регистре 3 хранится вычисленное новое приближение.

- Дальнейшее вычисление U,,. .(аналогично вычислению иЛ . В течение (п+2) тактов работы устройства подаются единичные сигналы на входы 23,30,31,37,26,39 и 40. Это обеспечивает прием j из соседнего вычислительного узла в строке по входу

0 18, прием ..и UiH.j.iH3 соседних вычислительныхузлов в столбце по входам 15 и 16, прием по входу 19 из блока правых частей сеточной мр5 дели. Во время первых двух тактов не сдвигается регистр 4, что обеспечивает умножение на коэффициент четыре в формуле (2). Регистр 3 в это время циклически сдвигается. С третьего такта работы подается единичный сих-

0 нал на вход 2В, в результате чего код с выхода регистра 4 поступает на вход сумматора, а регистр 4 циклически сдвигается. Работа блока умножения аналогична описанному выше. На п-ом и (п+1)-ом тактах работы сигнал сдвига на регистр 3 не подается. Таким образом, за {п+2) тактов содержимое регистров 3 и 4 восстанавливается. Далее после сброса триггера 41 в течение п такто1з работы устройства осуществляется суммирование .i,-i величиной

. -hu f ii,3 i,j ,j .j-i iM.j i-nj/

Для этого подаются единичные сигналы на входы 39,25 и 32. На регистр 4 подаются сдвигающие импульсы. Через п тактов в регистре 4 будет по 1учено новое .приближение.

Подавая сигналы 34, 35 на входы коммутатора 13 осуществляют считывание содержимого регистров 3 и 4 по выходам 22.

Время решения задачи при использовании изобретения примерно в N раз меньше, чем при использовании извест ного узла, где N - число узлов сеточной области по одному направлению.

Формула изобретения

Вычислительный узел цифровой сет6ч ной модели для решения диЛференциальных уравнений в частных производных, содержащий сумматор, бл.ок умножения, информационные входы которых соединены соответственно с инЛормационйыми входам узла, регистры сдвига, элементы И, тактовые входы которых соединены соответственно с тактовыми входами узла, выход первого элемента И является выходом узла, о т л и чающийся тем, что, с целью повышения быстродействия, в него введены- коммутаторы и преобразователь кода в дополнительный код, выход которого соединен с первым входом сумматора, выходы младших разрядов первого и второго регистров сдвига соединены соответственно с первыми входами первого и второго коммутаторов, вторые входы которых и вход второго элемента И соединены с выходом сумматора,выход второго элемента И подключен к входу блока умножения,выход третьего коммутатора подключен к входу преобразователя кода в дополнител ный код , инЛормационные входы четвертого и пятого коммутаторов соединены соответственно с информационными входами узла, выход блока умножения подключен к входу пятого кo Iмyтaтopa выходы четвертого и пятого коммутаторов .соединены соответственно с . вторым и с третьим входами сумматора входы третьего и шестого коммутатора соединены с выходами младших разрядов первого и второго регистров сдвига, выход шестого коммутатора подключен к входу первого.элемента И и к четвертому входу сумматора, входы седьмого коммутатора соединены соответственно с выходами первого и второго регистров сдвига, выходы седьмого коммутатора являются информагионными выходами узла, выходы первого и второго коммутаторов соединены соответственно с входами старших разрядов первого и второго регистров сдвига, тактовые входы коммутаторов соединены с тактовыми входами узла.

Источники информации, принятые во внимание при экспертизе

1.Евреинов Э.В. и Косарев Ю.Г. Однородные вычислительные системы высокой производительности. Новосибирск, Наука, 1966, с.38-41.

2.Авторское свидетельство СССР № 546891, кл.С 06 F. 15/34, 1975.

3.Авторское свидетельство СССР № 608165, кл.а 06 F 15/32, 1975

(прототип).

е

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| Вычислительный узел цифровойСЕТКи | 1979 |

|

SU800997A1 |

| Вычислительный узел цифровой сеточ-НОй МОдЕли для РЕшЕНия диффЕРЕНциАль-НыХ уРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU840920A1 |

| Вычислительный узел для однородной вычислительной системы | 1979 |

|

SU982008A1 |

| Сеточный микропроцессор | 1978 |

|

SU763904A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1981 |

|

SU976448A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Вычислительный узел цифровой сеточной модели для решения дифференциальных уравнений в частных производных | 1980 |

|

SU894717A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1980 |

|

SU926667A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

kZ

го

43

4f

Фиг.2

К

5J

Авторы

Даты

1981-01-23—Публикация

1978-12-06—Подача